Устройство для сравнения чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 693367

Авторы: Полисский, Факторович

Текст

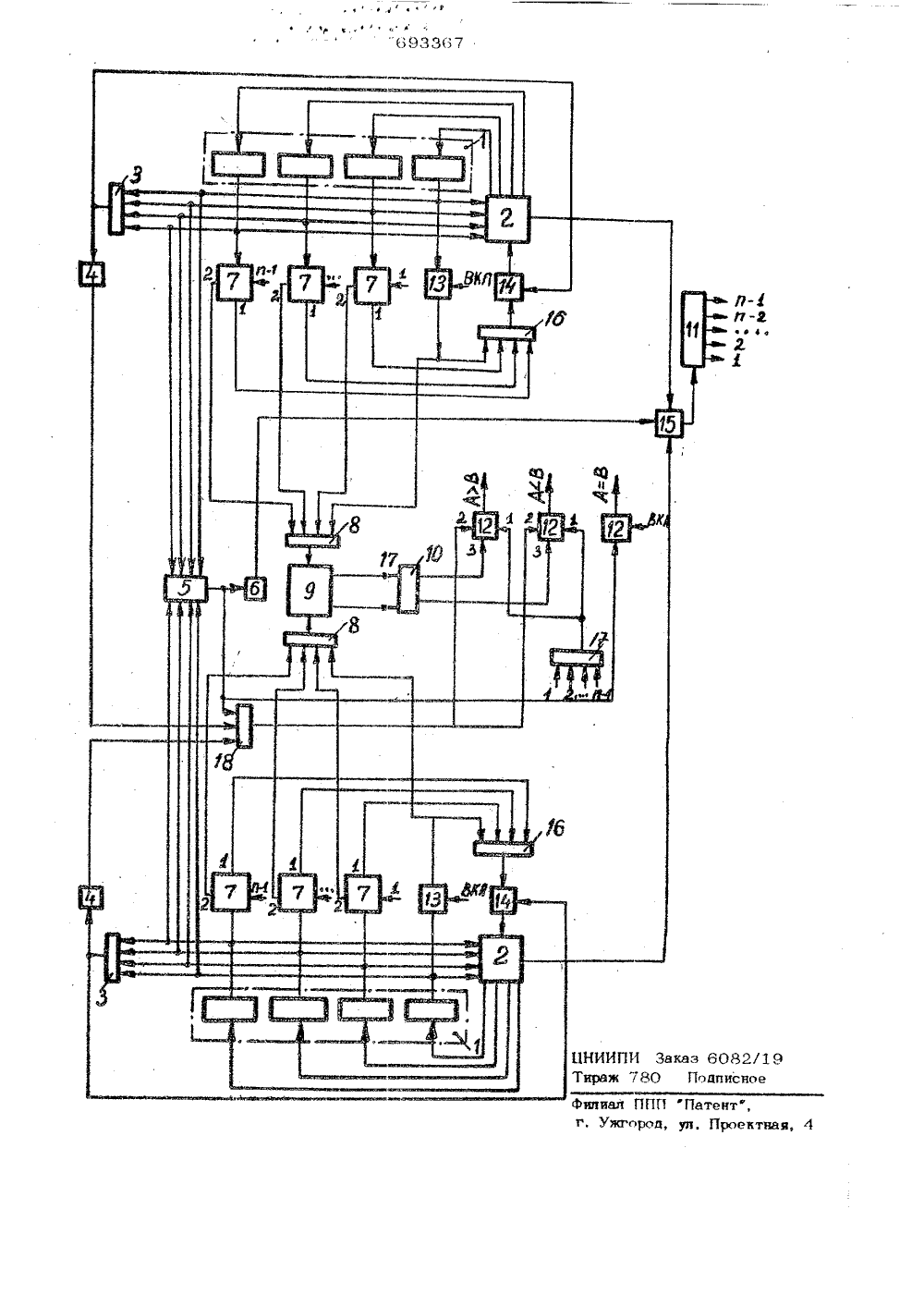

е с :, ы аюаю гОП И ф вм 1 Ф- Аммчвфкал Сооз Сввтсня Сцмапмстеасеа Рвслублмя(51) М. К 606 % 7/04 рисоединением заявкиГосударствеоый комитет СССР оо долам цобретеннй и открытой23) Приоритет Опубликовано 25.10.7 бюллетень %39 Дата опубликования описания 28. 10,79 3) УДК 681.325(72) Авторы изобретен М. Г. факторович н По лисс кнй Нвучно-нсследоввтельскнй и опытно-конструкторск институт автоматизации черной металлургии 71) Заявитель 4) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ ен 1Изобретение относится к автоматикеи вычислительной технике и может бытьиспользовано дпя обработки денных всхемах автоматики н цифровых вычислительных машинах, рвботвюшнх в системеоствточных клвссов,Известно устройство для сравнениячисел, выраженных в системе оствточных классов, содержашее регистры, сумматоры, элементы И, ИЛИ 11,Недостаток известного устройства состоит в том, что оно позволяет уствнввливвть лишь совпадение нпи несовпадениечисел по величине, но не цвет представлення об нх качественном соотношении(больше, меньше),Наиболее бпнзкнм по технической сушности к предлагаемому является устройство, содержвшее регистры, сумматоры,группы элементов И, ИЛИ, НЕ, триггер, одноразрядную схему сравнения,группы блоков преобрвзоввнвя, рвспределнтель снгнвлов, блок срввнення нв рввенство, причем выходы первого регнстрв соединены со входами первогомента ИЛИ, первого сумматора, информационные выходы которого подключеныко входам первого регнстрв, в управляюшнй выход первого сумматора соединен5 с первым входом первого эпементв И,выходы второго регистра подключены ковходам второго элементв ИЛИ, второгосумматора, ннформацнонные выходы которого соединены со входами второгот 0 регнстрв, а упрввляютнй вход второгосумматора подключен ко второму входупервого элемента И 2,Недостатком известного устройстваявляется невысокая скорость обработкиннформвцнн.11 ель изобретения - повыш не быстродействия устройства.Поставленнвя цепь достигается тем,что в устройстве выходы старших рвз 20 рядов первого н второго регистров соединены с первыми входами второго нтретье о элементов И соответственнов выходы остальных рвзрядов первого3 693367 и второго регистров подключены ко входам первой и второй групп блоков преобразования соответственно, выходы регистров подключены к соответствующим входам схемы сравнения на равенство, выход которой соединен с первым входом третьего алемента ИЛИ, второй и третий входы которого через первый и второй элеменгы НЕ подключены к выходам первого и второго эле- О ментов ИЛИ соответственно, выход третьего элемента ИЛИ соединен с первыми входами четвертого и пятого элеменгов И, вторые входы которых подключены к выходам триггера, а третьи - к выходу четвертого элемента ИЛИ, входы кото рого соединены с выходами распределителя сигналов, вход которого подключен к выходу первого элемента И, третий вход которого через третий элемент НЕ соединен с выходом схемы сравнения на равенство, выход которой подключен к первому входу шестого элемента И, второй вход которого соединен с шиной управления, соответствующие выходы блоков преобразования первой группы подключены ко входам пятого и шестого алементов ИЛИ, ко входам которых подключен также выход второго элемента И, второй вход которого соединен с шиной управления, а соответствуккпие выходы блоков преобразования второй группы подкп 1 очены ко,входам седьмсго и восьмого алементов ИЛИ, кс входам которых подключен также выход третьего элемента И, второй вход которого соединен с шиной управления, выходы пятого и седьмого алементов ИЛИ подключены ко входам одноразрядной схемы сравнения, выходы которой соединены со входами триггера, а выходы шестого и восьмого элементов ИЛИ подключены к первым входам четвертого и пятого элементов И, вторые входы которых соединены с выходами первого и второго алементов ИЛИ соответственно, выходы распределителя сигналов подключены ко входам соответствующих блоков преобразования первой и второй групп.Блок-схема предложенного устройстм представлена на чертеже Устройство содержит регистры 1, сумматоры 2, алементы ИЛИ 3 с элементами НЕ 4, схему 5 сравнения на равенство с апементом НЕ 6, блоки 7 преобразования элементы ИЛИ 8, одноразрядную схему 9 сравнения, триг 20 25 30 35 40 50 55 гер 10, распределитель 11 сигналов, элементы И 12-15 элементы ИЛИ 16-18,Устройство работает следующим образом.На регистрах 1 записаны сравниваемые числа. Исходное состояние элементов схемы зависит от соотношения значений сравниваемых чисел, В том случае. если сравниваемые числа равны, на выходе схемы 5 сравнения на равенство и, следовательно, на входе элемента И 12, фиксирующего равенство чисел, имеется сигнал, а нв входе элемента И 15 сигнал отсутствует, Положение триггера 10 произвольно. Сигналы на выходе распределителя 11 сигналов отсутствуют,С появлением импульса на шине управления в случае Д = В сигнал появляется на выходе упомянутого элемента И 12, В случае А 1 Ьс включением схемы значения снап и г поступают с выходов элементов И 13 через элементы ИЛИ 8 на вход одноразрядной схемы 9 сравнения, сигналом с выхода которой триггер 10 устанавливается в состояние АВ или А с В, Значение Аи Ъг, через элементы ИЛИ 16 и И 14 поступают также нв входы сумматоров 2, где происходит вычитание А - с и В - 5 г с перезаписью результатов операции в регистры 1. Сигнал "обнуления" сумматоров через элемент И 15 поступает на вход распределителя 11 сигналов, в результате ".его на его первом выходе появляется единичный сигнал, С появлением этого сигнала блоки 7 преобразования ( и -Ц-х разрядов определяют значения вычитаемых по величине остатков данных разрядов, Значения вычитвемых поступают на входы схемы 9. В зависимости от соотношения между этими значениями триггер 10 устанавливается в соответствующее состояние. Одновременно значения вычитаемых поступают на входы своих сумматоров 2, где выполняется операция, аналогичная описанной выше. В том случае, если после окончания операции результаты сравнятся между собой, т.е. на выходе схемы 5 появится сигнал, либо один из результатов вычитания обратится в нуль, т.е, нв выходе одной из схем 4 появится сигнал, появится сигнал на выходе элемента 6, в результате чего откроется один из элементов 12, фиксирующих АВ, А с В. В противном случае сигнал обнуления" с выходов сумматоров 2 пере933676первого н второго элементов ИЛИ соответственно, выход третьего элемента ИЛИ соединен с первыми иходамн четвертого и пятого элементов И, вторые входы которых подключены к выходам триггера, а третьи - к выходу четвертого элемента ИЛИ, входы которого соединены с выходамн распределителя, сигналов, вход которого юдключен к 10 вькоду первого элемента И, чретий входкоторого через третнй элемент НЕ соединен с выходом схемы сравнения на равенство, выход которой подключен к первому входу шестого элемента И, второй вход которого соединен с шиной управлення, соответствующне выходы блоков преобразования первой группы подключены ко входам пятого н шестого элементов ИЛИ, ко входам которых подключен также выход второго элемента И, второй вход которого соедннен с шиной унравлення, а соответствующие выходы блоков преобразования второй группы подключены ко входам седьмого и восьмого элементов ИЛИ, ко входам которых подключен также выход третье го элемента И, второй вход которого соединен с шиной управлення, выходы пятого .и седьмого элементов ИЛИ под 30клкчены ко входам одноразрядной схемы сравнения, выходы которой соединены со входамп триггера, а выходы шестого и восьмого элементов ИЛИ подключены к первым входам четвертого и питого 35элементов И, вторые входы которых соединены с выходами первого н второго элементов ИЛИ соответственно, выходы распределителя сигналов подключены во входам соответствующих блоков преобразования первой и вюрой групп. Устройство для сравнения чисел, содержащее два регистра, два сумматора, элементы И, ИЛИ, НЕ, триггер, одноразрядную схему сравнения, группы блоков преобразования, распределитель сиг налов, схему сравнения на равенство, причем выходы первого регистра соединены со входами первого элемента ИЛИ, первого сумматора, информационные выходы которого подключены ко входам первого регистра, а управляющий выход первого сумматора соединен с первым входом первого элемента И, выходы второго регистра подключены ко входам второго элемента ИЛИ, второго сумматора, информационные выходы которого соединены со входамн второго регистра, а управляющий вход второго сумматора подключен ко второму входу первого элемента И, о т л и ч а ю - щ е е с я тем, что, с целью повышення быстродействия в нем выходы старшнх разрядов первого и второго регистров соединены с первыми входами второго н третьего элементов И соответственно 1 а выходы остальных разрядов первого и второю регнстров подключены ко входам первой н второй групп блоков преобразования соответственно, выходы регистров подключены к соответствукицим входам схемы сравнения на равенство, выход которой соединен с первым входом третьего элемента ИЛИ, второй и третий входы которого .через первый и второй элементы НЕ подключены к выходам 5 6 водит распределитель сигналов 11 в состояние, при котором на его следующем выходе появляется сигнал, Процесс вычитания продолжится до появления одного из рассмотренных выше случаев.Данное схемное решение позволяет повысить быстродействие устройства сравнения чисел по 1 сравнению с известными техническими решениями этой же задачи. Формула изобретения Источники ннформапии,принятые во внимание при экспертнзе45 1, Авторское свндетельство СССР Мо 242495, кл. 6067/04, 12,05,67. 2, Авторсвэе свидетельство СССР

СмотретьЗаявка

2364633, 24.05.1976

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ И ОПЫТНОКОНСТРУКТОРСКИЙ ИНСТИТУТ АВТОМАТИЗАЦИИ ЧЕРНОЙ МЕТАЛЛУРГИИ

ФАКТОРОВИЧ МИХАИЛ ГРИГОРЬЕВИЧ, ПОЛИССКИЙ ЮРИЙ ДАВИДОВИЧ

МПК / Метки

МПК: G06F 7/04

Опубликовано: 25.10.1979

Код ссылки

<a href="https://patents.su/4-693367-ustrojjstvo-dlya-sravneniya-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сравнения чисел</a>

Предыдущий патент: Ячейка вычислительной среды

Следующий патент: Арифметико-логическое устройство

Случайный патент: Способ регенерации люминофора на основе ортованадата редкоземельных элементов