Сумматор по модулю три

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

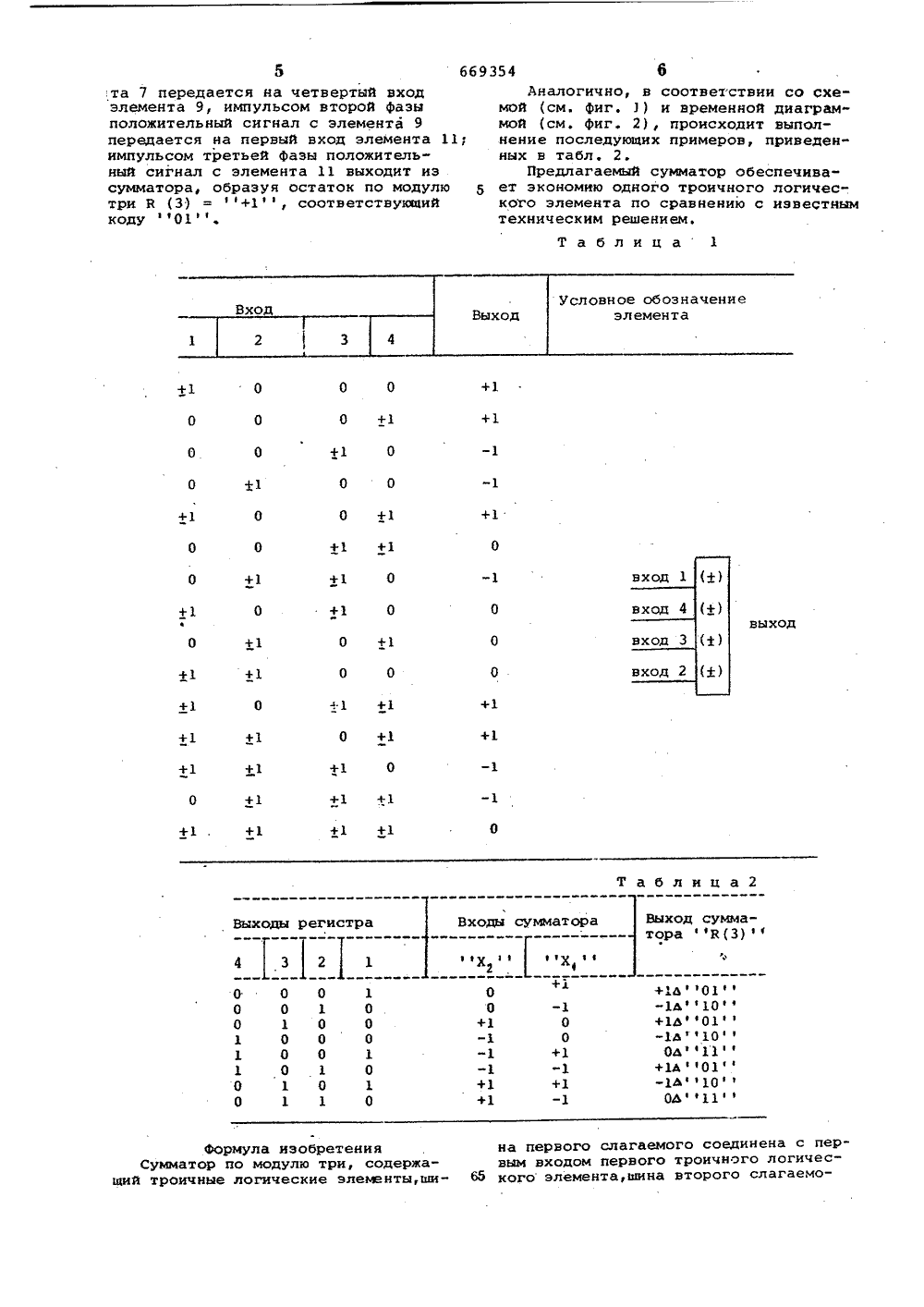

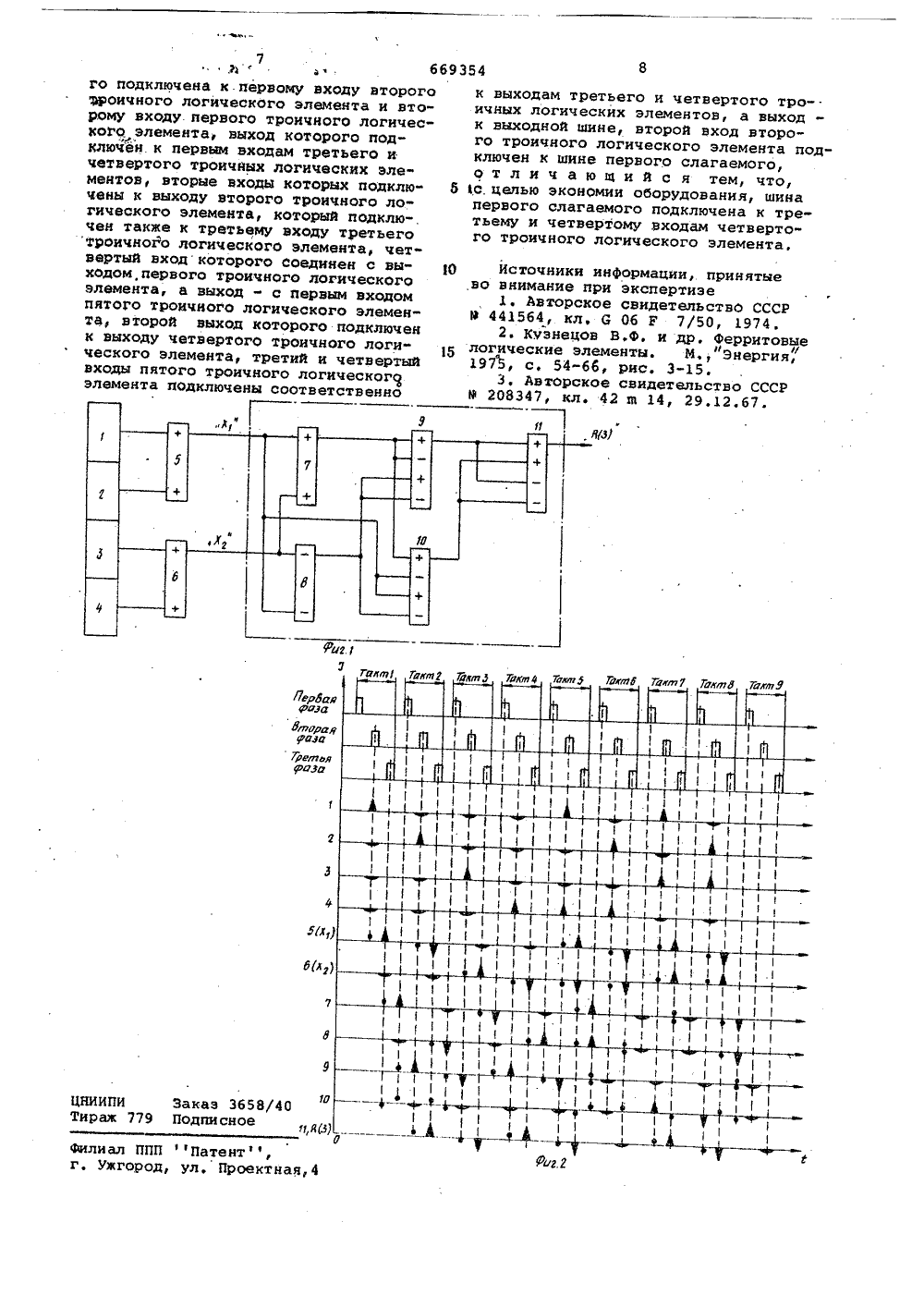

О и и с А и "и"ж ИЗОБРЕТЕНИЯ 11" ф фффнезЯЪ 69354 Союз Советскнк Социалистических Республик(51)М. Кл. С 06 Р 7/50 с присоединением заявки %в Государственный коинтет СССР но делам нзобретеннй н открытнй(54) СУММАТОР ПО МОДУЛЮ ТРИ Изобретение относится к вычислительной технике и может быть использовано при проектировании аппаратныхсредств автоматического контроля цифровых вычислительных устройств.5Известны сумматоры по модулю три,выполненные на ферродиодных логических элементах 1),Однако такие сумматоры по модулютри имеют большие затраты оборудования и невысокую надежность.Наиболее близок к предлагаемомуизобретению сумматор по модулю три,содержащий троичные логические элементы, шина первого слагаемого соединена с первым входом первого троичного логического элемента, шина второго слагаемого подключена к первомувходу второго троичного логическогоэлемента и второму входу первого тро ичного логического элемента, входкоторого подключен к первым входамтретьего и четвертого троичных логических элементов, вторые входы которых подключены к выходу второго троичного логического элемента, которыйподключен также к третьему входу третьего троичного логического элемента, четвертый вход которого соединенс выходом первого троичного логичес- ЗО кого элемента, а выход - с первым входом пятого троичного логического элемента, второй выход которого подключен к выходу четвертого троичного логического элемента, третий и четвертый входы пятого троичного логического элемента подключены соответственно к выходам третьего и четвертого троичных логических элементов, а выход - к выходной шине, второй вход второго троичного логическо. го элемента подключен к шине первого слагаемого 2.Такой сумматор по модулю три имеет сложную реализацию, т.е, выполнен на шести логическйх элементах. Цель изобретения - экономия обору" дования.Это достигается тем, что шина первого слагаемого подключена к третьему и четвертому входам четвертого троичного логического элемента.На фиг. 1 дана схема формирования остатка четырехразрядного числа; на фиг. 2 - временная диаграмма работы устройства, где обозначены: й - импульсы трехфазного источника питания: в- запись +1; т - запись -1; - считывание 0,.й. - считывание +1;- считываф Четырехраэрядное число находитсяв разрядах регистра 1-4. Троичныелогические элементы 5 и 6 определяютостаток по модулю три четверичныхцифр, расположенных в двух соседних 5разрядах. Сумматор по модулю трисовокупность троичных логических (элементов 7-11) - опрегеляет остатокпо модулю три от суммы цифр, поступающих на входы элементов 5 и б иэ 10разрядов регистра 1 - 4. Выходы разрядов регистра 1-4 соединены с входа"ми троичных логических элементов 5 и6.Выход троичного логического элемента 5 (шина первого слагаемого Х)соединен с входом первого троичногологического элемента 7, с входом второго троичного логического элемента8, с входами четвертого троичногологического элемента 10 сумматора,Выход трсичного логического элемента б (шина второго слагаемого Х 1)соединен с входом первого троичногологического элемента 7 и с входомвторого троичного логического элемента 8 сумматора. Выход первого троичного логического элемента 7 соединен с входами третьего троичного логического элемента 9, с входом четвертого троичного логического элемента10 сумматора, Выход второго троичного логического элемента 8 соединенс входами третьего троичного логического элемента 9, с входом четвертого троичного логического элемента10 сумматора, Выход третьего троичного логического элемента 9 соединенс входами пятого троичного логического элемента 11 сумматора. Выходчетвертого троичного логического элемента 10 соединен с входами пятого 40троичного логического элемента 11сумматора. Иа выходе пятого троичного логического элемента 11 сумматораФормируется остаток по модулю триВф (3),Сумматор по модулю три собран напяти троичных логических элементах,каждый иэ которых выполняет троич"ные операции, описанные в табл. 1.Указанные операции образуют Функционально, полную систему логических Функ ций и могут быть реализованы на основе троичных элементов (например,на ферритовых логических элементах)3),Система тактового питания схемысумматора-трехфазная; при этом каждый следующий разряд слагаемого поступает на вход сумматора через три Фазы (один такт) передачи информациипо элементам схемы (см. Фиг. 2).Тактовым импульсом первой Фазы 6считывается информация с троичных логических элементов 7 и 8, второй Фазы - с разрядов регистра 1 - 4 и тро"ичных логических элементов 9 и 10, атретьей фазы - с троичных логическихэлементов 5, 6 и 11. Рассмотрим работу сумматора по модулю три на примерах определения остатков восьми чисел, представленныхв табл. 2. 1 в двоичной системесчисления представляется положительным сигналом в разряде, а 0отсутствием сигнала в разряде, Числа на разрядах регистра 1 - 4 меняются в каждом такте последовательнов соответствии с табл. 2 (см, фиг.1 и 2).П р им е р 1. (число - 0001) .Тактовым импульсом второй фазы первого такта считывается информация с первого разряда регистра 1 и согласнологике работы элемента, записаннойв табл. 1, положительный сигнал спервогО разряда регистра 1 передается на первый вход элемента 5; импульсом третьей Фазы положительный сиг"нал с элемента 5 передается на пер"вый вход элемента 7 и третий входэлемента 10.Импульсом первой фазы второго такта положительный сигнал с элемента 7передается на первый вход элемента 9и 10, импульсом второй фазы положительный сигнал с элемента 9 передается на первый вход элемента 11, импульсом третьей фазы положительный .сигнал с элемента 11 выходит иэ сумматора, образуя остаток по модулютри В (3) = ф 1, соответствующийкоду 01П р и м е р 2. (число - 0010),Тактовым импульсом второй фазы второго такта считывается информация совторого разряда регистра 2, положи"тельный сигнал передается на второйвход элемента 5, импульсом третьейФазы отрицательный сигнал с элемента 5 передается на второй вход элемента 8 и четвертого элемента 10.Импульсом первой Фазы третьеготакта отрицательный сигнал с элемента 8 передается на четвертый входэлемента 10,Импульсом первой Фазы третьеготакта отрицательный сигнал с элемента 8 передается на второй вход элемен"та 9 и 10; импульсом второй фазы отрицательный сигнал с элемента 9 передается на третий вход элемента 11,импульсом третьей фазы отрицательныйсигнал с элемента 11 выходит Из суююатора, образуя остаток по модулю триК (3) = -1, соответствующий коду10П р и м е р 3. (число - 0100).Тактовым импульсом второй Фазы третьего такта считывается информацияс третьего разряда регистра 3, положительный сигнал передается напервый вход элемента 6; импульсомтретьей фазы положительный сигнал сэлемента 6 передается на второй входэлемента 7Импульсом первой фазы четвертоготакта отрицательный сигнал с элемен:та 7 передается на четвертый входэлемента 9, импульсом второй Фазыположительный сигнал с элемента 9передается на первый вход элемента 11;импульсом третьей фазы положительный сигнал с элемента 11 выходит изсумматора, образуя остаток по модулютри й (3) = +1, соответствующийкоду 01 0 0 О +1 +1 0 0 О 0 +1 Формула изобретенияСумматор по модулю три, содержтроичные логические элементы,Аналогично, в соответствии со схемой (см. Фиг,и временной диаграммой (см, фиг. 2), происходит выполнение последующих примеров, приведенных в табл, 2.Предлагаемый сумматор обеспечивает экономию одного троичного логического элемента по сравнению с известным техническим решением. мматора Выход сумматора ф фв(3) ф+ФЬ 1 101Ф -1 Ь 110 ф +1 Ь 01 -1 Ьф 10 фОЬ 111+1 А01-1 Ь10ОЬ 11на первого слагаемого соединена с пе вым входом первого троичного логичес кого элемента, шина второго слагаемо/7 ерВа Раза Втара Раза Треагья раза--- - Ф1+ +ф Риг 2 7Л ь сб го подключена к первому входу второго щоичного логического элемента и второму входу первого троичного логического элемента, выход которого подключен к первым входам третьего и четвертого троичных логических элементов, вторые входы которых подключены к выходу второго троичного логического элемента, который подключен также к третьему входу третьего троичной логического элемента, чет" вертый вход которого соединен с выходом, первого троичного логического элемента, а выход - с первым входом пятого троичного логического элемента, второй выход которого подключен к выходу четвертого троичного логического элемента, третий н четвертый входы пятого троичного логического элемента подключены соответственно ЦНИИПИ Заказ 3658 Тираж 779 Подписное Филиал ППП Патентф,г. Ужгород, ул. Проектная,4 к выходам третьего н четвертого тро ичных логических элементов, а выходи выходной шине, второй вход второго троичного логического элемента подключен к шине первого слагаемого,о т л и ч а ю щ и й с я тем, что, б 1 с. целью экономии оборудования, шинапервого слагаемого подключена к третьему и четвертому входам четвертого троичного логического элемента,г 0 Источники инФормации, принятые.во внимание при экспертизе1, Авторское свидетельствО СССРР 441564, кл, 6 06 Р 7/50, 19742. Юэнецов В.Ф. и др . Ферритовые

СмотретьЗаявка

2410185, 05.10.1976

ПРЕДПРИЯТИЕ ПЯ В-2969

МИНГАЛЕЕВ ФАЗЫЛ ФЕРИТОВИЧ, ПЛАСТУН НИКОЛАЙ ТРОФИМОВИЧ, ПАВЛОВ ВЛАДИМИР ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 7/50

Опубликовано: 25.06.1979

Код ссылки

<a href="https://patents.su/4-669354-summator-po-modulyu-tri.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю три</a>

Предыдущий патент: Арифметическое устройство

Следующий патент: Многоканальное устройство для последовательного обслуживания запросов

Случайный патент: Суспензия для электрофоретического осаждения медных и бронзовых покрытий