Устройство для формирования адреса в вычислительной системе иерархической структуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

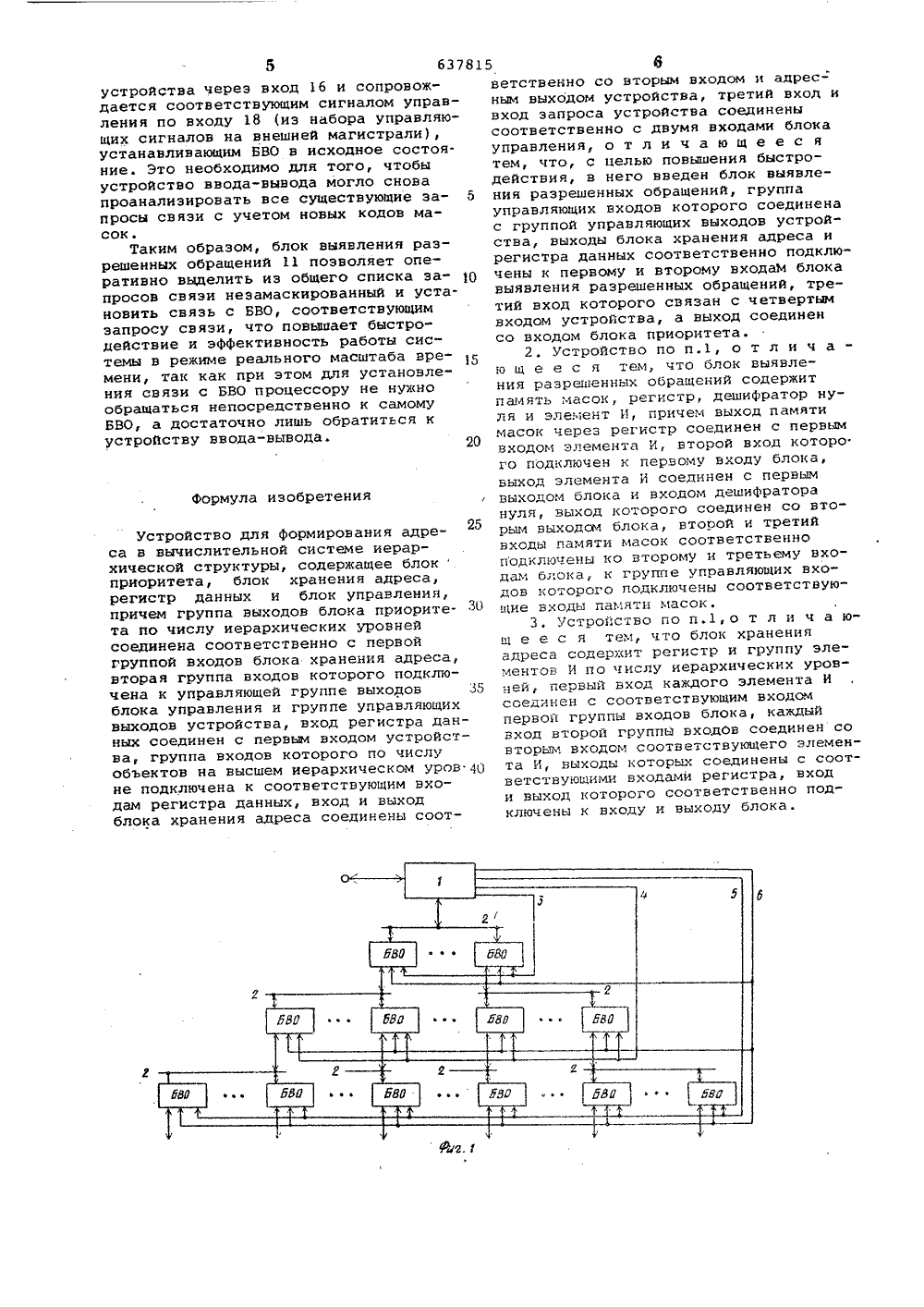

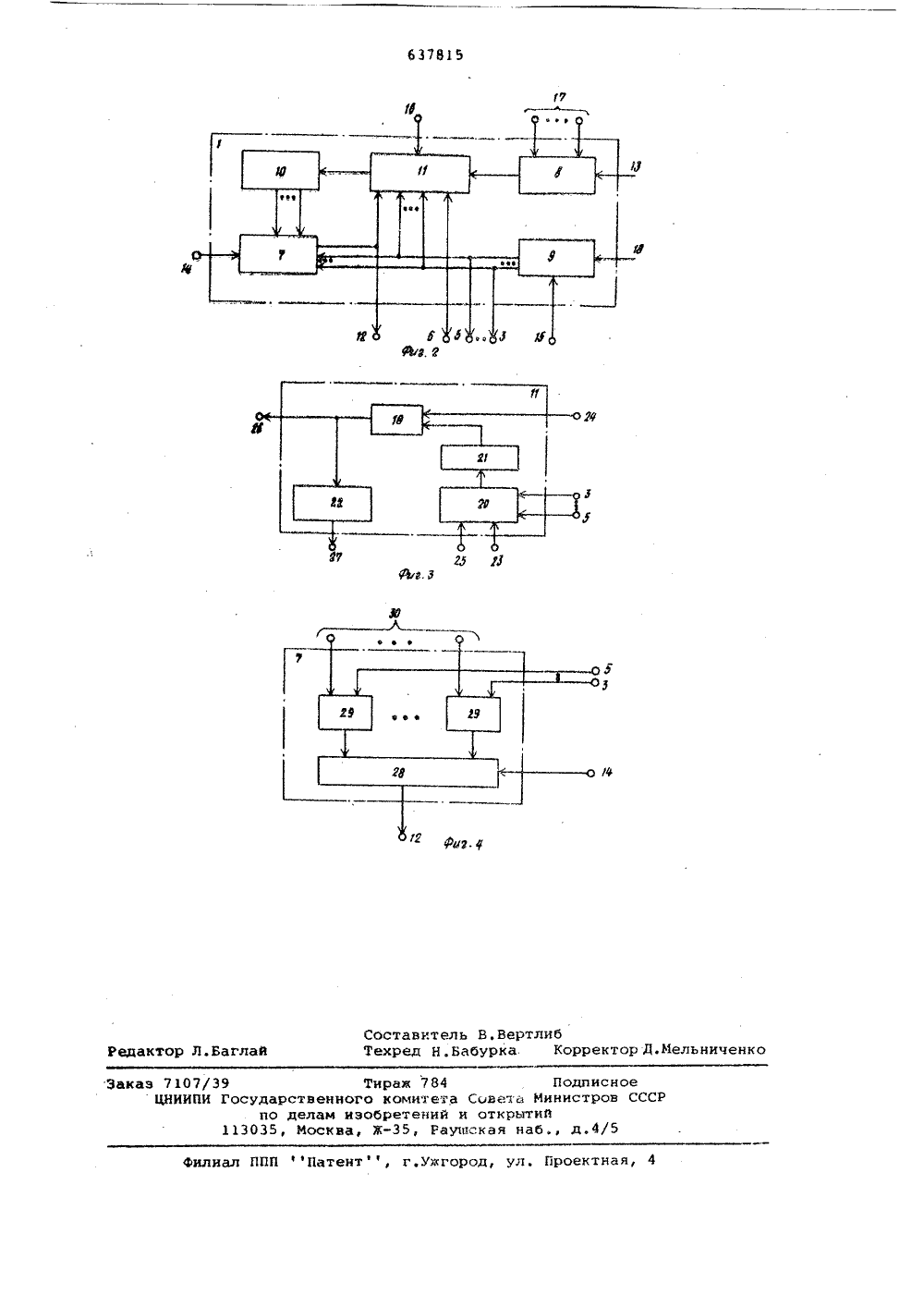

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДГтЕЛЬСтВ Сеез Ссеетсв Соцмалстичеек Уеепубпи(61) Дополнительное к авт, свид-ву - (22) Заявлено 0401.76 (21) 2309879/18(51) М. Кл. 5 06 Р 9/ рисоеаинением заявки Я твеииый Министро , изобр отирыти осуаэ мта о аел иитетСССРиий рио УДК 681. 326, 3088,8)(43) Опу оллетень Ж 46 ковано 15.12 т) Дата ликования описания 15,12,78 а ав,А.С.Кандауров, В.С.Коновало Г.Карнаух, 7. И.С.Шанлрин дент ) Заявитель ециальное конструкторское бюро си автоматического управления54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ РДРЕСй В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕИВ ИЕРАРХИЧЕСК СТРУКТУРЫна высшем иерархическом уровне подключена к соответствующим входам регистра данных, вход и выход блока хранения адреса соединены соответственно со вторым входом и адресным выходом устрсйства, третий вход и вход запроса устройства соединены соответственно с двумя входами блока управленияНедостатком этого усройства является низкое быстродействие, вследствие программной реализации процедур выбора осъекта,Целью изобретения является повышение быстродействия устройства, что позволяет повысить зФфективность работы иерархической системы в реальном масштабе времени.Цель достигается тем, что в устройство введен блок выявления разрешен ных обращений, группа Управляющих входов которого соединена с группой управ ляюших выходов устройства, выходы блока хранения адреса н регнстоа данных соответственно подключены к первому и второму входам блока выявления разрешенных обращений, третий вход которого связан с четвертым входом устрой" ства, а выход соединен со входом блока приоритета. Кроме того, блок выявления разрешенных обращений 1:одержит Изобретение относится к области втоматики и вычислительной техникиможет быть использовано в системах ерархической структуры с магистральым принципом сопряжения объектов на Ь аждом иерархическом уровне.Известны устройства, предназначеные для организации обмена инФормацией ежду центральным процессором и объеками, подключенными к блокам выполне ия операций,и, содержащие блок управ-,ения, регистры адреса, регистры данных.Эти устройства не приспособлены для приоритетного выбора сигналов зароса и имеют низкое быстродействие. 16 н Наиболее близким к данному устройству является устройство, содержащее блок приоритета, блок хранения адреса, регистр данных и блок управления,при чем группа выходов блока приоритета по числу иерархических уровней соединена соответственно с первой группой входов блока хранения адреса, вторая группа входов которого подключена к 26 управляющей группе выходов блока управления и группе управляющих выходов устройства, вход регистра данных соединен с первым входом устройства, группа входов которого по числу объектовпамять масок, регистр, дешифратор нуля и элемент И, причем выход памяти масок через регистр соединен с первым входом элемента И, второй вход которого одключен к первому входу блока, выход лемента И соединен с первым выходом лока и входом дешифратора нуля, выход,5 которого соединен со вторым выходом блока, второй и третий входы памяти масок соответственно подключены ко второму и третьему входам блока, к группе управляющих входов которого 10 подключены соответствующие входы памяти масок. Кроме того, блок хранения адреса содержит регистр и группу элементов И по числу иерархических уРовней, первый вход каждого элемен- д та И соединен с соответствующим входом первой группы входов блока, каждый вход второй группы входов соединен со вторым входом соответствующего элемента И,выходы которых соединены 20 соответствующими входами регистра, вход и выход которого соответственно подключены к входу и выходу блока,На фиг.1 изображена система иерархической структуры, в которой исполь зуется рассматриваемое устройство;на фиг. 2-4 изображены соответственно блок-схемы устройства, блок выявления разрешенных обращений и блок хранения адреса.Описываемая система содержит блоки выполнения операций (БВО), к которым подключены объекты - источники и приемники информации.БВО соединены в иерархическую структуру и связаны между собой устройст вом для формирования адреса 1 посредством магистральных шин 2, управляющих шин первого 3, второго 4, и третьего 5 уровней иерархии, а также шин блокировки б. 40устройство для формирования адреса 1 (фиг.2) содержит блок хранения адреса 7, регистр данных 8, блок управления 9, блок приоритета 10, блок выявленич разрешенных обращений 11, адрес.45 ный выход устройства 12, первый 13, второй 14, третий 15 и четвертый 16 входы устройства, группу входов 17 устройства по числу блоков выполнения операции, подключенных к магистрали 50 на высшем иерархическом уровне, вход запроса 18.Блок выявления разрешенных обращений 11 (фиг.3) содержит элемент И 19, память масок 20, регистр 21 и дешифратор нуля 22,.первый вход 23, второй вход 24, третий вход 25, первый 26 и второй 27 выходы.Блок хранения адреса 7 ( фиг,4) содержит регистр 28 и группу элементов И 29 и первую группу входов 30. 60Устройство работает следующим образом.Когда какие-либо БВО низшего уровня требуют связи, выдавая при этом запрос связи, то БВО высших уровней 65 пропускают его на вход запроса 18 устройства 1 формирования адреса. Блок управления 9 вырабатывает сигнал на выходе 3 для управления группой БВО высшего уровня, По этому сигналу БВО данной группы выставляют на соответствующие разряды информационных шин магистрали 2 сигнал магистральногб запроса связи ( в соответствии с по- зиционным приоритетом) соответствующих групп второго уровня. Эти сигналы считываются в регистре 8 данных в виде позиционных кодов, а в блоке 11 выявления разрешенных обращений из памяти 20 масок в регистр 21 считывается слово масок. Посредством элемента И 19 из позиционного кода, поступающего по входу 24, выделяются только те разряды, которые не соответствуют значениям соответствующих разрядов кода масок. Выделенный код поступает на дешифратор 22 нуля и на вход блока 10 приоритета.Если выделенный код оказался нулевым (все позиционные запросы связи замаскированы), то на выходе дешифратора 22 нуля формируется сигнал на выходе блокировки б. По этому сигналу в БВО производится блокировка запроса связи. Вследствие блокировки сигналов запроса связи высшего уровня, БВО снимает сигнал на запрос связи, а блок управления 9 переходит в режим ожидания следующего прерывающего сигнала, В случае, если сигнал запроса связи появится снова (например ББО, которые до этого не выставляли сигналов запросов связи, выставили их), то блок управления 9 повторяет цикл поиска приоритетного и не замаскированного сигнала запроса связи.Если выделенный код оказался не нулевым, то в блоке приоритета 10 производится преобразование его в двоичный нормальный код адреса БВО первого уровня. Полученный код адреса выдается на входы 30 блока. хранения адреса 7 вместе с управляющим сигналом по шинам 3-5, через соответствующий элемент И 29 записывается в соответствующую часть регистра адреса 28 и на адресном выходе 12 выставляется адрес БВО, а на выходе блока управления 9 формируется сигнал управления группами БВО следующего уровня,Цикл поиска приоритетного и незамаскированного запроса связи повторяется в том порядке, как приведено выше, за исключением того, что в блоке выявления разрешенных обращений 11 из памяти 20 масок считывается другой код масок. Адрес соответствующего кода масок определяется информацией, находящейся в регистре адреса, и присутствием одного иэ управляющих сигналов по шинам 3-5.Занесение и изменение кода масок соответствующих групп, любого уровня, производится от внешнего управляющего63781устройства через вход 16 и сопровождается соответствующим сигналом управления по входу 18 (из набора управляющих сигналов на внешней магистрали), устанавливающим БВО в исходное состояние. Это необходимо для того, чтобы устройство ввода-вывода могло снова проанализировать все существующие эа просы связи с учетом новых кодов ма" сок.Таким образом, блок выявления разрешенных обращений 11 позволяет оперативно выделить из общего списка за О просов связи незамаскированный и установить связь с БВО, соответствующим запросу связи, что повышает быстродействие и эффективность работы системы в режиме реального масштаба времени, так как при этом для установления связи с БВО процессору не нужно обращаться непосредственно к самому БВО, а достаточно лищь обратиться к устройству ввода-вывода.20Формула изобретенияустройство для формирования адре 25 са в вычислительной системе иерархической структуры, содержащее блокприоритета, блок хранения адреса, регистр данных и блок управления, причем группа выходов блока приорите- ЗО та по числу иерархических уровней соединена соответственно с первой группой входов блока хранения адреса, вторая группа входов которого подключена к управляющей группе выходов 35 блока управления и группе управляющих выходов устройства, вход регистра данных соединен с первым входом устройства, группа входов которого по числу объектов на высшем иерархическом уров л 0 не подключена к соответствующим входам регистра данных, вход и выход блока хранения адреса соединены соот 5 6ветственно со вторым входом и адрес- ным выходом устройства, третий вход н вход запроса устройства соединены соответственно с двумя входами блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введен блок выявления разрешенных обращений, группа управляющих входов которого соединена с группой управляющих выходов устройства, выходы блока хранения адреса и регистра данных соответственно подключены к первому и второму входаМ блока выявления разрешенных обращений, третий вход которого связан с четвертым входом устройства, а выход соединен со входом блока приоритета.2, Устройство по п.1, о т л и ч а - ю щ е е с я тем, что блок выявления разрешенных обращений содержит память масок, регистр, дешифратор нуля и элемент И, причем выход памяти масок через регистр соединен с первым входом элемента И, второй вход которо го подключен к первому входу блока, выход элемента И соединен с первым выходом блока и входом дешифратора нуля, выход которого соединен со вторым выходск блока, второй и третий входы памяти масок соответственно подключены ко второму и третьему входам блока, к группе управляющих входов которого подключены соответствующие входы памяти масок.3. Устройство по п.1,о т л и ч а ющ е е с я тем, что блок хранения адреса содержит регистр и группу элементов И по числу иерархических уровней, первый вход каждого элемента И соединен с соответствующим входом первой группы входов блока, каждый вход второй группы входов соединен со вторым входом соответствующего элемента И, выходы которых соединены с соответствующими входами регистра, вход и выход которого соответственно подключены к входу и выходу блока./5 П 11 атент, г,ужгород, ул. Проект фил Эакаэ 7107/39 Т ЦНИИПИ Государственного по делам иво 113035, Москва, раж 784 Подлкол 1 итета Совета Иинисретений и открытий

СмотретьЗаявка

2309879, 04.01.1976

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКОЕ БЮРО СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ

ДИДЕНКО КОНСТАНТИН ИВАНОВИЧ, КАНДАУРОВ АНАТОЛИЙ СТАНИСЛАВОВИЧ, КАРНАУХ КОНСТАНИН ГРИГОРЬЕВИЧ, КОНАРЕВ АНАТОЛИЙ НИКОЛАЕВИЧ, КОНОВАЛОВ ВАЛЕРИЙ СЕМЕНОВИЧ, ШАНДРИН ИГОРЬ СТЕПАНОВИЧ

МПК / Метки

МПК: G06F 9/20

Метки: адреса, вычислительной, иерархической, системе, структуры, формирования

Опубликовано: 15.12.1978

Код ссылки

<a href="https://patents.su/4-637815-ustrojjstvo-dlya-formirovaniya-adresa-v-vychislitelnojj-sisteme-ierarkhicheskojj-struktury.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования адреса в вычислительной системе иерархической структуры</a>

Предыдущий патент: Многоканальное устройство для управления обслуживанием запросов

Следующий патент: Резервированное трехканальное устройство

Случайный патент: Подающий узел лентопротяжного механизма