Адаптивный дельта-кодер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

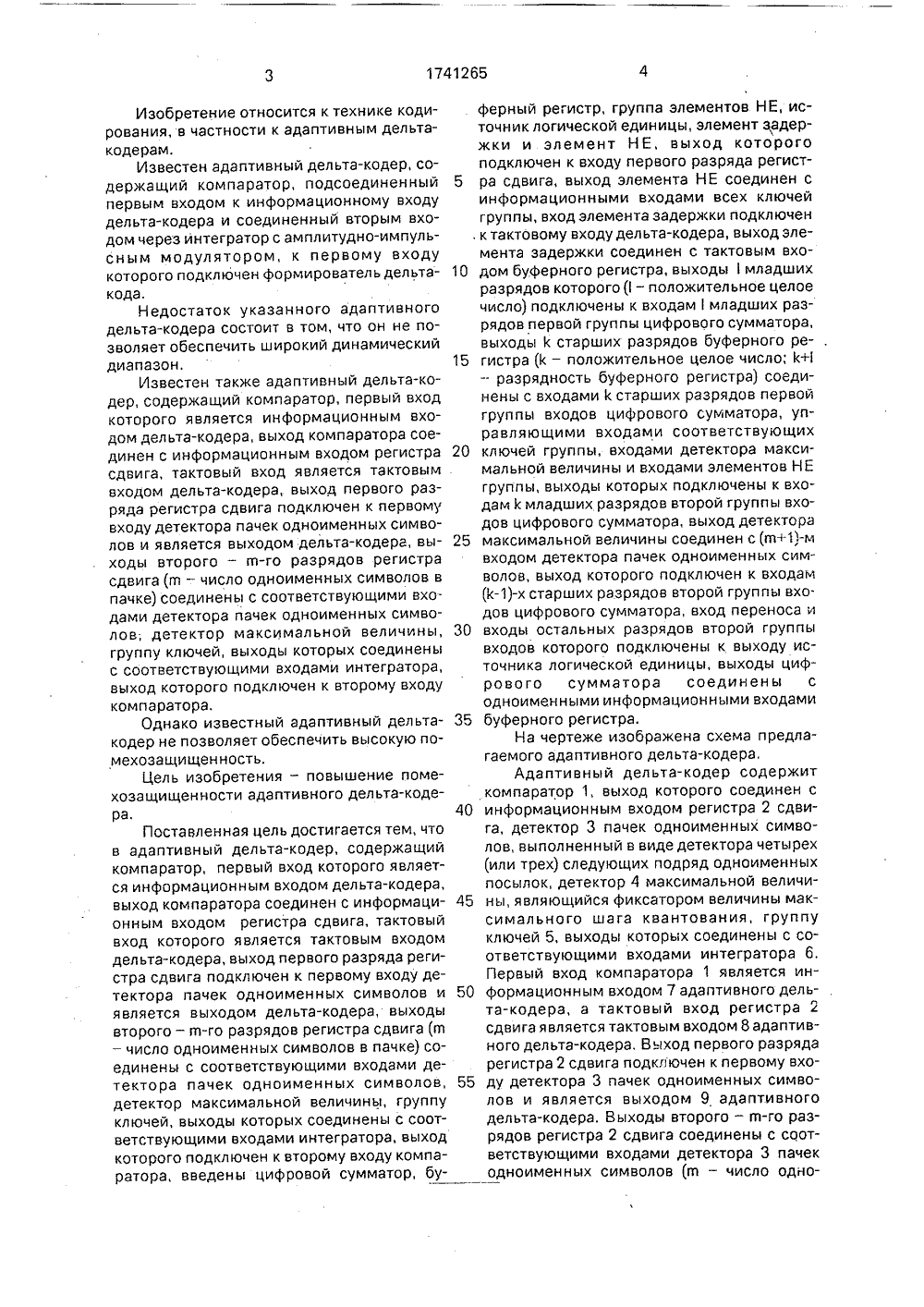

(51)5 Н 03 М 3/02 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(57) Изобретение относится квычислительнойтехнике, м,б, использовано в системах кодирования для передачи аналоговой информации и по.зволяет повысить помехозащищенность дельта-кодера. Это обеспечивается благодаря более качественной адаптации шага квантования, Дельта-кодер содержит компаратор 1, регистр 2 сдвига, детектор 3 пачек одноименных символов, детектор 4 максимальной величины, группу ключей 5, интегратор 6, цифровой сумматор 12, буферный регистр 13, группу элементов НЕ 14, источник 15 логической единицы, элемент 16 задержки, элемент НЕ 17. 1 ил.Изобретение относится к технике кодирования, в частности к адаптивным дельта- кодерам.Известен адаптивный дельта-кодер, содержащий компаратор, подсоединенный первым входом к информационному входу дельта-кодера и соединенный вторым входом через интегратор с амплитудно-импульсным модулятором, к первому входу которого подключен формирователь дельта- кода.Недостаток указанного адаптивного дельта-кодера состоит в том, что он не позволяет обеспечить широкий динамический диапазон.Известен также адаптивный дельта-кодер, содержащий компаратор, первый вход которого является информационным входом дельта-кодера, выход компаратора соединен с информационным входом регистра сдвига, тактовый вход является тактовым входом дельта-кодера, выход первого разряда регистра сдвига подключен к первому входу детектора пачек одноименных символов и является выходом дельта-кодера, выходы второго - а-го разрядов регистра сдвига (щ - число одноименных символов в пачке) соединены с соответствующими входами детектора пачек одноименных символов; детектор максимальной величины, группу ключей, выходы которых соединены с соответствующими входами интегратора, выход которого подключен к второму входу компаратора.Однако известный адаптивный дельта- кодер не позволяет обеспечить высокую помехозащищенность,Цель изобретения - повышение помехозащищенности адаптивного дельта-кодера,Поставленная цель достигается тем, что в адаптивный дельта-кодер, содержащий компаратор, первый вход которого является информационным входом дельта-кодера, выход компаратора соединен с информационным входом регистра сдвига, тактовый вход которого является тактовым входом дельта-кодера, выход первого разряда регистра сдвига подключен к первому входу детектора пачек одноименных символов и является выходом дельта-кодера, выходы второго - а-го разрядов регистра сдвига (в - число одноименных символов в пачке) соединены с соответствующими входами детектора пачек одноименных символов, детектор максимальной величины, группу ключей, выходы которых соединены с соответствующими входами интегратора, выход которого подключен к второму входу компаратора, введены цифровой сумматор, буферный регистр, группа элементов НЕ, источник логической единицы, элемент задержки и элемент НЕ, выход которогоподключен к входу первого разряда регист 5 ра сдвига, выход элемента НЕ соединен синформационными входами всех ключейгруппы, вход элемента задержки подключен, ктактовому входудельта-кодера, выходэлемента задержки соединен с тактовым вхо 10 дом буферного регистра, выходымладшихразрядов которого( - положительное целоечисло) подключены к входаммладших разрядов первой группы цифрового сумматора,выходы К старших разрядов буферного ре- .15 гистра (К - положительное целое число; 1+1- разрядность буферного регистра) соединены с входами 1 старших разрядов первойгруппы входов цифрового сумматора, управляющими входами соответствующих20 ключей группы, входами детектора максимальной величины и входами элементов НЕгруппы, выходы которых подключены к входам К младших разрядов второй группы входов цифрового сумматора, выход детектора25 максимальной величины соединен с (в+1)-мвходом детектора пачек одноименных символов, выход которого подключен к входам(К)-х старших разрядов второй группы входов цифрового сумматора, вход переноса и30 входы остальных разрядов второй группывходов которогО подключены к выходу источника логической единицы, выходы цифрового сумматора соединены содноименными информационными входами35 буферного регистра.На чертеже изображена схема предлагаемого адаптивного дельта-кодера,Адаптивный дельта-кодер содержиткомпаратор 1, выход которого соединен с40 информационным входом регистра 2 сдвига, детектор 3 пачек одноименных символов, выполненный в виде детектора четырех(или трех) следующих подряд одноименныхпосылок, детектор 4 максимальной величи 45 ны, являющийся фиксатором величины максимального шага квантования, группуключей 5, выходы которых соединены с соответствующими входами интегратора 6.Первый вход компаратора 1 является ин 50 формационным входом 7 адаптивного дельта-кодера, а тактовый вход регистра 2сдвига является тактовым входом 8 адаптивного дельта-кодера, Выход первого разрядарегистра 2 сдвига подключен к первому вхо 55 ду детектора 3 пачек одноименных символов и является выходом 9 адаптивногодельта-кодера, Выходы второго - в-го разрядов регистра 2 сдвига соединены с соответствующими входами детектора 3 пачекодноименных символов (в - число одно5 10 дельта-кодера, Выход элемента 16 задержки соединен с тактовым входом буферного 25 30 35 40 именных символов в пачке), Выход интегратора 6 подключен к второму входу компаратора 1. При этом интегратор 6 выполнен в виде резисторов 10 и интегрирующего элемента 11. Первые выводы резисторов 10 совпадают с входами интегратора 6. Вторые выводы резисторов 10 соединены с входом интегрирующего элемента 11, выход которого совпадает с выходом интегратора 6,Адаптивный дельта-кодер содержит также цифровой сумматор 12, буферный регистр 13, группу элементов НЕ 14, источник 15 логической единицы, элемент 16 задержки и элемент НЕ 17, выход которого подключен к выходу первого разряда регистра 2 сдвига.Выход элемента НЕ 17 соединен с информационными входами всех ключей 5 группы. Вход элемента 16 задержки подключен к тактовому входу 8 адаптивного регистра 13. Выходымладших разрядов буферного регистра 13 подкгючены к входаммладших разрядов первой группы входов цифрового сумматора 12 ( положительное целое число). Выходы 1 старших разрядов буферного регистра 13 соединены с входами 1 старших разрядов первой группы входов цифрового сумматора 12 (1 - положительное целое число; К+ - разрядность буферного регистра 13), Выходы К старших разрядов буферного регистра 13 соединены также суправляющими входами соответствующих ключей 5 группы, с входами детектора 4 максимальной величины и с входами элементов НЕ 14 группы. Выходы элементов НЕ 14 группы подключены к входам К младших разрядов второй группы входов цифрового сумматора 12, Выход детектора 4 максимальной величины соединен с (в+1)-м входом детектора 3 пачек одноименных символов, выход которого подключен к входам (Е)-х старших разрядов второй группы входов цифрового сумматора 12, Вход переноса и входы остальных разрядов второй группы входов цифрового сумматора 12 подключены к выходу источника 15 логической единицы. Выходы цифрового сумматора 12 соединены с одноименными информационными входами буферного регистра 13.Адаптивный дельта-кодер работает следующим образом,На первый вход компаратора 1 подается входной аналоговый сигнал тональной частоты, например речевой сигнал, а на второй вход - аппроксимирующий сигнал с выхода интегратора 6, Компаратор 1 сравнивает эти сигналы, а на его выходе в зависимости от знака разности образуется 45 50 55 либо уровень логической единицы, либо уровень логического нуля, С выхода компаратора 1 сигнал поступает на информационный вход регистра 2 сдвига, на тактовый вход которого с тактового входа 8 адаптивного дельта-кодера поступает сигнал дискретизации с частотой 32 кбит/с. С выхода первого разряда регистра 2 сдвига сигнал, нормированный по вреМени, подается на выход 9 адаптивного дельта-кодера и на детектор 3 пачек одноименных символов, на который поступают также сигналы с выходов (в)-х разрядов регистра 2 сдвига, Сигнал детектора 3 пачек одноименных символов определяет величину приращения шага квантования. Если пачки следующих подряд одноименных символов отсутствуют, то нет приращения шага. Если происходит появление пачек следующих подряд одноименных символов, то в соответствии с выбранным алгоритмом приращение шага составляет удвоенную величину минимального шага квантования на каждом тактовом интервале.С выхода детектора 3 пачек одноименных символов сигнал подается на входы К)-х старших разрядов второй группы входов цифрового сумматора 12, На входы 1 старших разрядов первой группы входов цифрового сумматора 12 подаются сигнал;: с выходов М старших разрядов буферного регистра 13. С выходов К старших разрядов буферного регистра 13 сигналы поступают также через элементыНЕ 14 группы на входы 1 младших разрядов второй группы входов цифрового сумматора 12. На входымладших разрядов первой группы входов цифрового сумматора 13 поступают сигналы с выходовмладших разрядов буферного регистра 13, При этом на входы остальных разрядов второй группы входов и вход переноса цифрового сумматора 12 подается уровень логической единицы с источника 15 логической единицы. На тактовый вход буферного регистра 13 с элемента 16 задержки подается сигнал синхронизации с частотой 32 кГц, сдвинутый на 2 мкс относительно сигнала синхронизации. поступающего стактового входа 8 адаптивного дел ьта-кодера.С части (К) выходов старших разрядов буферного регистра 13 сигналы поступают также на детектор 4 максимальной величины, воздействующий на детектор 3 пачек одноименных символов, При этом детектор 4 максимальной величины запрещает детектору 3 пачек одноименных символов выдавать сигнал о наличии пачек одноименных символов, что обеспечивает фиксацию максимального шага квантования, В противном случае при увеличении уровня сигнала на1741265 40 45 50 Составитель Д.ХейфецТехред М.Моргентал Корректор С.Шевкун Редактор А,Огар Заказ 2092 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 входе 7 адаптивного дельта-кодера сигнал с выхода детектора 3 пачек одноименных символов перебрасывает уровень старших разрядов буферного регистра 13 из логической единицы в логический ноль, При этом шаг квантования становится минимальным, что может привести к нарушению работы адаптивного дельта-кодера.С выхода первого разряда регистра 2 сдвига сигнал подается, кроме того через элемент НЕ 17 на информационные входы ключей 5, воздействующих через интегратор 6 на компаратор 1.Формула изобретения Адаптивный дельта-кодер, содержащий компаратор, первый вход которого является информационным входом дельта-кодера, выход компаратора соединен с информационным входом регистра сдвига, тактовый вход которого является тактовым входом дельта-кодера, выход первого разряда регистра сдвига подключен к первому входу детектора пачек одноименных символов и является выходом дельта-кодера, выходы второго - а-го разрядов регистра сдвига (а - число одноименных символов в пачке) соединены с соответствующими входами детектора пачек одноименных символов, детектор максимальной величины, группу ключей, выходы которых соединены с соответствующими входами интегратора, выход которого подключен к второму входу компаратора, о тл и ч а ю щ и й с я тем, что, с целью повышения помехозащищенности дельта- кодера, в него введены цифровой сумматор,буферный регистр, группа элементов НЕ, источник логической единицы, элемент задержки и элемент НЕ, вход которого подключен к выходу первого разряда регистра 5 сдвига, выход элемента НЕ соединен с информационными входами всех ключей группы, вход элемента задержки подключен к тактовому входу дельта-кодера, выход элемента задержки соединен с тактовым вхо дом буферного регистра, выходымладшихразрядов которого ( - положительное целое число) подключены к входам младших разрядов первой группы входов цифрового сумматора, выходы 1 старших разрядов 15 буферного регистра 1 - положительное целое число; К+ - разрядность буферного регистра) соединены с входами 1 старших разрядов первой группы входов цифрового сумматора, управляющими входами соот ветствующих ключей группы, входами детектора максимальной величины и входами элементов НЕ группы, выходы которых подключены к входам К младших разрядов второй группы входов цифрового сумматора, 25 выход детектора максимальной величинысоединен с (в+1)-м входом детектора пачек одноименных символов, выход которого подключен к входам Кстарших разрядов второй группы входов цифрового суммато ра, вход переноса и входы остальных разрядов второй группы входов которого подключены к выходу источника логической единицы, выходы цифрового сумматора соединены с одноименными информационны ми входами буферного регистра.

СмотретьЗаявка

4778643, 08.01.1990

ЦЕНТРАЛЬНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ СВЯЗИ

БУЗДАЛИНА ИРИНА АЛЕКСАНДРОВНА, ГЕБЕРГЕР ГЕНРИХ ХАЙМОВИЧ, УГЕР ВЛАДИМИР ГЕОРГИЕВИЧ, ХЕЙФЕЦ ДМИТРИЙ ЛЬВОВИЧ

МПК / Метки

МПК: H03M 3/02

Метки: адаптивный, дельта-кодер

Опубликовано: 15.06.1992

Код ссылки

<a href="https://patents.su/4-1741265-adaptivnyjj-delta-koder.html" target="_blank" rel="follow" title="База патентов СССР">Адаптивный дельта-кодер</a>

Предыдущий патент: Интегрирующий преобразователь тока в код

Следующий патент: Преобразователь постоянного напряжения в постоянное

Случайный патент: Приспособление к бандуре