Устройство для коррекции программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1647574

Автор: Улыбин

Текст

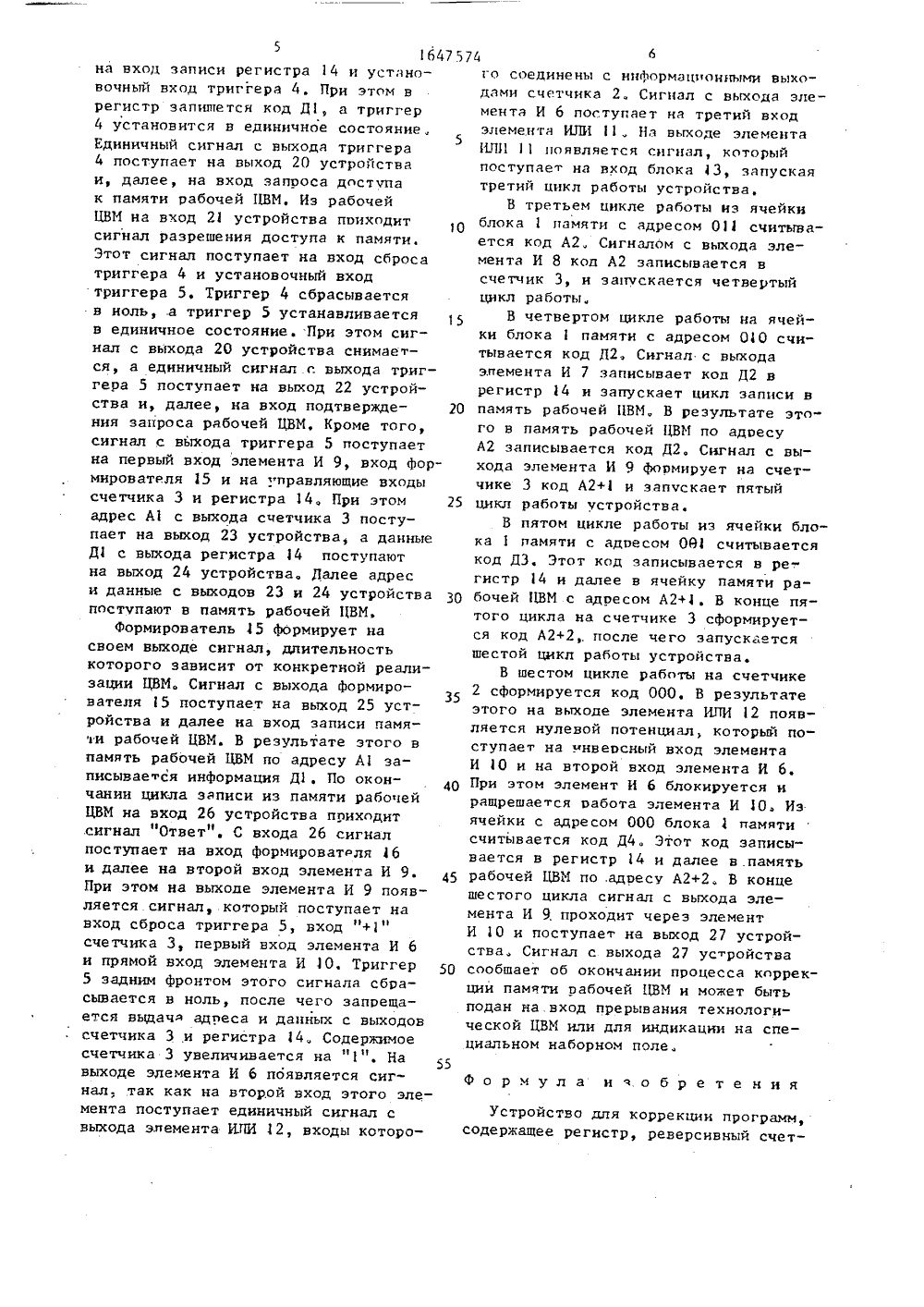

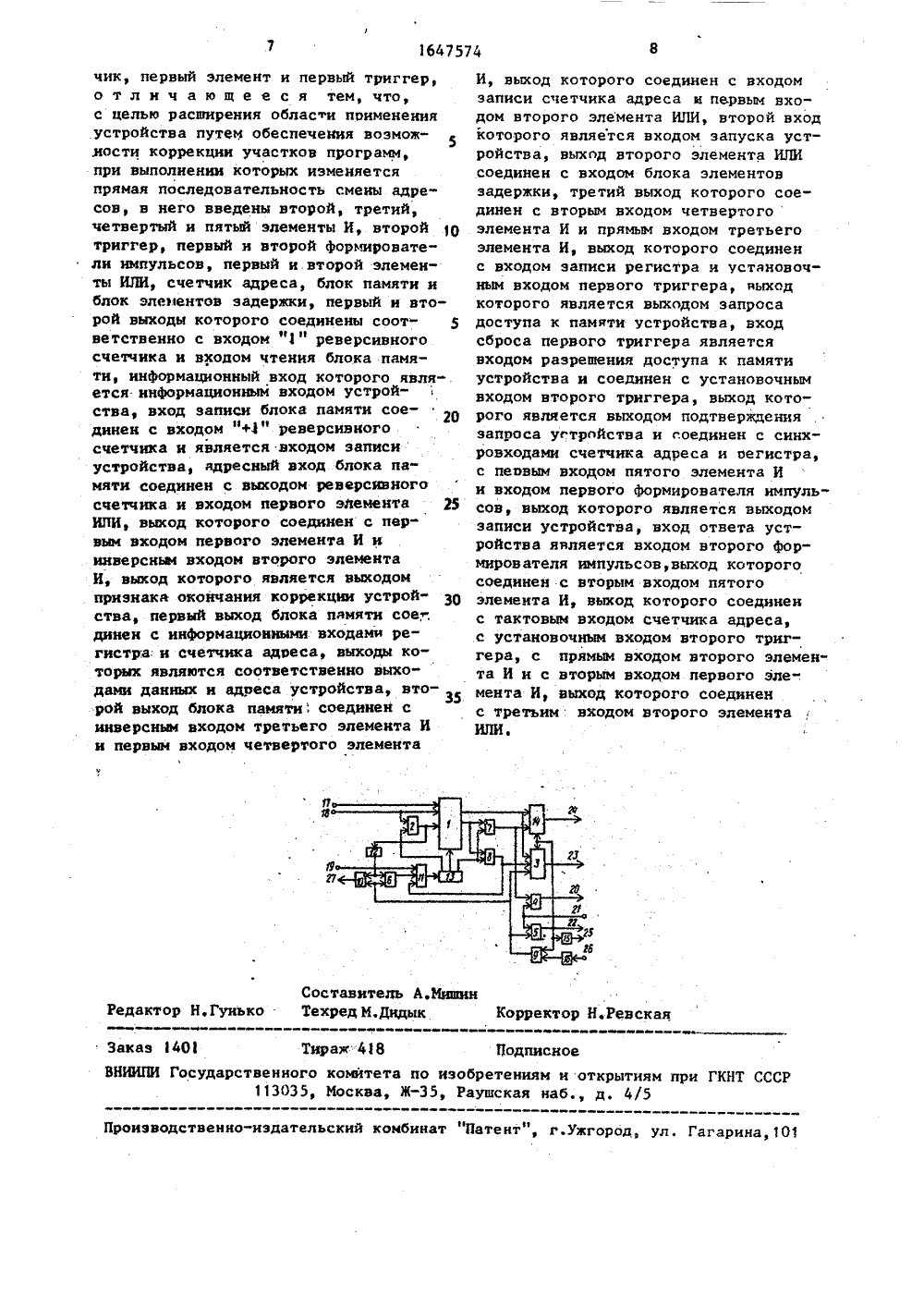

С 06 Г 1 ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ П(НТ СССР ИЗОБРЕТЕНИЯ3 ИДЕТЕЛЬСТВУ ПИС ВТОРСН учно-производствен применения микротизации в машиносвидетельство СССР С 06 Р 11/28, 1984.видетельство СССР С 06 Р 11./28, 1985,О ДЛЯ КОРРЕКЦИИ ПРО(57) Изобретение относи лительной технике и мож пользовано для коррекци ЦВТ. Цель изобретения -ся к вычис т бьть испрограммырасширение . Изобретение тельной техникетносится к вычи и может быть исп кции программ ЦВ ения является ра именения за счет л 3 элеменервый 15 ро ьвано для корре Целью изобрет ние области пр ши 8 выходвход 21выхододыход 25д 27 обеспечения возмучастков програторых ивменяетсность смены адре ожносмм, пр коррекцивыполнении коель. Р 2 2 прям оследо На чер ная схема Устрой содержит счетчик 2еже представле рукт з устроиства. ство для кор блок 1 памятсчетчик 3 й 5 триггеры четвертый 8 элементы И,екции программреверсивныйдреса, первыйпервый б,пятый 9 ипервый 11 и втои вто третий 7второй 10 устроистзим.(71) Ульяновский наный комплекс "Центрэлектроники и автомастроении"(54) УСТРОЙСТВ области применения за счет обеспечения возможности коррекции участковпрограммы, при выполнении которыхизменяется прямая последовательностьсмены адресов. Указанная цель достигается тем, что в устройства введены со второго по пятый элементы И,счетчик адреса, второй триггер, дваформирователя импульсов, два элемента ИЛИ, блок памяти и блок элементов задержки. Введенные элементыпозволяют корректировать программыв памяти ЦВТ, не останавливая ее работы, например, в ходе "прогона".,Причем реализуется возможность коррекции выборочных участков программ,необходимость чего возникает при наличии в программе команд перехода,1 ил 1 табл,12 элементы ИЛИ, блокзадержки, регистр 14, иторой 16 формирователи импуормационный вход 17, входта записи, вход 19 запусказапроса доступа к памяти,решения доступа к памяти,подтверждения запроса, выхадреса, выход 24 данных, виси, вход 26 ответа и выхознака окончания коррекции. Устройство работает в двух режиАдреса ячеек блока 1 па- мяти Содержимое ячеек блокапамяти35 Младшие разряды Старшийразряд Д 4 Д 3 Д 2 А 2 Д 4 А 1 ООО 001 010 011 100101 0 О ОО П р и и е ч а н и е. А 1,А 2 - двоичныекоды адресов ячеек памяти рабочей ЦВМ, информацию в которыхнадо откорректировать; Д 1, Д 2,ДЗ, Д 4 - двоичные кбды корректировочной информации.Двоичные коды адоесов А 1 и А 2 отличаются один от другого более чем на "1", В результате коррекции в ячейку памяти рабочей ЦВМ с адоесои А 1 должна быть записана инФормация Д 1, а в ячейку с адоесом А 2 и следующие эа ней две ячейки (то есть ячейВ исходном состоянии .1 цепи установки в исходное состояние не показлны)счетчик 2 и триггеры 4 и 5 обнулены.На входы 17. и 18 устройства из тех 5нологической ЦВМ (или с тумблеров икнопки специального наборного поли)подаются соответственно корректировочная информация и сигнал записи.С входа 18 сигнал поступает на входтакта записи олсона 1 памяти. Приэтом в ячейку блока 1 памяти, адрескоторой с информационного выходасчетчика 2 поступает на адресный входблока 1 памяти, записывается инфор"мация, приходящая на информационныйвход блока 1 памяти с входа 17 устрой,ства, Кроме того, сигнал с входа 18поступает на вход "+1 " счетчика 2 изадним Фронтом увеличивает его содержимое на единицу.Таким образом, в режиме "Подготовка" обеспечивается последовательноезаполнение ячеек блока 1 памяти.По окончании заполнения блока 25памяти счетчик 2 содержит увеличенныйна единицу адрес последней заполненной ячейки,В результате выполнения режима"Подготовка" в блок 1 памяти должнабыть записанд инФормация, данные которой приведены в таблице,ки с адресами А 2+1 и Л 2+2) должныбыть записаны коды Д 2, ДЗ и Д 4 соответственноно,После окончания заполнения блока1 памяти из технологической ЦВМ (илис кнопки специального наборного поля)на вход 19 устройства поиходит сигнал . По этому сигналу устройство начинает работу в режиме КоррекцияВ режиме иКоррекция устройствоработает следующим образомС входа 19 сигнал поступает на первый вход элемента ИЛИ 11, При этомна выходе элемента ИЛИ 11 появляется сигнал, который поступает на входблока 13 элементов задержки. Блок3имеет три выхода, на которых последовательно вырабатываются единичныесигналы.Сигнал с первого выхода блока 13поступает на вход "-1" счетчика 2,после чего на счетчике 2 формируется адоес последней заполненной ячейки блокапамяти для приведенногопримера - адрес 101 ).Сигнал с второго выхода блока 13поступает на вход такта чтения блока1 памяти, При этом на выходе блокапамяти появится информация, хранящаяся в ячейке с адресом 101. Младшиеразряды информации (А 1) с выхода блока 1 памяти поступают на информационные входы счетчика 3 и регистра 14.Старший разояд информации (и ") свторого выхода блока 1 памяти поступает на инверсный вход третьего элемента И 7, блокируя его, и на первыйвход четвертого элемента И 8.Сигнал с третьего выхода блока 13поступает нй прямой вход элемента 7и второй вход элемента 8. При этомна выходе элемента 8 появляется сигнал, который поступает на вход тактазаписи счетчика 3 Этот же сигналпоступает на второй вход элементаИЛИ 1 1, на выходе которого появляется сигнал, .поступающий на вход блока 13, запуская второй цикл работыустройства.Сигнал с пеового выхода блока 13сформирует на счетчике 2 адрес 100.Сигнал с второго выхода блока 13считает из блока 1 памяти информацию,содержащую в старшем разряде "О", ав младших - Д 1,Сигнал с третьего выхода блока 13пройдет через элемент И 7 и поступит25 40 164757на вход записи регистра 4 и устано -вочный вход триггера 4, Лри этом врегистр запишется код Д 1, а триггер4 установится в единичное состояние,5Единичный сигнал с выхода триггера4 поступает на выход 20 устройстваи, далее, на вход запроса доступак памяти рабочей ЦВМ. Из рабочейЦВМ на вход 21 устройства приходитсигнал разрешения доступа к памяти.Этот сигнал поступает на вход сбросатриггера 4 и установочный входтриггера 5. Триггер 4 сбрасываетсяв ноль, а триггер 5 устанавливаетсяв единичное состояние. При этом сигнал с выхода 20 устройства снимается, а единичный сигнал .с выхода триггера 5 поступает на выход 22 устройства и, далее, на вход подтверждения запроса рабочей ЦВМ, Кроме того,сигнал с выхода триггера 5 поступаетна первый вход элемента И 9, вход формирователя 15 и на управляющие входысчетчика 3 и регистра 14. При этомадрес А 1 с выхода счетчика 3 поступает на выход 23 устройства, а данныеД 1 с выхода регистра 14 поступаютна выход 24 устройства. Далее адреси данные с выходов 23 и 24 устройствапоступают в память рабочей ЦВМ,Формирователь 15 формирует насвоем выходе сигнал, длительностькоторого зависит от конкретной реализации ЦВМ. Сигнал с выхода формиро 35вателя 5 поступает на выход 25 устройства и далее на вход записи памяти рабочей ЦВМ. В результате этого впамять рабочей ЦВМ по адресу А 1 записывается информация Д 1 . Ло окончании цикла записи из памяти рабочейЦВМ иа вход 26 устройства приходит.сигнал "Ответ". С входа 26 сигналпоступает на вход формирователя 16и далее на второй вход элемента И 945При этом на выходе элемента И 9 появляется сигнал, который поступает навход сброса триггера 5, вход "+"счетчика 3, первый вход элемента И 6и прямой вход элемента И 10. Триггер5 задним фронтом этого сигнала сбрасывается в ноль, после чего запрещается выдача адреса и данных с выходовсчетчика 3 и регистра 14, Содержимоесчетчика 3 увеличивается на "1". Навыходе элемента И 6 появляется сигнал., так как на второй вход этого элемента поступает единичный сигнал свыхода элемента ИЛИ 12, входы которо 46го соединены с информационными выходами счетчика 2. Сигнал с выхода элемента И 6 постугает на третий входэлемента ИЛИ. На выходе элементаИЛЛ 11 появляется сигнал, которыйпоступает иа вход блока 13, запускаятретий цикл работы устройства,В третьем цикле работы из ячейкиблока 1 памяти с адресом 011 считывается код А 2. Сигналом с выхода элемента И 8 код А 2 записывается всчетчик 3, и запускается четвертыйцикл работыВ четвертом цикле работы на ячейки блокапамяти с адресом 010 считывается код Д 2. Сигнал с выходаэлемента И 7 записывает код Д 2 врегистр 14 и запускает цикл записи впамять рабочей ЦВМ, В результате этого в память рабочей ЦВМ по адресуА 2 записывается код Д 2. Сигнал с выхода элемента И 9 формирует на счетчике 3 код А 2+1 и запускает пятыйцикл работы устройства,В пятом цикле работы из ячейки блока 1 памяти с адресом 061 считываетсякод ДЗ. Этот код записывается в регистр 14 и далее в ячейку памяти рабочей ВМ с адресом А 2+1 . В конце пятого цикла на счетчике 3 сформируется код А 2+2. после чего запускаетсяшестой цикл работы устройства.В шестом цикле работы на счетчике2 сформируется код 000. В результатеэтого на выходе элемента ИЛИ 12 появляется нулевой потенциал, который поступает на инверсный вход элементаИ 10 и на второй вход элемента И 6,При этом элемент И б блокируется иращрешается работа элемента И 1 О. Изячейки с адресом 000 блока 1 памятисчитывается код Д 4. Этот код записывается в регистр 4 и далее в .памятьрабочей ЦВМ по .адресу А 2+2. В концешестого цикла сигнал с выхода элемента И 9, проходит через элементИ О и поступает на выход 27 устройства Сигнал с выхода 27 устройствасообшает об окончании процесса коррекции памяти рабочей ЦВМ и может бытьподан на.вход прерывания технологической ЦВМ или для индикации на специальном наборном поле.Формула изобретенияУстройства для коррекции программ,содержащее регистр, реверсивный счет.Ревская Коррек Заказ 40 Тираж"418 ПодписноеВНИИПИ Государственного комитета по изобретениям н открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 роизводственно-издательский комбинат "Патент", г,ужгород, ул. Гагарина,чик, первый элемент и первый триггер, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства путем обеспечения возмож 5 ,ности коррекции участков программ, при выполнении которых изменяется прямая последовательность смены адре" сов, в него введены второй, третий, четвертый и пятый элементы И, второй 10 триггер, первый н второй формирователи импульсов, первый и второй элементы ИЛИ, счетчик адреса, блок памяти и блок элементов задержки, первый н второй выходы которого соединены соот ветственно с входом "1 " реверсивного счетчика и входом чтения блока памяти, информационный вход которого явля-. ется информационным входом устройства, вход записи блока памяти соединен с входом "+4" реверсивного счетчика и является входом записи устройства, адресный вход блока памяти соединен с выходом реверсивного счетчика и входом первого элемента 25 ИЛИ, выход которого соединен с первым входом первого элемента И и инверсньи входом второго элемента И, выход которого является выходом признака окончания коррекции устройства, первый выход блока памяти сое,", дииен с информационными входами регистра:и счетчика адреса, выходы которых являются соответственно выходами данных и адреса устройства, вто рой выход блока памяти, соединен с инверсным входом третьего элемента И и первым входом четвертого элемента И, выход которого соединен с входомзаписи счетчика адреса и первым входом второго элемента ИЛИ, второй входкоторого является входом запуска устройства, выход второго элемента ИЛИсоединен с входом блока элементовзадержки, третий выход которого соединен с вторым входом четвертогоэлемента И и прямым входом третьегоэлемента И, выход которого соединенс входом записи регистра и установочным входом первого триггера, выходкоторого является выходом запросадоступа к памяти устройства, входсброса первого триггера являетсявходом разрешения доступа к памятиустройства и соединен с установочнымвходом второго триггера, выход которого является выходом подтверждениязапроса устройства и соединен с синхровходамн счетчика адреса и оегистра,с пеовым входом пятого элемента Ии входом первого формирователя импульсов, выход которого является выходомзаписи устройства, вход ответа устройства является входом второго формирователя импульсов, выход которогосоединен с вторым входом пятогоэлемента И, выход которого соединенс тактовым входом счетчика адреса,с установочным входом второго триггера, с прямым входом второго элемента И и с вторым входом первого эле-.мента И, выход которого соединенс третьим: входом второго элементаИЛИ.

СмотретьЗаявка

4699060, 05.04.1989

УЛЬЯНОВСКИЙ НАУЧНО-ПРОИЗВОДСТВЕННЫЙ КОМПЛЕКС "ЦЕНТР ПРИМЕНЕНИЯ МИКРОЭЛЕКТРОНИКИ И АВТОМАТИЗАЦИИ В МАШИНОСТРОЕНИИ"

УЛЫБИН СЕРГЕЙ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 11/28

Опубликовано: 07.05.1991

Код ссылки

<a href="https://patents.su/4-1647574-ustrojjstvo-dlya-korrekcii-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для коррекции программ</a>

Предыдущий патент: Устройство для контроля последовательностей импульсов

Следующий патент: Устройство памяти телевизионного типа

Случайный патент: Выходной узел тестера для контроля электронных блоков