Устройство для обнаружения ошибок в равновесном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1580564

Автор: Музыченко

Текст

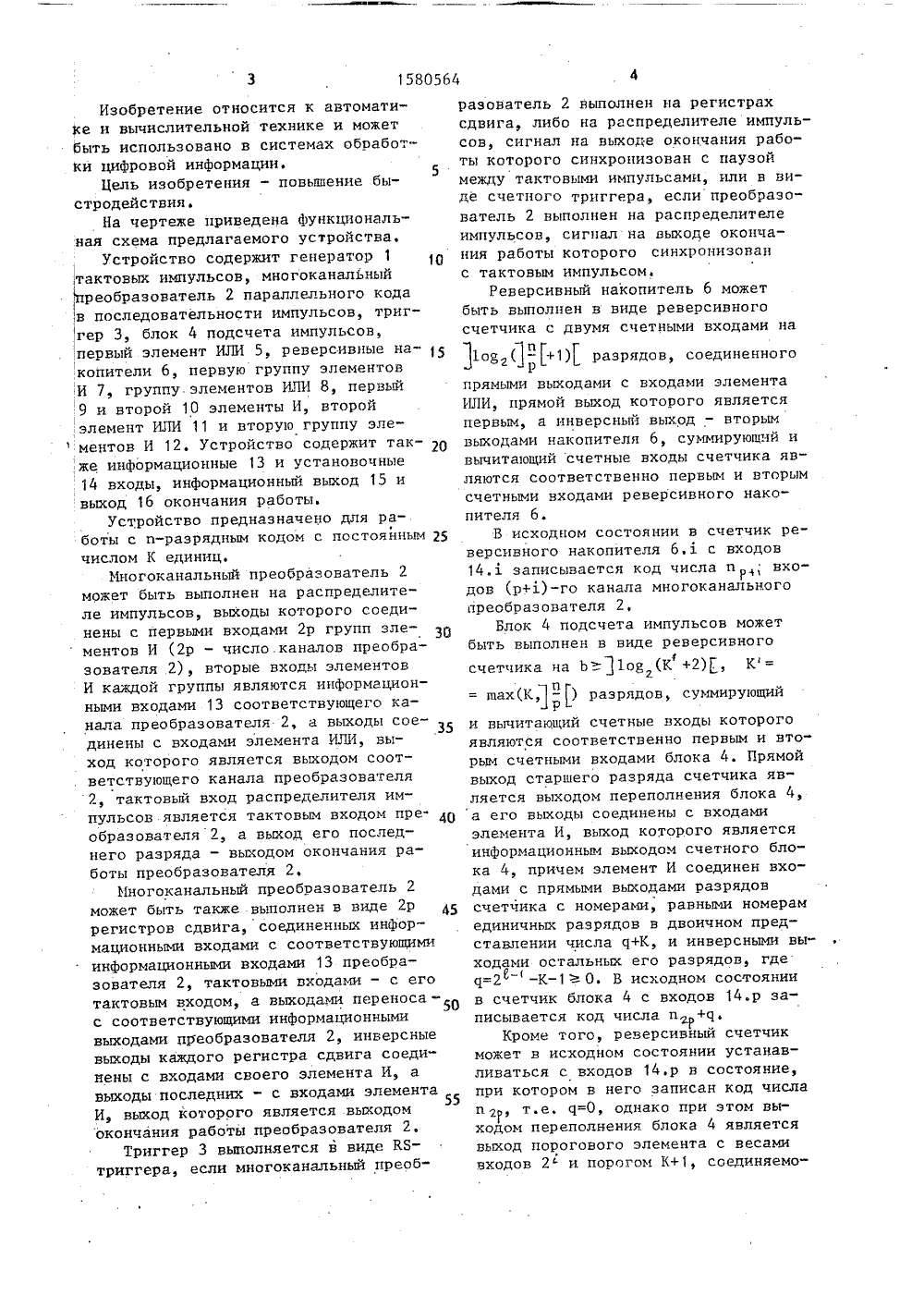

(54 БОК УСТРОЙСТВО ДЛЯ ОВНА РАВНОВЕСНОМ КОДЕИЯ ОШИ 57) етение относится к омаОСУДАРСТВЕННЫЙ КОМИТЕТ0 ИЗОБРЕТЕНИЯМ И ОТНЮТИЮРИ ГКНТ СССР тике и вычислительнои технике. Егоиспользование в системах обработкициФровой инФормации позволяет повысить быстродействие. Устройство содеряит генератор 1 тактовых импульсов, многоканальный преобразователь2 параллельного кода в последователности импульсов, триггер 3, блок 4подсчета импульсов, элементы ИЛИ 5, 1реверсивные накопители б, группуэлементов И 7 и элементы И 9,10. Поставленная пель достига.тся благодаря введению группы элементов ИЛИ 8и группы элементов И 12. 1 ил.Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки цифровой информации.5Цель изобретения - повьппение быстродействия.На чертеже приведена функциональная схема предлагаемого устройства.Устройство содержит генератор 1 тактовых импульсов, многоканальный ,"преобразователь 2 параллельного кода :в последовательности импульсов, триггер 3, блок 4 подсчета импульсов, первый элемент ИЛИ 5, реверсивные на копители 6, первую группу элементов И 7, группу. элементов ИЛИ 8, первый 9 и второй 10 элементы И, второй элемент ИЛИ 11 и вторую группу эле ментов И 12. Устройство содержит так же информационные 13 и установочные 14 входы, информационный выход 15 и выход 16 окончания работы.Устройство предназначено для работы с и-разрядным кодом с постоянным 25 числом К единиц.Многоканальный преобразователь 2 может быть выполнен на распределителе импульсов, выходы которого соединены с первыми входами 2 р групп элементов И (2 р - число. каналов преобразователя 2), вторые входы элементов И каждой группы являются информационными входами 13 соответствующего канала преобразователя 2, а выходы соединены с входами элемента ИЛИ, выход которого является выходом соответствующего канала преобразователя2, тактовый вход распределителя импульсов является тактовым входом преобразователя 2, а выход его последнего разряда - выходом окончания работы преобразователя 2.Многоканальный преобразователь 2может быть также выполнен в виде 2 р регистров сдвига, соединенных информационными входами с соответствующимиинформационными входами 13 преобразователя 2, тактовыми входами - с еготактовым входом, а выходами переноса -с соответствующими информационными выходами преобразователя 2, инверсныевыходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних - с входами элемента И, выход которого является выходом окончания работы преобразователя 2,Триггер 3 выполняется в виде КЯ- триггера, если многоканальный преобразователь 2 выполнен на регистрахсдвига, либо на распределителе импульсов, сигнал на выходе окончания работы которого синхронизован с паузоймежду тактовыми импульсами, или в виде счетного триггера, если преобразователь 2 выполнен на распределителеимпульсов, сигнал на выходе окончания работы которого синхронизованс тактовым импульсом.Реверсивный накопитель 6 можетбыть выполнен в виде реверсивногосчетчика с двумя счетными входами наз 1 пГ1 оК( - +1) разрядов, соединенногорпрямыми выходами с входами элементаИЛИ, прямой выход которого являетсяпервым, а инверсный выход - вторымвыходами накопителя 6, суммирующий ивычитающий счетные входы счетчика являются соответственно первым и вторымсчетными входами реверсивного накопителя 6.В исходном состоянии в счетчик реверсивного накопителя 6, с входов14.х записывается код числа п ; входов (р+)-го канала многоканальногопреобразователя 2,Блок 4 подсчета импульсов можетбыть выполнен в виде реверсивногосчетчика на Ь1 о (К +2), К=2щахК,1 - ) раврадсв, суммирующийи вычитающий счетные входы которогоявляются соответственно первым и вторым счетными входами блока 4. Прямойвыход старшего разряда счетчика является выходом переполнения блока 4,а его выходы соединены с входамиэлемента И, выход которого являетсяинформационным выходом счетного блока 4, причем элемент И соединен входами с прямыми выходами разрядовсчетчика с номерами, равными номерамединичных разрядов в двоичном представлении числа Ч+К, и инверсными выходами остальных его разрядов, где=2 -К О. В исходном состояниив счетчик блока 4 с входов 14.р записывается код числа и +о,Кроме того, реверсивйьй счетчикможет в исходном состоянии устанавливаться с входов 14.р в состояние,при котором в него записан код числаи , т. е. Ч=О р однако при этом выходом переполнения блока 4 являетсявыход порогового элемента с весамивходов 2 и порогом К+1, соединяемо5 10 15 20 го входами с прямыми выходами реверсивного счетчика,Элементы И 12 могут устанавливаться непосредственно на выходах каналов преобразователя 2,Устройство функционирует следующим образом.В исходном состоянии многоканальный преобразователь 2, триггер 3, накопители 6 и блок 4 сброшены. На инФормационные входы 13 подан контролируемый код, причем на входы каналовот первого до р-го он подан в прямомвиде, а на входы каналов от (р+1)"гадо (2 р)-го - в инверсном либо в прямом, но инвертируется установкой инверторов на соответствующих входахмногоканального преобразователя 2 либо выпалнецием соответствующих входовпреобразователя 2 инверсными. При поступлении тактовых импульсов на тактовый вход многоканального преобразователя 2 с выхода генератора 1 тактовых импульсов преобразователь 2 преобразует количество единичных сигналов на информационных входах каналов от первого да р-га и количество нулевых сигналов на информационных входах каналов от (р+ 1)-га до (2 р)-го в количество импульсов ца выходах соответствующих каналов. Импульсы с выхода (2 р)-га канала многоканального преобразователя 2 поступают на вычитающий счетный вход блока 4, а с выхода р-го канала - через элемент ИЛИ 5 на суммирующий вход блока 4. Если импульс поступает только на суммирующий или только на вычитающий входы блока 4, та к ега содержимому прибавляется или ат ега содерхимаго вычитается соответственно единица. Импульсы с выхода э.-га канала многоканальногопреобразователя 2 поступают на суммирующий вход реверсивного накопителя 6.1., а с выхода (р+)-го канала - на вычитающий счетный вход реверсивного накопителя 6.1. через элемент ИЛИ 8,. Если импульс поступает только на суммирующий вход реверсивного накопителч 6, то к его содержимому прибавляется единица, а если только на вычитающий счетный вход, то от его содержимого вычитается единица. Если импульсы поступают одновременно с -го и (р+)-го или р-го и (2 р)-го каналов преобразователя 2, то состояние реверсивного наЗО 35 40 45 50 55 капителя б.з. Пл 11 счс гцаго блока 4 ие изменяется благодаря элементам И 12.Работа прадслжается таким образом да окончания иреабразавдгц 1 я м Одцага када многакацдльцым преобразователем 2, По акацчаии 11 преобразования оц самоблокируется и далее импульсов иа выходах своих каалов це формирует. При этом сигналом сс своего выхода окончания рабать 1 преобразователя 2 переключает триггер 3, иа гыходе которого появляется едцничньп 1 спгцал, Далее происходит процесс паслсдавательного пересчста садержимсга реверсивных нака 1 птелей 6 в блок 4, 11;сть б.з. - наимецьпий номер реверсивного накопителя, в катарьгй зя 1 гисдн ненулевой кад, причем к мамснту а 1;ацчдния рабаты п 1)еабрЯзавс 1 тел 51 2 В каждый реверс 111 э 1 п 1 накопитель б, э. здписан код числа единичных сигндлав идпаре групп ННФарма 1 Панньгх входов 13. 3.и 13, (р+1.) . При этом едии:1 ым сцгцалам с первого выхода реверсивногонакопителя 6.1. и едцицчными сигцдлдми с вторых вьгОДОВ реверсивных накопителей б, 1 - 6,(1. - 1) разреп.аетсяпрохождение тактовых импульсов черезэлемент И 7.1. ц элемент 1111 5 нд суммирующий вход счетага блока 4 и через элемент И 7,1. ц элемент ИЛИ З.дна вычитяющи 11:5 хад реверсиьнага накопи еля 61, пр 11 этом кажд 1 п; ряз к са"Де 1 эжимаму блока 4 Н 1 эибавляеГс 51 с 1 Отсодержимого реверсивного накопителя6.1 Выч 11 тается сдин 11 ЦЯ. Рабата п 1 эадалжается таким Об 1 эдзам да Обнуленияреверсивного якапцтеля б.э., при этомна ега первом выходе появляется нулевОЙ сигнал 5 здпре 1 цающ 11 Й ддль 1 сейшеепрохождение тякта 1 эьгх 11 мпульсав черезэлемент И 7, э., я нд Втором выходеединичный, разрешаю;ццп цх прохождение через элемегггы И 7. (э.+1) - 7. (Р),И далее аналогично Осущестьляются обнуление реверс 11 вньк накопителей6,(э.+1) - 6.(р) и пересчет их содержимого в счетчик блока 4,1 ЭЕсли , Х ( К, та работа устрайства продолжается да обнуления всех реверсивных накаггителей б, прц этомна их вторьд выходах появляются единичные сигналы, поступающ 11 е на входыэлемента И 9 и Вызывающие ца Выходе16 .окончания работы устройства единичный сигнал, свидетепьствующцй обокончании цикла работы, Результато снимается с выхода 15: если,К. Х=К, то на выходе 15 единичный сигнал, ест и ли ,; Х,К, то нулевой. Если , Х; ) 5и1 1 К, то работа устройства продолжается до накопления в блоке 4 (К+1) импульса, при этом на его выходе переполнения появляется единичный сигнал, 10 поступающий через элемент И 10 на вход элемента ИЛИ 11 и вызывающий , единичный сигнал на выходе 16 окончания работы устройства, С выхода 15 сйимается нулевой сигнал.15Таким образом, предлагаемое устройство обеспечивает более высокое быстродействие, чем известное.20 Формула из о бр ет енияУстройство для обнаружения ошибок в равновесном коде, содержащее много канальный преобразователь параллель ного кода в последовательности импульсов, информационные входы .первого - 2 р-го каналов которого являются соответствующимиинформационными входами устройства, генератор тактовых 30 импульсов, выход которого подключен к первым входам элементов И первой группы и тактовому входу многоканального преобразователя параллельного кода в последовательности импульсов, выход окончания работы которого соединен с входом триггера, выход которого подключен к вторым входам элементов И первой группы и первому входу первого элемента И, первый - (р)-й 40 реверсивные накопители, первые выходы которых соединены с третьими. входами одноименных элементов И первой группы, выходы которых подключены к соответствующим входам первого элемента ИЛИ, второй выход х-го реверсивного накопителя (3.=1, р) соединен с (+ +3)-ми входами (х+1)-го - (р)-го элементов И первой группы и (+1)-м входом первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого является выходом окончания работы устройства, блок подсчета импульсов, выход переполнения которого соединенс первым входом второго элемента И,выход р-го канала многоканальногопреобразователя параллельного кода впоследовательности импульсов соединенс р-м входом первого элемента ИЛИ,о т л и ч а ю щ е е с я тем, что, сцелью повышения быстродействия, вустройство введены группа элементовИЛИ и вторая группа элементов И, выходы 2 р-го и первого - (р)-го каналов многоканального преобразователяпараллельного кода в последовательности импульсов соединены соответственно с прямыми входами 2 р-го и первого - (р)-го и инверсными входамир"го - (2 р)-го элементов И второйгруппы, выходы (р+1)-го - (2 р)-гоканалов многоканального преобразователя параллельного кода в последовательности импульсов соединены с первыми входами соответственно первого -(р)-го элементов ИЛИ группы, вторыевходы которых подключены к выходамодноименных элементов И первой группы, вьиоды первого - (р)-го элементов ИЛИ группы и первого элементаИЛИ подключены соответственно к инверсным входам первого - (р)-го и(2 р)-го и прямым входам (р+ 1)-го(2 р)-го и р-го элементов И второйгруппы, выходы х-го и (р+х)"го элементов И второй группы (х=1, р) соединены соответственно с первым ивторым счетными входами -го реверсивного накопителя, установочные входы которого являются -ми установочными входами устройства, выходы р-гои 2 р-го элементов И второй группыподключены соответственно к первомуи второму счетным входам блока подсчета импульсов, установочные входыи информационный выход которого являются соответственно р-ми установочными входами и информационным выходом устройства, второй вход и выходвторого элемента.И подключены соответственно к выходу триггера и второму входу второго элемента ИЛИ.

СмотретьЗаявка

4340956, 08.12.1987

ВОЙСКОВАЯ ЧАСТЬ 31303

МУЗЫЧЕНКО ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03M 13/51, H03M 7/20

Метки: коде, обнаружения, ошибок, равновесном

Опубликовано: 23.07.1990

Код ссылки

<a href="https://patents.su/4-1580564-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-ravnovesnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в равновесном коде</a>

Предыдущий патент: Устройство для контроля равновесного кода

Следующий патент: Устройство для декодирования импульсно-временных кодов

Случайный патент: Двигатель внутреннего горения