Устройство для сопряжения управляющей и управляемых вычислительных машин

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

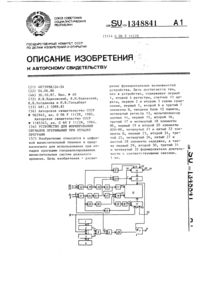

(57) Излительнпользов О ДЛЯ СОПРЯЖЕНИЯ УПРАВЛЯЕМЫХ ВЫЧИ сится к вычисожет быть исения высокопро е от и тех но дл ке пос ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГННТ СССР А ВТОРСКОМУ СВИДЕТЕЛЬСТ(71) Специальное конснологическое бюро Физкого института им. Г,(56) Авторское свидетУ 533928, кл. С 06 ГАвторское свидетелУ 808194, кл. С 06 Г 8015170 иэводительных многомашннньм вычислительных систем. Целью изобретенияявляется расширение функциональныхвоэможностей устройства эа счет исключения случаев блокировки низкоприоритетных управляемых вычислительных машин. Поставленная цельдостигается путем введения М триггеров 7, арбитра 8, элемента ИЛИ 9, Мэлементов И 16, М счетчиков 17, Мблоков сравнения 18 и шифратора 20,что позволяет осуществлять обслуживание запросов управляемых вычислительных машин в соответствии с их приоритетами, очередностью поступлениязапросов на обслуживание, длинойсформировавшейся очереди и временеможидания обслуживания, т.е. реализовать гибкую систему распределенияресурсов, 1 ил.35 Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизво 5дительных многомашинных вычислительных систем,Целью изобретения является расширение функциональных возможностейустройства за счет исключения случаевблокировки низкоприоритетных управляемых вычислительных мапин,На чертеже приведена структурнаясхема предлагаемого устройства.Устройство содержит регистр 1 приращения, коммутатор 2, регистр 3 15управления, дешифратор 4, М блоков 5элементов И, М управляемых вычислительных машин 6, М триггеров 7, арбитр 8, элемент ИЛИ 9, М узлов 10Формирования сигналов состояния, сос.риггера 12 запроса, регистра 13 состояния, первого блока 14 сравнения,группы 15 элементов И, элементаИ 16, реверсивного счетчика 17 и второго блока 18 сравнения, элементИЛИ 19, шифратор 20, группу 21 элементов ИЛИ, группу 22 элементов И,выход 23 настройки, выход 24 строба,информационный вход 25, адресныйыход 26, информационный выход 27,ход 28 запроса, выход 29 кода опрос., вход 30 состояния, вход 31 номера ЭВ и выход 32 разрешения управляющей вычислительной машины 33.Устройство работает следующимобразом.В начале работы триггеры 7, триггеры 12 запроса, регистры 13 состояния и реверсивные счетчики 17 находят ся в нулевом состоянии, что свидетельствует об отсутствии запросов наобмен информацией со стороны управляемых вычислительных машин 6. В регистрах 1 постоянно хранятся коды 45номеров вычислительных машин 6, указывающие на приоритетность машин 6 вс.пстеме, причем эти коды в процессеФункционирования системы могут меняться управляющей вычислительной машиной 33 (цепи установки кодов иначальной установки не показаны),Обмен информацией по инициативе вычислительной машины 33 осуществляетсяследующим образом.Команда настройки заносится в регистр 1 приращений по выходу 23. Состояние регистра 1 определяет режимработы вычислительной машины 33 с оперативной, памятью вычислительной машины 6. Информация о состояния регистра 1 через коммутатор 2 в промежутки времени, определяемые подачей вычислительной машины 33 стробирующих сигналов с выхода 24, записывается в регистр 3 управления, Сигнал выборки на соответствующем выходе дешифратора 4 разрешает прохождение данных через элементы И блока 5 и, тем самым, связь между вычислительной машиной 33 и требуемой вычислительной машиной 6. При этом код адреса обращения с выхода 26 вычислительной машины 33 поступает через элементы И блока 5 в регистр адреса оперативной памяти выбранной вычислительной машины 6. Одновременно элементы И блока 5 обеспечивают передачу синхронизирующих сигналов и управляющей информации с выхода 27 вычислительной машины 33 на вычислительную машину 6, а также поступление данных с выхода вычислительной машины 6 на вход 25 вычислительной машины ЗЗ.При обмене. информацией по инициативе вычислительной машины 6 в целях устранения блокировки запросов с низкими приоритетами и устранения конфпиктных ситуаций устройство формирует очередь заявок и предоставляет информацию о ней управляющей вычислительной машине 33.Поступающие от вычислительной машины 6 сигналы требований на обмен устанавливают соответствующие триггеры 7 в единичное состояние. Одновременно в регистры 13 состояния соответствующих узлов 10 заносятся коды операций обмена (решена очередная задача, требование ввода-вывода информации, сигналы от системы контроля вычислительной машины 6 и др). Триггеры 7 и арбитр 8 служат для устранения конфликтной ситуации при одновременном поступлении нескольких запросов от различных машин 6. Зафиксированные триггерами 7 запросы поступают на арбитр 8, который определяет наиболее приоритетный иэ них и устанавливает соответствующий триггер 12 в единичное состояние, Это вызывает сброс соответствующего триггера 7, разрешая тем самым арбитру 8 дальнейшее обслуживание менее приоритетных запросов. Кроме того, сигнал с выхода триггера 12 поступает череззапроса соответствует большее значение содержимого соответствующего счетчика 17Обслуживание запросов на обмен управляющей вычислительной машиной 33 производится следующим образом. По сигналу с выхода элемента ИЛИ 19, свидетельствующему о наличии запросов от вычислительной машины 6, вычислительная машина 33 опрашивает регистры 13 состояния путем поочередной подачи по выходу 29 кодов опроса, равных номерам вычислительных машин 6, на выходы блоков 14сравнения узлов 10. В случае совпаде 30 35 40 5 151703элемент ИЛИ 19 на вход 28 вычислительной машины 33, указывая тем самым наналичие запроса. Информация о количестве поступивших запросов определяется шифратором 20, а об очереднос"5 ти их поступления регистрируется реверсивными счетчиками 17 узлов 10.Информация об очередности поступления запросов от вычислительной ма шины 6 формируется на счетчиках 17 следующим образом. В исходном состоянии содержимое всех счетчиков равно нулю (в системе нет запросов на обмен от вычислительных машин 6). При 15 поступлении первого запроса соответствующий триггер 12 узла 10 устанавливается в единичное состояние, разрешая тем самым прохождение сигналов с выхода элемента ИЛИ 9 через эле мент И 16 на инкрементный вход реверсивного счетчика 17. Содержимое этогосчетчика становится равным единице ибудет увеличиваться на единицу при поступлении каждого последующего запроса от других вычислительных машин6. Аналогичным образом формируетсясодержимое всех остальных счетчиков17, причем более раннему поступлению 3 6ной вычислительной машиной 6. С этойцелью в регистр 1 записывается соответствующая команда настройки и повыходу 32 подается разрешающий сигнална группу 22 элементов И, через которые код операции обмена с выходовгруппы 21 элементов ИЛИ записываетсяв регистр 3 управления. В дальнейшемобмен по инициативе вычислительноймашины 6 осуществляется аналогичнообмену, производимому по инициативевычислительной машины 33.При обслуживании запроса от вычислительной машины 6 коды с соответствующего реверсивного счетчика 17через группы элементов И 15, ИЛИ 21и И 22 подаются на все блоки 18 сравнения узлов 10, где сравниваютсяс содержимым собственного счетчика17 каждого узла. Если содержимоесчетчика 17 очередности поступлениязапроса от данной вычислительной машины 6 больше содержимого счетчика17 обслуживаемой вычислительноймашины 6, то соответствующий блок18 сравнения вырабатывает сигнал,который уменьшает на единицу содержимое данного реверсивного счетчика17. Таким образом, производится сжатие очереди при внеочередном обслуживании (при обслуживании запросовв порядке их поступления сжатие очереди не происходит, так как в системе нет счетчика 17 с большим значением кода, чем у счетчика 17 обслуживаемой вычислительной машины 6),По окончании обслуживания вычислительной машины 33 устанавливаются в исходное (нулевое) состояние триггер 12запроса, регистр 13 состояния и реверсивный счетчик 17 соответствующего узла 10 формирования сигналовсостояния,45 50 55 ния кода опроса и номера (приоритета) вычислительной машины 6 срегистра 11 коды операций обменас регистра 13 состояния и очередности поступления запроса со счетчика17 через группы элементов И 15 иИЛИ 21 поступают на вход 30 вычислительной машины 33. Управляющая вычислительная машина 33 анализирует всю совокупность информации: приоритетность вычислительной машины 6, очередность поступления запроса, длину очереди, После принятия решения об обслуживании запроса вычислительная машина 33 инициирует обмен с выбранФормула изобретения Устройство для сопряжения управляющей и управляемых вычислительных машин, содержащее регистр приращений, коммутатор, регистр управления, дешифратор, М блоков элементов И по три группы в каждой, элемент ИЛИ, группу элементов ИЛИ, группу элементов И, И узлов формирования сигналов состояния, каждый иэ которых состоит из регистра состояния, триггера запроса, регистра приоритета, первого блока сравнения и группыэлементов Ир причем информационный вход регистра приращений является входом настройки устройства, информационный выход регистра приращений соединен с одноименным входом коммутатора, выход которого соединен с входом "Запись-чтение" регистра управления, подключенного своим выходом к входу дешифратора, х-й выход которого, где =1 М, соединен соответственно с первыми входами элементов И трех групп хо блока, вторые входы элементов И первой и второй групп каждого из М блоков яв ляются соответственно адресными и информационными входами устройства, выходы элементов И первой и второй групп каждого из М блоков являются соответственно адресными и информа ционными выходами устройства с перного по М, вторые входы элементов И третьих групп каждого из М блоков являются с первого па М-й информационными входами устройства, 25 выходы элементов И третьих групп каждого из М блоков подключены к информационному выходу устройства, управляющий вход коммутатора является входом Строб устройства, инфарма ционньп 1 вход -го где 3.=1 М) регистра состояния узла формирования сигналов состояния является -м входом "Код операции" устройства, выход регистра состояния -га узла формирования сигналов состояния подключен к первому входу элементов И 1.-го узла формирования сигналов состояния, вторые входы которых подключены к выходу первого блока сравне ния -го узла формирования сигналов состояния, первый вход которого соединен с выходом регистра приоритета -га узла Формирования сигналов состояния, выход триггера запроса 45 д-го узла формирования сигналов состояния соединен с -м входом элемента ИЛИ, выход которого является выходом "Запрос" устройства, выходы элементов И группы -го узла формирования сиг 50 налов состояния соединены с -м входами элементов ИЛИ группы, вторые входы первых блоков сравнения всех узлов формирования сигналов состояния являются входами "Код номера управляемой вычислительной машины" устройства,выходы элементов ИЛИ группы соединеныс вторыми входами эпементов И группыи являются выходом состояния устройства, вход разрешения устройства является первым входом элементов Игруппы, выходы которых подключены кинформационным входам регистра управления, о т л и ч а ю щ е е с я тем,что, с целью расширения функциональных возможностей системы за счет исключения случаев блокировки низкоприоритетных управляемых вычислительных машин, в него введены М триггеров,арбитр, второй элемент ИЛИ, шифратор,а в каждый иэ М узлов формированиясигналов состояния - элемент И, реверсивный счетчик и второй блок сравнения, причем -й вход заграса устройства является входом установки -гатриггера, выход которого подключен к-му входу арбитра, -й выход которого соединен с 1.-м входом второго элемента ИЛИ и с входом установки триггера запроса -го узла Формированиясигналов состояния, выход второгоэлемента ИЛИ соединен с вторыми вхадами элементов И каждого из М узловформирования сигналов состояния, выход триггера запроса -га узла формирования сигналов состояния подключен к входу сброса триггера, первомувходу элемента И -га узла формирования сигналов состояния и 1.-му входушифратора, выход элемента И -гаузла формирования сигналов состояниясоединен с инкрементным входам реверсивного счетчика -га узла формирования сигнала состояния, выход которого подключен к первому входу второгоблока сравнения 1-га узла формирования сигналов состояния н к вторымвходам элементов И группы -га узлаформирования сигналов состояния, выход второго блока сравнения 1.-гоузла формирования сигналов состояниясоединен с декрементным входом реверсивного счетчика 1.-га узла формирования сигналов состояния, второй входвторого блока сравнения 1-га узлаформирования сигналов состояния соединен с вьгходам соответствующегоэлемента И группы, выход шифратораявляется выходом номера управляемойвычислительной машины устройства.

СмотретьЗаявка

4404982, 05.01.1988

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО ФИЗИКО МЕХАНИЧЕСКОГО ИНСТИТУТА ИМ. Г. В. КАРПЕНКО

БОЙЧУК БОГДАН МИХАЙЛОВИЧ, КУЖЕЛЮК ЮРИЙ АНАТОЛЬЕВИЧ, ШЕНДЕРУК СЕРГЕЙ ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 13/32, G06F 15/16

Метки: вычислительных, машин, сопряжения, управляемых, управляющей

Опубликовано: 23.10.1989

Код ссылки

<a href="https://patents.su/4-1517033-ustrojjstvo-dlya-sopryazheniya-upravlyayushhejj-i-upravlyaemykh-vychislitelnykh-mashin.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сопряжения управляющей и управляемых вычислительных машин</a>

Предыдущий патент: Устройство для управления резервированной динамической памятью

Следующий патент: Микропрограммный процессор

Случайный патент: Кольцевой счетчик