Цифровой формирователь сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1474832

Автор: Смирнов

Текст

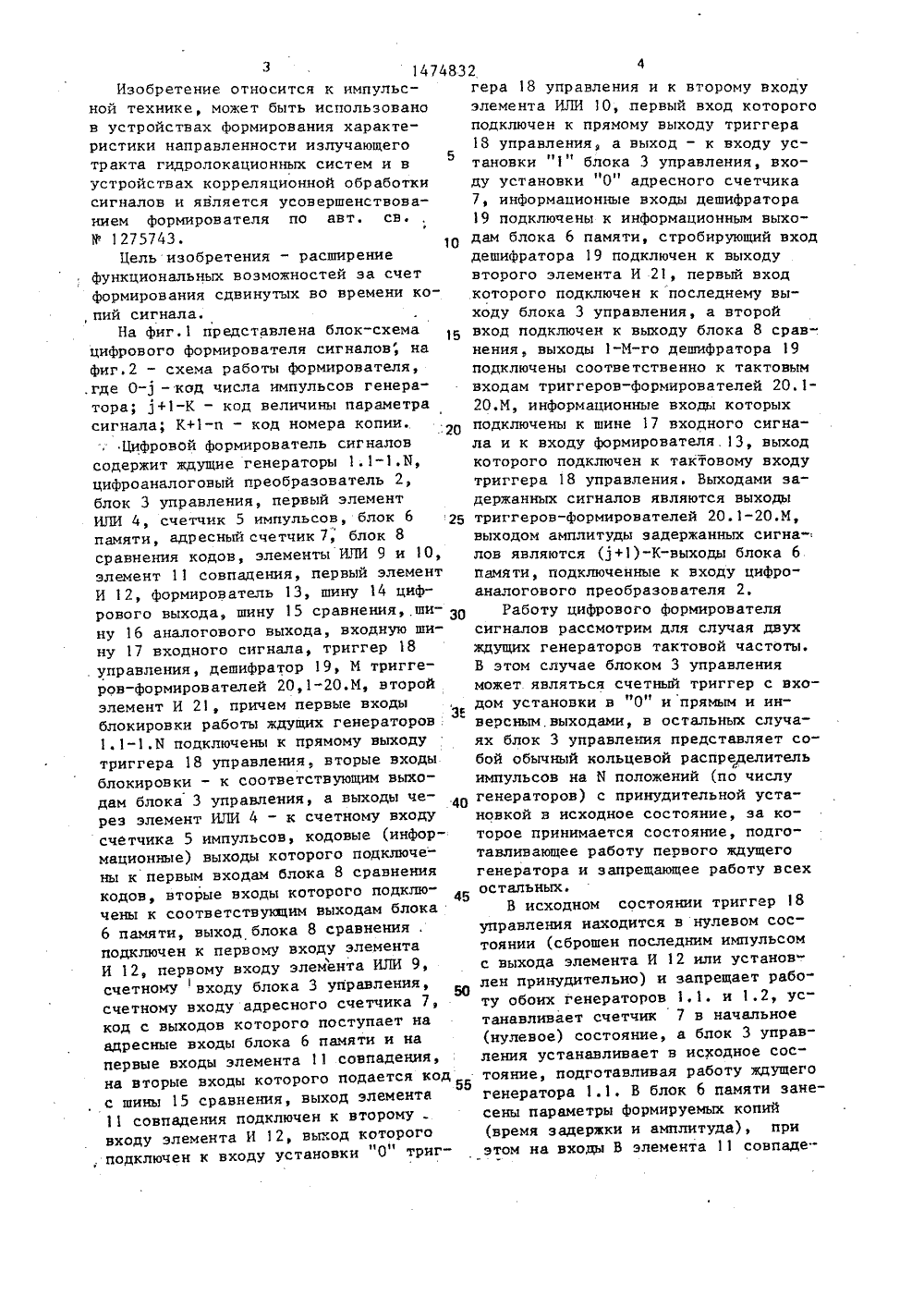

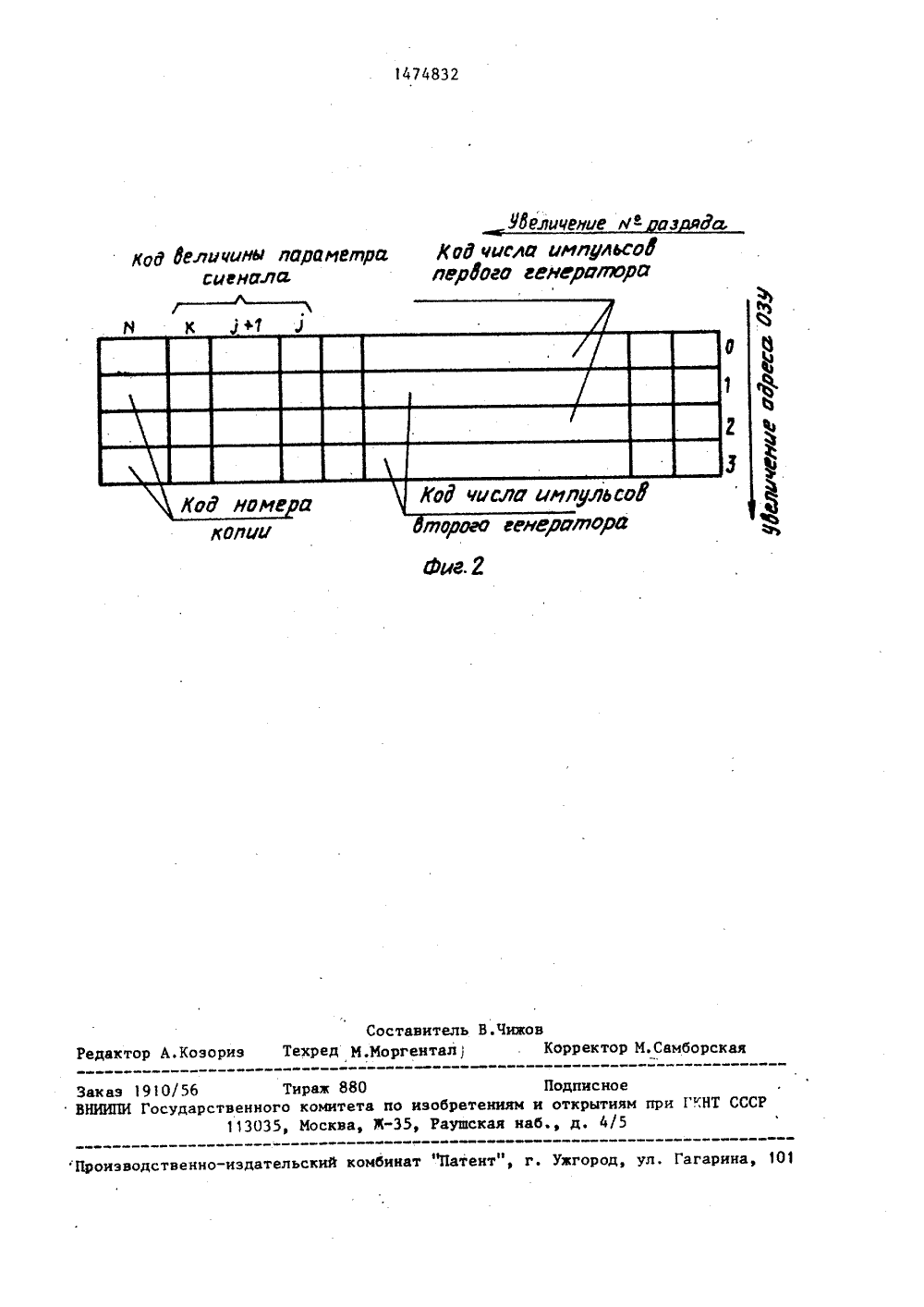

(51)4 Н 03 К 3 ПИСАНИЕ ИЗОБРЕТЕАВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И (ЛНРЫТИЯПРИ ГКНТ СССР(56) Авторское свидетельство СССРУ 1275743, кл. Н 03 К 3/84, 1985.(54) ЦИФРОВОЙ ФОРМИРОВАТЕЛЬ СИГНАЛОВ(57) Изобретение может быть исполь"зовано в устройствах формирования характеристики направленности излучающего тракта гидролокационных систем ив устройствах корреляционной обработ 2ки сигналов. Цель изобретения - повышение функциональных возможностей - достигается путем формирования сдви" нутых во времени копий сигнала. Цифровой формирователь сигналов содержит ждущие генераторы 1, цифроаналоговый преобразователь 2, блок 3 управления, элементы ИЛИ 4, 9 и 10, счетчик 5 импульсов, элемент 11 совпадения, адресный счетчик 7, блок 8 сравнения кодов, элементы И 12 и 21, формирователь 13, триггер 18 управления, дешифратор 19 и триггеры-формирователи 20, 2 ил.генератора и запрещающее работу всех остальных.В исходном состоянии триггер 18 управления находится в нулевом состоянии (сброшен последним импульсом с выхода элемента И 12 или установлен принудительно) и запрещает работу обоих генераторов 1.1. и 1.2, ус" танавливает счетчик7 в начальное (нулевое) состояние, а блок 3 управления устанавливает в исходное состояние, подготавливая работу ждущегогенератора 1.1, В блок 6 памяти зане 3147483Изобретение относится к импульсной технике, может быть использованов устройствах формирования характеристики направленности излучающеготракта гидролокационных систем и в5устройствах корреляционной обработкисигналов и является усовершенствованием формирователя по авт. св,У 1275743.10Цель изобретения - расширениефункциональных возможностей за счетформирования сдвинутых во времени ко".где 0-1 - код числа импульсов генератора;+1-К - код величины параметрасигнала; К+1-и - код номера копии.Цифровой формирователь сигналовсодержит ждущие генераторы 1.1-1.И,цифроаналоговый преобразователь 2,блок 3 управления, первый элементИЛИ 4, счетчик 5 импульсов, блок 6памяти, адресный счетчик Т, блок 8сравнения кодов, элементы ИЛИ 9 и 10,элемент 11 совпадения, первый элементИ 12, формирователь 13, шину 14 цифрового выхода, шину 15 сравнения, ши- З 0ну 16 аналогового выхода, входную шину 17 входного сигнала, триггер 18 . управления, дешифратор 19, М триггеров-формирователей 20,1-20.М, второйэлемент И 21, причем первые входыблокировки работы ждущих генераторов .1.1-1.Н подключены к прямому выходутриггера 18 управления, вторые входыблокировки - к соответствующим выходам блока 3 управления, а выходы через элемент ИЛИ 4 - к счетному входусчетчика 5 импульсов, кодовые (информационные) выходы которого подключены к первым входам блока 8 сравнениякодов, вторые входы которого подключены к соответствукцим выходам блока6 памяти, выход блока 8 сравнения .подключен к первому входу элементаИ 12, первому входу элемента ИЛИ 9,счетному входу блока 3 управления,счетному входу адресного счетчика 7, код с выходов которого поступает наадресные входы блока 6 памяти и на первые входы элемента 11 совпадения, на вторые входы которого подается код с шины 15 сравнения, выход элемента11 совпадения подключен к второму входу элемента И 12, выход которого11 11 ,. подключен к входу установки 0 триг 24гера 18 управления и к второму входуэлемента ИЛИ 10, первый вход которого подключен к прямому выходу триггера18 управления, а выход - к входу установки "1" блока 3 управления, входу установки "0" адресного счетчика7, информационные входы дешифратора19 подключены к информационным выходам блока 6 памяти, стробирующий вход дешифратора 19 подключен к выходувторого элемента И 21, первый входкоторого подключен к последнему выходу блока 3 управления, а второй вход подключен к выходу блока 8 сравнения, выходы 1-М-го дешифратора 19 подключены соответственно к тактовым входам триггеров-формирователей 20.1- 20.М, информационные входы которых подключены к шине 17 входного сигнала и к входу формирователя.13, выход которого подключен к тактовому входу триггера 18 управления, Выходами задержанных сигналов являются выходы триггеров-формирователей 20.1-20.М, выходом амплитуды задержанных сигна". лов являются Я+1)-К-выходы блока 6 памяти, подключенные к входу цифроаналогового преобразователя 2.Работу цифрового формирователя сигналов рассмотрим для случая двух ждущих генераторов тактовой частоты. В этом случае блоком 3 управления может являться счетный триггер с входом установки в "0" и прямым и инверсным выходами, в остальньпс случаях блок 3 управления представляет собой обычный кольцевой распределительимпульсов на Ы положений (по числугенераторов) с принудительной установкой в исходное состояние, за которое принимается состояние, подготавливающее работу первого ждущего сены параметры формируемых копий(время задержки и амплитуда), приэтом на входы В элемента 11 совпадеб 147483ния подается код произведения количества генЕраторов на количество формируемых задержанных копий исходногосигнала, на входы А блока 8 сравнения поступает код "0" с выхода счетчика 5 на входы В - код первого подынтервала задержки первой копии.При изменении параметров сигнала(переход логического "О" в логическую "1" или наоборот) на входе формирователя 13 дифференцирующая цепь,формирующая короткие положительныеимпульсы при переходе логическогоуровня входного сигнала из "О" в "1"(и наоборот), на его выходе формируется короткий (меньше длительностивходного импульса) положительный импульс, устанавливающий триггер 18 вединичное состояние, разрешая работу 2 Ождущих генераторов 1.1 и 1. 2, но работать начинает только генератор 1.1,так как генератор 1.2 заблокировансигналом с выхода блока 3 управления,импульсы генератора 1.1 через элемент 25ИЛИ 4 поступают на вход счетчика 5импульсов, код с выходов счетчика 5импульсов поступает на входы А блока8 сравнения кодов, на вход В которогопоступает код первого подынтервала З 0задержки первой копии. При равенствекодов блок 8 сравнения вырабатываетимпульс, изменяющий состояние блока3 управления, обнуляющий счетчик 5импульсов и увеличивающий код счетчика 7 адресного на единицу, выбираяиз блока 6 памяти содержимое следующей ячейки. На входы В блока 8 сравнения кодов поступает код второгоподынтервала задержки первой копии.Блок 3 управления блокирует работу генератора 1,1 и разрешает работугенератора 1.2, импульсы которого через элемент ИЛИ 4 также поступает навход счетчика 5 импульсов. При равенстве кодов блок 8 сравнения вновь вырабатывает импульс, обнуляющий счетчик 5 импульсов, возвращающий блок 3управления в исходное положение,- вновь увеличивая код адресного счетчика 7 на единицу и подавая на входы В блока 8 сравнения код первогоподынтервала задержки второй копии(по отношению к первой). Сигнал свыхода блока 8 сравнения при формировании последнего подынтервала первой,копии через элемент И 21 поступает настробирующий вход дешифратора 19,,сигнал с первого выхода которого ус-; 2 бтанавливает триггер-формирователь 20,1 в состояние, соответствующее входному сигналу, формируя передний фронт первого задержанного импульса. Этот процесс продолжается до тех пор, пока код на выходе адресного счетчика 7 не совпадает с кодом на входах В элемента 11 совпадения. При совпадении кодов в момент формирования фронта последнего задержанного сигнала импульс с выхода первого элемента И 12 устанавливает триггер 18 управления, счетчик 5 импульсов, адресньй счетчик 7, блок 3 управления и ждущие генераторы 1.1-1.Б в исходное состояние, При поступлении следующего перепада напряжения на вход формирователя 13 процесс формирования задержанных сигналов протекает аналогично.Предлагаемый формирователь позволяет формировать любое количество копий сигнала при условии, что максимальная задержка копии не превышает минимума длительностей импульса и паузы входного сигнала. Формула изобретенияЦифровой формирователь сигналов по авт.св. 9 1275743, о т л и ч а - ю щ и й с я тем, что, с целью расширения функциональных возможностей за счет формирования задержанных копий сигнала, в него введены формирователь, триггер управления, дешифратор, второй элемент И и М триггеров- формирователей, причем вход формирователя подключен к информационным входам М триггеров-формирователей и к входной шине, выход формирователя подключен к входу синхронизации триггера управления, выход которого подключен к первому входу третьего элемента ИЛИ, а вход установки нуля подключен к выходу первого элемента И, информационные входы дешифратора подключены кинформационным выходам блока памяти, стробирующий вход дешифратора подключен к выходу второго элемента И, первый вход которого подключен к последнему выходу блока управления, а второй вход подключен к выходу блока сравнения кодов, М информационных выходов дешифратора подключены соответственно к информационным входам М триггеров-формирователей.1474832 Составитель Техред М,Моргентал, ижов Корректор М.Самборска Коэо ак аэ 1910/56 Тираж 880 ПодписноеНИИПИ Государственного комитета по иэобретениям и открытиям при ГКНТ 113035, Москва, Ж, Раушская наб., д. 4/5 енно-издательский комбинат "Патент", г. Ужгород, ул. Гагар оиэво Код Зеличины ларамеара сие налаЛеличеиие м- аз оЪ Код чигла импульсоР оер 3 оеа генерапюро

СмотретьЗаявка

4278607, 06.07.1987

ПРЕДПРИЯТИЕ ПЯ В-2445

СМИРНОВ АНАТОЛИЙ ПЕТРОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: сигналов, формирователь, цифровой

Опубликовано: 23.04.1989

Код ссылки

<a href="https://patents.su/4-1474832-cifrovojj-formirovatel-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой формирователь сигналов</a>

Предыдущий патент: Г-триггер

Следующий патент: Устройство для задержки информации с контролем

Случайный патент: Устройство для преобразования переменного напряжения в постоянное