Адаптивная система интегрирования дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

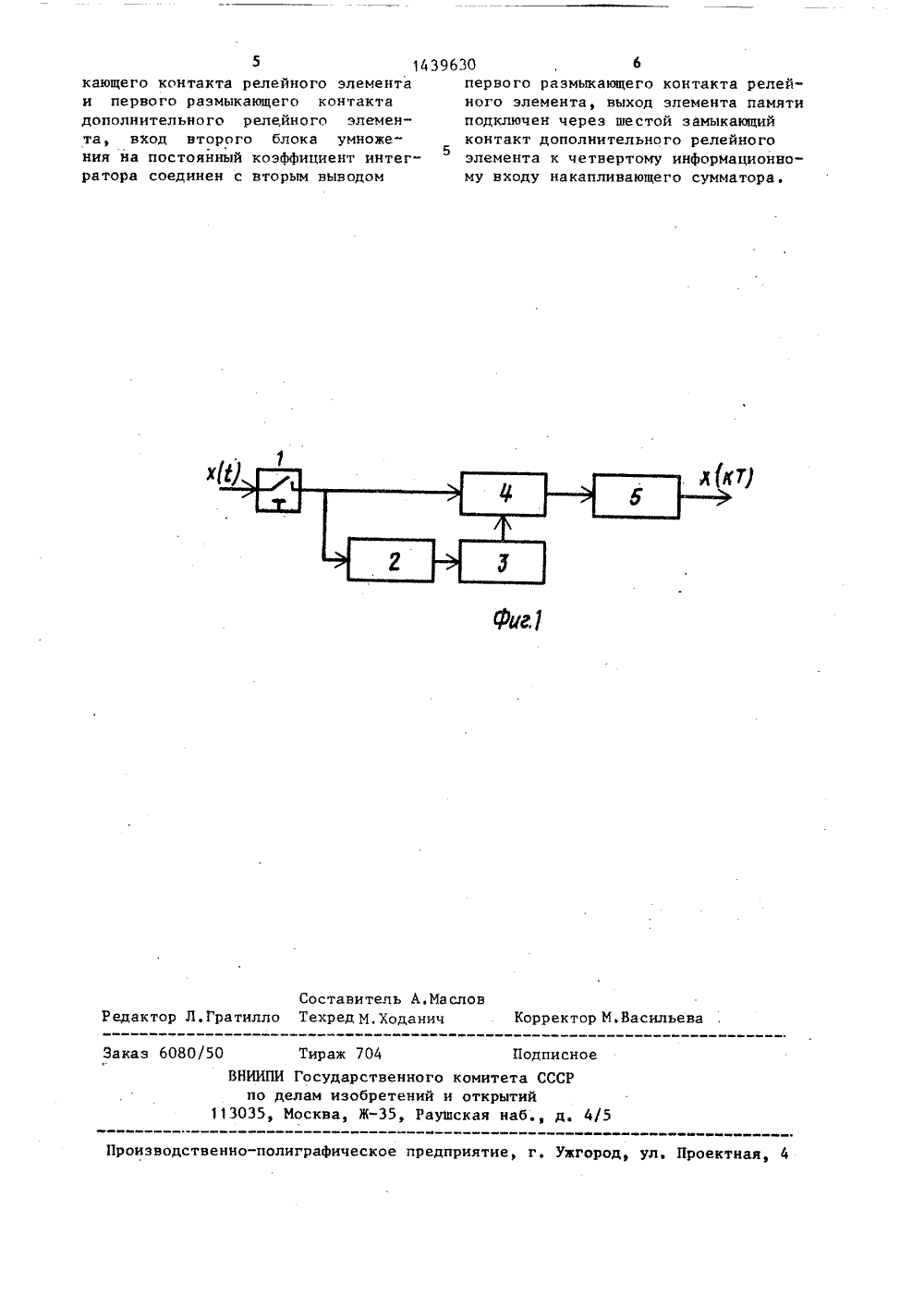

(19 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ ИСАНИЕ ИЗОБРЕТ 20814/2(57) АПТИВНАЯ СИСТЕМА ИНТЕГРИРОВАКРЕТНЫХ СИГНАЛОВ ится к систеобретение отно авления и изме ельнои техним интегрированияможет быть ис"в системах наетательными едназначено для тных сигналов и вано, например, и и управления л тами. Целью изоб ке, п дискр польз и вх вигаци аппара ретения являет(21) 41 (22) 12 (46) 23 (72) Н, и В.А,Н (53) 68 (56) Ку ние дис М.: МашАвто В 11793 РСКОМУ СВИДЕТЕЛЬСТВ ся повышение точности интегрирования без уменьшения периода дискретности. Система содержит квантователь 1 входного сигнала по времени, анализатор 2 характера изменения входного сигнала с блском вычисления первой и второй разности, блок коммутации 3,блок интегрирования 4 и накапливающий сумматор 5. Анализатор 2 характера изменения входного сигнала содержит два последовательно соединенных элемента памяти на Т , блоки вычисленияс фпервой и второй разностей и пороговые элементы с зоной нечувствительности- А. Блок интегрирования 4 построен на элементах памяти, блоках умножения с коэффициентами, соответ- фТ Тственно равными 4, Т, в , в , двух блоах суммирования на два39630 2Т, Т(2, Т/3. Связи в интеграторе формируются замыкающими и размыкающимиоконтактами репейных элементов 12и 13, реализующих интеграторы по правилам прямоугольника, трапеции и1/3 Симпсона, разностные уравнениякоторых имеют видх (КТ) =хК) Т+Т х (КТ); (3) Изобретение относится к областисистем управления и измерительнойтехники и предназначено для интегрирования дискретных сигналов,Целью изобретения является повышение точности интегрирования сигналов без уменьшения периода дискретно сти.На фиг.1 представлена блочная схема системы; на фиг.2 - структурнаясхема системы.Система (фиг.1) содержит квантователь 1 входного сигнала по времени,анализатор 2 характера изменениявходного сигнала, блок 3 коммутации,интегратор 4, накапливающий сумматор 5. Анализатор 2 (фиг.2) содержитосновной элемент 6 памяти и дополнительный элемент 7 памяти на Ткаждый, блок 8 вычисления первой иблок 9 вычисления второй разностей,первый пороговый элемент 10 и дополнительный пороговый элемент 11. Навыходе блоков вычисления разностейпоследовательно формируются разности2)х(КТ) =х(КТ) - х(К-) Т 1;дх(КТ) =д х(КТ) -Ьх (К) Т, (1)а пороговые элементы 10 и 11 реализуют условиядх(КТ)Я,; дх(КТ Е 1(д 2 х(КТ)( Е 2;д 2 х(КТ) е, (2)где Ос тЕ,м,); 3.=1,2,и выдают сигналы на блок 3 коммутации,Блок 3 коммутации содержит первый12 и дополнительный 13 релейные элементы с замыкающими и размыкающимиконтактами, структурно расположенными в интеграторе 4,Первый релейный элемент 12 имееттри контакта, из которых первый 14размыкающий, второй 15 и третий 16замыкающие.Второй дополнительный релейныйэлемент имеет шесть контактов, изкоторых первый 17 и второй 18 размыкаюшие, а третий 19, четвертый 20,пятый 21, шестой 22 контакты замыка"ющие.Интегратор 4 содержит элемент 23памяти на Тр, входом подключенныйк выходу первого элемента памяти анализатора характера изменения входногсигнала, первый 24 и второй 25 блокисуммирования соответственно на дваи три входа, четыре блока умножения,первый 26, второй 27, третий 28 ичетвертый 29 с постоянными коэффициентами, соответственно равными 4,х (КТ)=хК) Т 1 - х(КТ)+2+хК) Я, (К)где Т - период дискретности, К=О, 12,Накапливающий сумматор 30 хранит20 предыдущее значение интеграла, а через элемент 31 памяти и замыкающийконтакт 22 формируется значениях(К)Т для реализации соотношения (5).25 Адаптивная система интегрирования работает следующим образом.Дискретный сигнал х (КТ) с квантователя 1 подается на вход анализатора 2 и интегратор 4,30 Вначале срабатывает анализатор 2,а затем работает интегратор 4. В ана"лизаторе 2 последовательно вычисляются первая дх (КТ) и вторая д х (КТ)разности, которые поступают соответственно на пороговые элементы 10и 11, и проверяются условия (2), взависимости от которых работают релейные элементы 12 и 13, контакты ко-.торых производят коммутацию связей4 О в интеграторе 4, Например, если сигнал х (С) постоянный, то первая раз-.ность дх(КТ) и вторая разностьдх (КТ) равны нулю, релейные элемен-ты 12 и 13 не срабатывают, входнойсигнал х (КТ) через размыкающий контакт 14 и второй блок 27 умноженияна коэффициент Т поступает на первыйвход накапливающего сумматора 5 иреализуется состояние (3).1Если х(с) изменяется по линейномузакону, то срабатывает только первыйрелейный элемент 12 и через его коно такты 15 и 16, 17 и 18 сигналы сквантователя в виде х (КТ) и с элемента 6 памяти анализатора в видех (К) Т 1 поступают на входы первогоблока 24 суммирования, а с него - навторой вход накапливающего сумматора30 через третий блок 28 умножения с1 О 15 20 25 3 143 коэффициентом Т/2. В сумматоре 30 формируется значение х (КТ) по правилу трапеции С 4) .Если х параболический, то срабатывают релейные элементы 12 и 13, так как А х (КТ), 1 Р х(КТ) Ег, и через их замкнутые контакты 15, 16, 19, 20, 21 и 22 сигналы с квантователя 1, выходов элементов 6 и 23 памяти поступают на три входа второго блока 25 суммирования, а с него через четвертый блок 29 умножения с коэффициентом Т/3 - на третий вход накапливающего сумматора 5, где суммируется с сигналом х(К) ТД, поступившим с выхода элемента 31 памяти и замыкающим контакт 22 релейного элемента 13. В результате реализуется интегрирование по правилу 1/3 Симпсона (5). При включении обратной связи через элемент 31 памяти и контакт 22 необходимо обнулить сумматор 30, так как в нем хранится значение х (К) Т, которое не используется в формуле (5) . 9630 4 второго, третьего и четвертого блоковумножения на постоянные коэффициентыи первого и второго блоков суммирова"ния, подключенных выходами к входамсоответственно третьего и четвертогоблоков умножения на постоянные коэффициенты, выход первого блока умножения на постоянный коэффициент соединен в интеграторе с первым входом его второго блока суммирования, а вы-ходы второго, третьего и четвертогоблоков умножения на постоянные коэффициенты интегратора подключены соответственно к первому, второму и,третьему информационным входам накапливающего сумматора, анализатор ха"рактера изменения входного сигналадополнительно содержит последовательно соединенные дополнительный элементпамяти, блок вычисления второй раз-."ности и дополнительный пороговый элемент, выход которого подключен к управляющему входу дополнительного релейного элементы системы, вход допол Формула изобретения Адаптивная система интегрирования дискретных сигналов, содержащая квантователь входного сигнала по времени, вход которого является входом системь 1, интегратор, первый релейный элемент и анализатор характера изменения входного сигнала, выполненный на последовательно соединенных элементе памяти, блоке вычисления первой разности и пороговом элементе, выход которого подключен к управляющему входу первого релейного элемента системы, выход квантователя входного сигнала по времени подключен к первым выводам первого размыкающего и второго замыкающего контактов первого релейного элемента, к входу элемента памяти анализатора характера изменения входного сигнала и к другому входу блока вычисления первой разности анализатора характера изменения входного сигнала, о т л и ч а ю щ ая с я тем, что, с целью повышения точности интегрирования сигналов без уменьшения периода дискретности, она содержит дополнительный релейный элемент, накапливающий сумматор и . элемент памяти, подключенный входом к выходу накапливающего сумматора, который является выходом системы, интегратор выполнен в виде первого, 30 35404550 55 ножения на постоянный коэффициентподключен через пятый замыкающий кон такт дополнительного релейного элемента к общему выводу третьего замынительного элемента памяти и другой вход блока вычисления второй разности анализатора характера изменения входного сигнала подключены к выходу блока вычисления первой разности, выход первого элемента памяти анализатора характера изменения входного сигнала подключен через последовательно соединенные третий замыкают щий контакт релейного элемента и пер. вый размыкающий контакт дополнительного релейного элемента к первомувходу первого блока суммированияинтегратора, второй вход первого бло.ка суммирования которого подключенчерез второй размыкающий контакт дополнительного релейного элемента к второму выводу второго замыкающего контакта релейного элемента, а их общий вывод подключен через третий замыкающий контакт дополнительногорелейного элемента к второму входу второго блока суммирования интегратора, третий вход второго блока суммирования интегратора подключен через четвертый замыкающий контакт дополнительного релейного элемента к выходу дополнительного элемента памяти анализатора характера изменения входного сигнала, вход первого блока ум"Т) оставитель А,М ехред М. Ходани Корректор М. Васильева Редактор Л.Грати Под Заказ 6080/50 Тираж 704 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, Раушсн омитета ССС открытийкая наб., д 4 оизводственно-полиграфическое предприятие, г. Ужгород, ул. Проек 4 5 1439630 6кающего контакта релейного элемента первого размыкающего контакта релейи первого размыкающего контакта ного элемента, выход элемента памяти дополнительного релейного элемен- подключен через шестой замыкающий та, вход второго блока умноже" контакт дополнительного релейного ния на постояйный коэффициент интег- элемента к четвертому информационно 5ратора соединен с вторым выводом му входу накапливающего сумматора.

СмотретьЗаявка

4120814, 12.06.1986

СЕРПУХОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. ЛЕНИНСКОГО КОМСОМОЛА

ХАРИН НИКОЛАЙ ТИМОФЕЕВИЧ, БОБЫРЕВ ВЛАДИМИР БОРИСОВИЧ, НИКИФОРОВ ВИКТОР АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06G 7/18

Метки: адаптивная, дискретных, интегрирования, сигналов

Опубликовано: 23.11.1988

Код ссылки

<a href="https://patents.su/4-1439630-adaptivnaya-sistema-integrirovaniya-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Адаптивная система интегрирования дискретных сигналов</a>

Предыдущий патент: Фазовое делительное устройство

Следующий патент: Устройство для моделирования нейрона

Случайный патент: Насос а. к. худолеева