Аналоговый интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1425724

Автор: Архипов

Текст

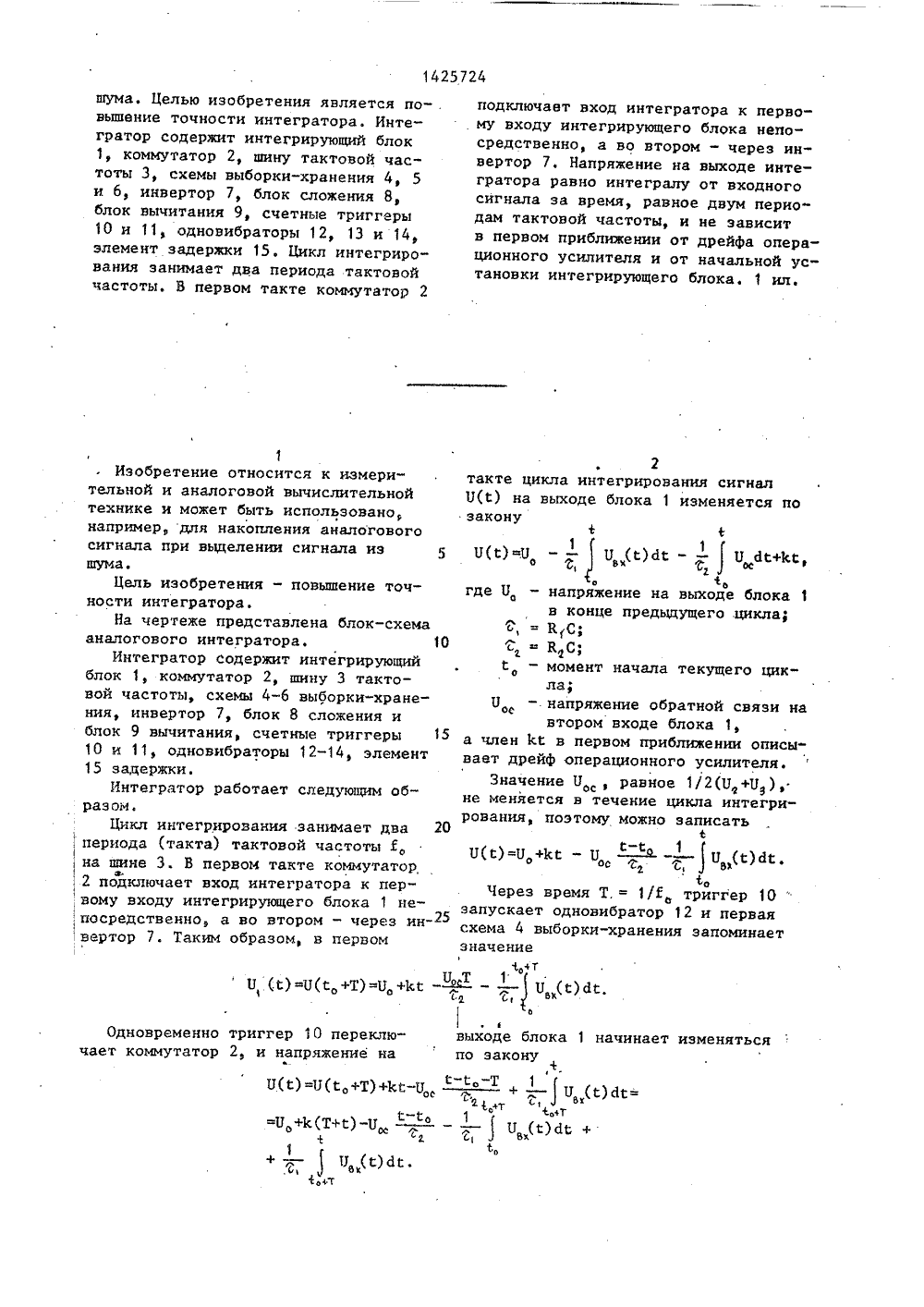

(51 ПИСАНИЕ ИЗОБРЕТЕНИЯ ТЕЛЬСТВ АВТОРСКОМУ СГОСУДАРСТВЕННЫЙ КОМИТЕТ СС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНР 4197382/24-2423.02.8723.09.88. БюлС.В. Архипов681335(088.8Патент США06 С 7/18,ултон. Точньвным сброУ 18, с(57) Изобретение относится к измериф тельной и аналоговой вычислительной технике, предназначено для получения периодической последовательности значений интеграла аналогового сигнала на заданном интервале интегрирования и может быть использовано, например, для накопления аналогового сигнала при вьщелении сигнала из1425724 подключает вход интегратора к перво, му входу интегрирующего блока непосредственно, а во втором - через инвертор 7. Напряжение на выходе интегратора равно интегралу от входного сигнала за время, равное двум перно" дам тактовой частоты, и не зависит в первом приближении от дрейфа операционного усилителя и от начальной установки интегрирующего блока. 1 ил. шума. Целью изобретения является повьппение точности интегратора. Интегратор содержит интегрирующий блок1, коммутатор 2, шину тактовой частоты 3, схемы выборки-хранения 4, 5и 6, инвертор 7, блок сложения 8,блок вычитания 9, счетные триггеры10 и 11, одновибраторы 12, 13 и 14,элемент задержки 15. Цикл интегрирования занимает два периода тактовойчастоты, В первом такте коммутатор 2 1 гИзобретение относится к измери- такте цикла интегрирования сигналтельной и аналоговой вычислительной 0(С) на выходе блока 1 изменяется потехнике и может быть использовано, законунапример, для накопления аналоговогосигнала при выделении сигнала иэ 5 ц(е) ц -- ц (е)йе -- Ц йС+Ыс,1 1шума.о , вх фг6соЦель изобретения - повышение точ- где Ц - напряжение на выходе блока 1аности интегратора. в конце предыдущего цикла;На чертеже представлена блок-схема = К Сэаналогового интегратора. 10К СфИнтегратор содержит интегрирующий е - момент начала текущего цикоблок 1, коммутатор 2, шину 3 такто- ла;вой частоты, схемы 4-б выборки-хране в . напряжение обратной связи наоения, инвертор 7, блок 8 сложения и втором входе блока 1,блок 9 вычитания, счетные триггеры 15 а член И в первом приближении описы"10 и 11, одновибраторы 12-14, элемент вает дрейф операционного усилителя.Значение У, равное 1/2(У +У ),Интегратор работает следующим обрования, поэтому можно записатьразом.Цикл интегрирования занимает два 20пеуиода (такта) тактовой частоты Хо Ц(С)=У +1 С - У в -Я- - 11 ДЕона шине 3. В первом такте коммутаторхСо; 2 подключает вход интегратора к пер- . Через время Т. = 1/Е триггер 1 О "овому входу интегрирующего блока 1) не запускает одновибратор 12 и перваяпосредственно, а во втором - чер и" схема 4 выборки-хранения запоминает25вертор 7. Таким образом, в первомс,т11 (со Т) 1 о1.) Т 1Одновременно триггер 10 переклю- выходе блока 1 начинает изменятьсячает коммутатор 2, и напряжение на по законуФ331425724 4.В конце второго такта триггер 11 минает напряжение цв, которое до этои с некоторой задержкой триггер 10го хранилось во нторой схеме 5 выбор- переходят в исходное состояние, за- ки-хранения, а эта последняя схема пУская одновибраторы 13 и 14. При этом запоминает сигнал конца текущего цик 5третья схема 6 выборки-хранения запо- ла, равный1,+тЦ(с,+2 Т) 1 Л,+2 КТц, ---и (с)ас +ТТаким образом, на выходе блока 8 сложения, реализующего функцию Ц 1/2(Ц + Цз), по окончании цикла 15 интегрирования получают напряжение обратной связи для следующего цикла интегрирования равноетТ 1 ц.+1 Т - ц - , --ц И)1 - гО о ос) вл 6 ф 2 т - и (с)ас,,т а на выходе блока 9 вычитания - напряжение 252 т ц - -- ц (е)йе.1 вью вк10Отсюда видно, что напряжение на выходе интегратора равно интегралу от входного сигнала за время, равное двум периодам тактовой частоты, и не зависит в первом приближении от дрейфа операционного усилителя и от начальной установки интегрирующего блока.Обратная связь с выхода блока 8 сложения на второй вход интегрирующего блока 1 обеспечивает работу интегрирующего блока н оптимальном 40 диапазоне выходных напряжений. Критерием оптимальности здесь служит условие близости к нулю одйой из границ диапазона. Эта граница определяется значением напряжения ц в -м цикле 453-1 интегрирования. учитывая, что ц ц а ц, =, 1/2(ц + ц), можна записать для цот оф 2 Т -ц,(с)й -и (с)асф.о 1,тВ стационаРном Режиме пРи Цв(С) = сопзС интегралы в квадра 7 ных скоб 55ках равны между собой, а Ц 2 = цпоэтому имеют ц = 1 ссОтсюда видно, что в отсутствие дрейфа (Ь " 0) граница диапазона сигнала на выходе интегрирующего блока 1 равна нулю, а при разорванной обратной связи (2оо ) дрейф делает невозможной работу схемы. Снизу значениеограничено погрешностью интегрирования, которую вносит уменьшение этой .величины вследствие конечности коэффициента усиления операционного усилителя. Формула изобретенияАналоговый интегратор, содержащий двухвходовой интегрирующий блок, две схемы выборки-хранения, о т л и ч а ющ и й с я тем, что, с целью повышения точности интегратора, в него введены третья схема выборки-хранения, два счетных триггера, три одновибратора, блоки сложения и вычитания, элемент задержки, инвертор .и коммутатор, первый информационный вход которого непосредстненно, а второй через инвертор соединены с входом интегратора, выход коммутатора подключен к первому входу двухвходового интегрирующего блока, второй вход которого соединен с выходом блока сложения, а выход подключен к информационным входам первой и второй схем выборки-хранения, вход первого счетного триггера через элемент задержки соединен с шиной тактовой частоты, прямой ныход подключен к управляющему входу коммутатора и через первый одновибратор - к управляющему входу первой схемы выборки-хранения, выход которой соединен с первым входом блока вычитания, выход которого является выходом интегратора, а второй вход подключен к выходу блока сложения, инверсный выход первого счетного триггера через второй одновибратор подключен к управляю. щему входу второй схемы выборки-хранения, выход которой соединен с первым входом блока сложения и информационным входом третьей схемы выборки-хранения, выход которой подключен к нто/ Заказ 4773/49 Тираж 704 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раушская наб., д, 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 рому входу блока сложения, а управляющий вход через третий одновибраторсоединен с инверснья выходом второго счетного триггера, вход которого под,ключен к шине тактовой частоты инте

СмотретьЗаявка

4197382, 23.02.1987

ПРЕДПРИЯТИЕ ПЯ Ю-9270

АРХИПОВ СЕРГЕЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06G 7/186

Метки: аналоговый, интегратор

Опубликовано: 23.09.1988

Код ссылки

<a href="https://patents.su/4-1425724-analogovyjj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый интегратор</a>

Предыдущий патент: Делитель напряжения

Следующий патент: Аналого-цифровое вычислительное устройство

Случайный патент: Рабочий орган кратцер-крана