Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

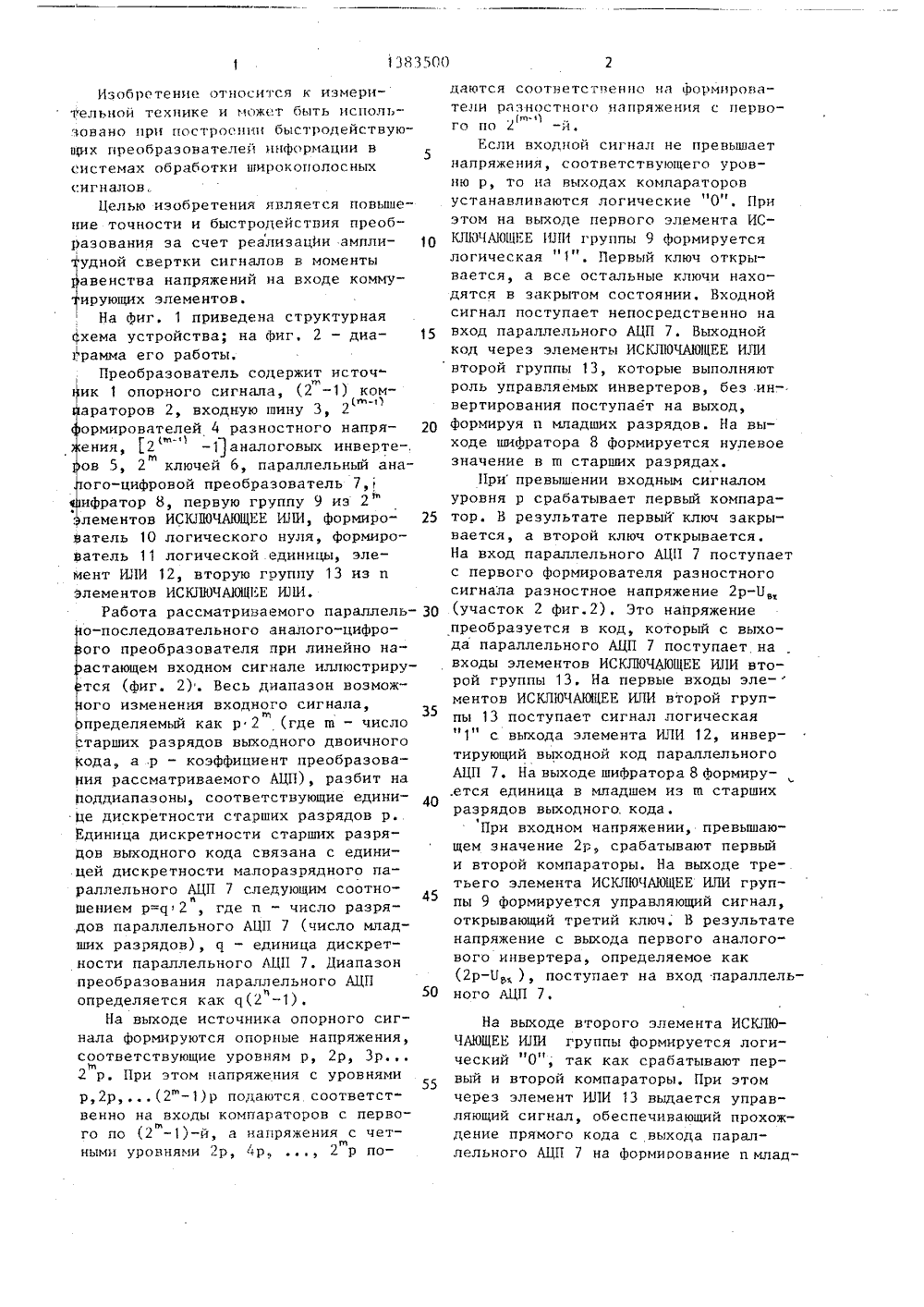

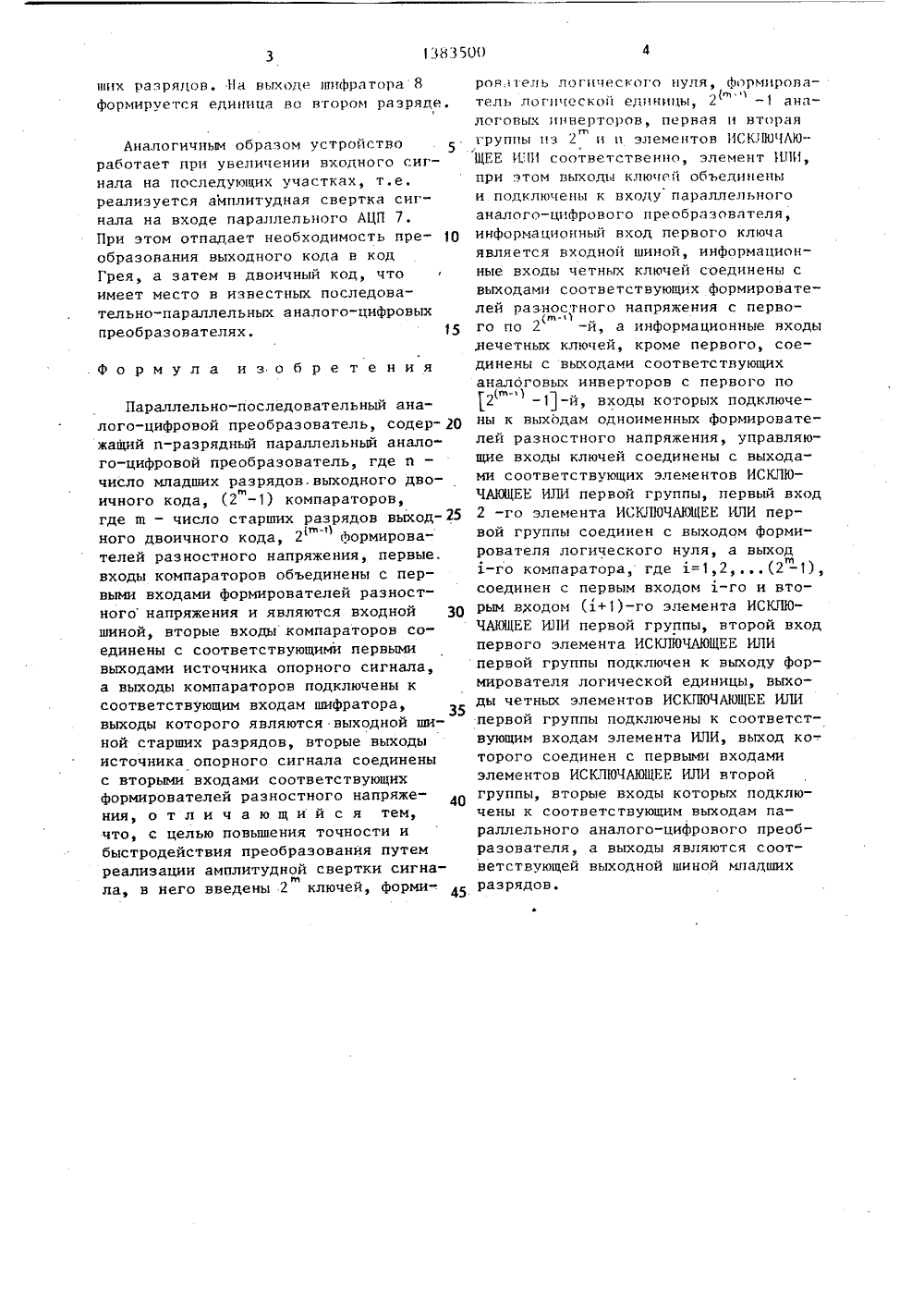

)д, 1 И ЕТЕЛЬСТ ВТОРС ладко 7 981.СР 19 ТЕЛЬНЫИВАТЕЛЬ(57) Изобретенизмерительной тиспользовано пдействующих пр е относитехники ии построеобразоват я к областиожет быть и быс елеи ин о ГОСУДАРСТВЕННЫЙ НОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫ ОПИСАНИЕ ИЗОБР(56) Заявка ЕПВ (ЕР) У 0кл. Н ОЗ К 13/175, опублиАвторское свидетельствВ 1069156, кл. Н 03 М 1/ 54) ПАРАЛЛЕЛЬНО-ПОС 11 ЕДО НАЛОГО-ЦИФРОВОЙ ПРЕОБРА ции в системах обработки широкополосных сигналов. В устройство, содержащее и-разрядный параллельный аналогоцифровой преобразователь 7, компаратры 2, формирователи 4 разностногонапряжения, источник 1 ойорного сигнла и шифратор 8, с целью повышенияточности и быстродействия преобразования за счет реализации и амплитудной свертки сигнала и коммутации сигналов в моменты равенства напряжений на входе и выходе коммутирующихэлементов, введены аналоговые инверторы 5, ключи 6, первая и втораягруппы 9 и 13 элементов ИСКЛЮЧАЮЩЕЕИЛИ, формирователи 1 О и 11 логических единицы и нуля соответственнои элемент ИЛИ 12, 2 ил.10 15 20 25 30 35 40 45 50 55 Изобретение относится к измери- "елькой технике и может быть использовано при построении быстродействук- щих преобразователей информации в системах обработки широкополосных сигналов,Целью изобретения является повышение точности и быстродействия преобразования за счет реализации амплиудной свертки сигналов в моментыавенства напряжений на входе коммуирующих элементов.На фиг. 1 приведена структурнаяСхема устройства; на фиг. 2 - диа,рамма его работы.Преобразователь содержит источник 1 опорного сигнала, (2 -1) комв-араторов 2, входную шину 3, 2ормирователей 4 разностного напряв- )ения, 2 -1 аналоговых инверте-,ов 5, 2 ключей 6, параллельный аналого-цифровой преобразователь 7,шифратор 8, первую группу 9 из 2элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь 10 логического нуля, формирователь 11 логической единицы, элемент ИЛИ 12, вторую группу 13 из иЭлементов ИСКЛЮЧАЮЩЕЕ ИЛИ,Работа рассматриваемого параллельо-последовательного аналого-цифроого преобразователя при линейно наастающем входном сигнале иллюстрирутся (фиг. 2). Весь диапазон возможного изменения входного сигнала,рпределяемый как р 2 (где щ - числостарших разрядов выходного двоичногоКода, а р - коэффициент преобразоваНия рассматриваемого АЦП), разбит нацоддиапазоны, соответствующие единице дискретности старших разрядов р.Единица дискретности старших разрядов выходного кода связана с единицей дискретности малоразрядного параллельного АЦП 7 следующим соотноншением р=о 2, где и - число разрядов параллельного АЦ 11 7 (число младших разрядов), Ч - единица дискретности параллельного АЦ 11 7. Диапазонпреобразования параллельного АЦПопределяется как Ч(2 -1)На выходе источника опорного сигнала формируются опорные напряжения,соответствующие уровням р, 2 р, Зр2 р, 11 ри этом напряжения с уровнямир,2 р,(2"-1)р подактся соответст"венно на входы компараторов с первого по (2 - 1)-й, а напряжения с четными уровнями 2 р, 4 р , 2 р подаются соответственно на фГ)рмнрова -тели разностного напряжения с первою го по 2 -й.Если входной сигнал не превышает напряжения, соответствующего уровню р, то на выходах компараторов устанавливаются логические "0", При этом на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 9 формируется логическая "1". Первый ключ открывается, а все остальные ключи находятся в закрытом состоянии, Входной сигнал поступает непосредственно навход параллельного АЦП 7. Выходнойкод через элементы ИСКЛЮЧАЮЩЕЕ ИЛИвторой группы 13, которые выполняютроль управляемых инвертеров, без инвертирования поступает на выход,формируя и младших разрядов. На выходе шифратора 8 формируется нулевоезначение в щ старших разрядах.При превышении входным сигналомуровня р срабатывает первый компаратор. В результате первый ключ закры"вается, а второй ключ открывается.На вход параллельного АЦ 11 7 поступаетс первого формирователя разностногосигнала разностное напряжение 2 р-Б,(участок 2 фиг.2). Это напряжениепреобразуется в код, который с выхода параллельного АЦП 7 поступает, навходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 13. На первые входы эле-ментов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 13 поступает сигнал логическая"1" с выхода элемента ИЛИ 12, инвертирующий выходной код параллельногоАЦП 7. На выходе шифратора 8 формиру.ется единица в младшем из щ старшихразрядов выходного. кода.При входном напряжении, превышающем значение 2 р, срабатывают первыйи второй компараторы. На выходе тре-.тьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 9 формируется управляющий сигнал,открывающий третий ключ, В результатенапряжение с выхода первого аналого"вого инвертера, определяемое как(2 р-Б ), поступает на вход параллельного АЦП 7,На выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы формируется логический "0", так как срабатывают первый и второй компараторы. При этом через элемент ИЛИ 13 выдается управляющий сигнал, обеспечивающий прохождение прямого кода с выхода параллельного АЦП 7 на формирование п младших разрядов. На выходе шифратора 8формируется единица во втором разряде.Аналогичным образом устройство работает при увеличении входного сигнала на последующих участках, т.е, реализуется амплитудная свертка сигнала на входе параллельного АЦП 7, При этом отпадает необходимость пре образования выходного кода в код Грея, а затем в двоичный код, что имеет место в известных последовательно-параллельных аналого-цифровых преобразователях. 15Формула изобретенияПараллельно-последовательный аналого-цифровой преобразователь, содер жащий и-разрядный параллельный аналого-цифровой преобразователь, где и - число младших разрядов. выходного двоичного кода, (2 -1) компараторов, где ш - число старших разрядов выход(м-иного двоичного кода, 2 формирователей разностного напряжения, первые. входы компараторов объединены с первыми входами формирователей разностного напряжения и являются входной 30 шиной, вторые входы компараторов соединены с соответствующими первыми выходами источника опорного сигнала, а выходы компараторов подключены к соответствующим входам шифратора выходы которого являются выходной шиной старших разрядов, вторые выходы источника опорного сигнала соединены с вторыми входами соответствующих формирователей разностного напряже ния, о т л и ч а ю щ и й с я тем, что, с целью повышения точности и быстродействия преобразования путем реализации амплитудной свертки сигнамла, в него введены .2 ключей, форми-. 45 ров. тель логического нуля, формпрова(м тель логической единицы, 2(- 1 аналоговых пннерторов, первая и вторая группы пз 2 и и элементов ИСКЛПОЧАЮ/ЩЕЕ ИЛИ соответственно, элемент И 1 И, при этом выходы ключей объединены и подключены к входу параллельного аналого-циФрового преобразователя, информационный вход первого ключа является входной шиной, информационные входы четных ключей соединены с выходами соответствующих формирователей раэностного напряжения с перво(м-го по 2 -й, а информационные входы ,нечетных ключей, кроме первого, соединены с выходами соответствующих аналоговых инверторов с первого по(м 2 -1-й, входы которых подключены к выходам одноименных формирователей разностного напряжения, управляющие входы ключей соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, первый вход 2 -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с выходом формирователя логического нуля, а выход 1-го компаратора, где 1=1,2,(2 -1), соединен с первым входом -го и вторым входом (1+)-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы подключен к выходу формирователя логической единицы, выходы четных элементов ИСКПЮЧАЮЩЕЕ ИЛИ первой группы подключены к соответствующим входам элемента ИЛИ, выход которого соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых подключены к соответствующим выходам параллельного аналого-цифрового преобразователя, а выходы являются соответствующей выходной шиной младших разрядов.1383500 Йх Зчцс Составитель Ю.Спи Техред И. Ходанич В.Бугренков Редак Заказ 1351 ног ении5, Ра Производственно-полиграАическое предприятие, г.ужгород, ул,Проектна Йк ди Тираж 92 ВНИИПИ Государстве цо делам изобре 113035, Москва, Ж доновКорректор И.Пилипен Подписомитета СССРоткрытийщская наб., д

СмотретьЗаявка

4081992, 06.05.1986

КОНСТРУКТОРСКОЕ БЮРО "ШТОРМ" ПРИ КИЕВСКОМ ПОЛИТЕХНИЧЕСКОМ ИНСТИТУТЕ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ТЕСЛЕНКО ВИКТОР АЛЕКСЕЕВИЧ, ГЛАДКОВ АЛЕКСЕЙ МИХАЙЛОВИЧ, ЛИТВИН АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 1/36

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 23.03.1988

Код ссылки

<a href="https://patents.su/4-1383500-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Преобразователь перемещения в код

Следующий патент: Каскадный аналого-цифровой преобразователь

Случайный патент: Супергетеродинный радиоприемник