Параллельно-последовательный аналого-цифровой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 407423

Авторы: Автор, Вьюхин, Электрометрии

Текст

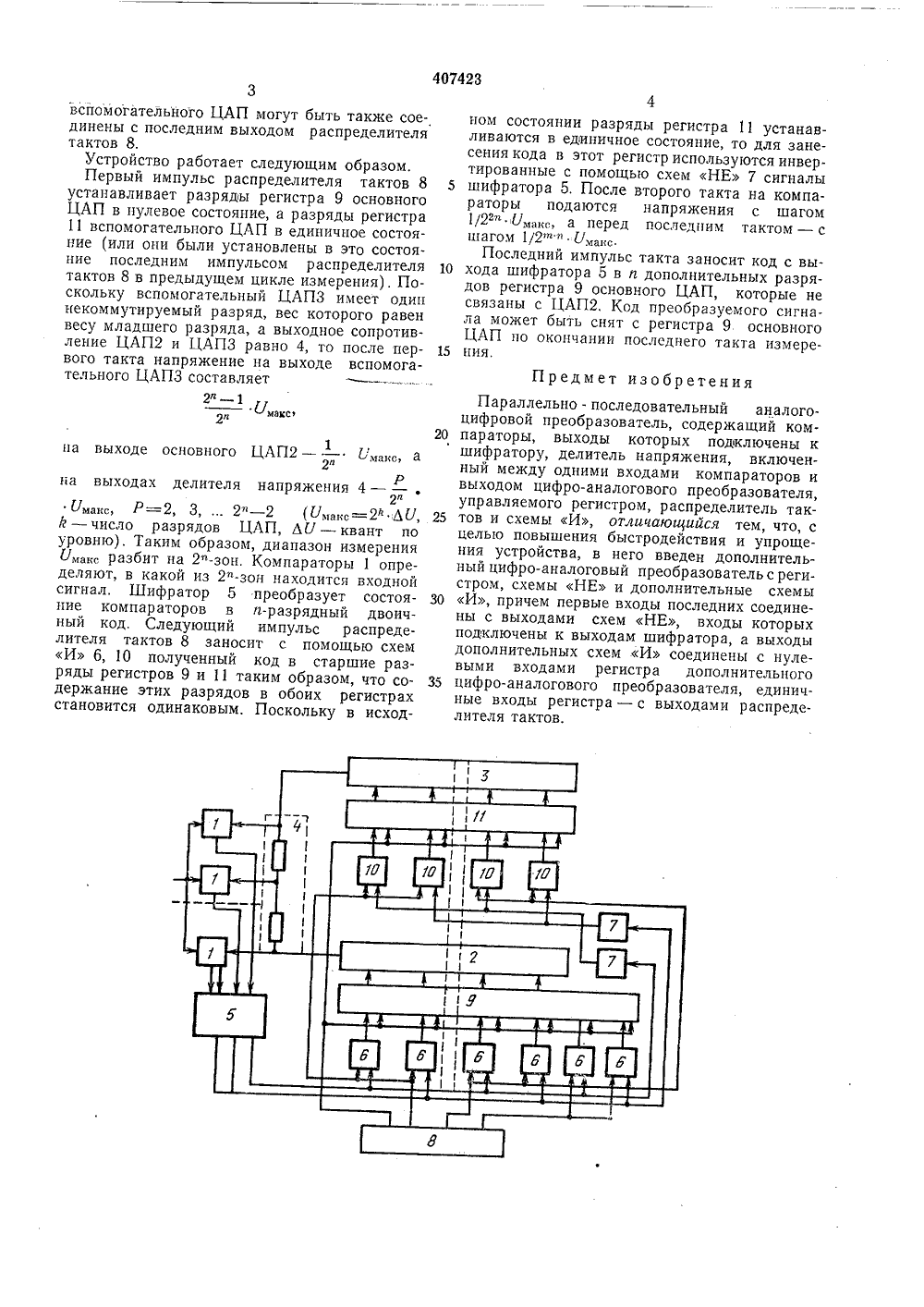

407423 НИЕ Союз СоветскихСоциалистическихРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ видетельства(Юе 1750718/26-9 ависимое от М,Кл. НОЗ Заявлено 23,11,197 присоединением заявкиосударственныи комитеСовета Министров СССРпо делам изобретенийи открытий иоритет У 325(088.1973. Бюллетень46 публиковано 21,Х ата опубликования описания 27.111.197т,. .,"д Авторизобретен. Н. Вью е отделение АН ССС Заявитель Институт автоматики и электрометрии С РАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВ ПРЕОБРАЗОВАТЕЛЬИзобретение относится к области электро- измерительной техники.Известен параллельно - последовательный аналого-цифровой преобразователь, содержащий компараторы, выходы которых подключены к шифратору, делитель напряжения, включенный между одними входами компараторов и выходом цифро-аналогового преобразователя, управляемого регистром, распределитель тактов и схемы И.Недостатком известного устройства является невысокое быстродействие и сложность в исполнении.Предлагаемое устройство отличается от известного тем, что в него введен дополнительный цифро-аналоговый преобразователь с регистром, схемы НЕ и дополнительные схемы И, причем первые входы последних соединены с выходами схем НЕ, входы которых подключены к выходам шифратора, а выходы дополнительных схем И соединены с нулевыми входами регистра дополнительного цифро-аналогового преобразователя, единичные входы регистра - с выходами распределителя тактов, что значительно повышает быстродействие и упрощает устройство,На чертеже дано предполагаемое устройство.Устройство содержит компараторы 1 (и-число одновременно определяемых двоичных разрядов), первые входы которых соединены с входным сигналом, вторые входы соединены с выходами основного и дополнительного цифро-аналогового преобразователей 2 и 3 и с выходами делителя напряжения 4, а выходы - со входами шифратора состояний компараторов 5. Выходы последнего соединены с входами т схем И 6 и и схем НЕ 7 (т - число тактов аналого-цифрового преобразователя).Вторые входы схем И 6 объединены группа 10 ми по п и соединены с соответствующими выходами распределителя тактов 8, а выходы схем И 6 соединены с единичными установочными входами регистра 9 основного цифроаналогового преобразователя (ЦАП), нулевые 15 установочные входы которого соединены спервым выходом распределителя тактов 8, а выходы соединены с входами основногоЦАП 2.Выходы схем НЕ 7 соединены с входами 20 схем И 10, вторые входы которых объедине.ны группами по и и соединены с соответствующими выходами распределителя тактов 8. Вы ходы схем И 10 соединены с нулевыми уста новочными входами регистра 11 вспомогатель.25 ного ЦАП, единичные установочные входы которого соединены с первым выходом распреде.лителя тактов 8, а выходы соединены с входами вспомогательного ЦАПЗ. Нулевые установочные входы регистра 9 основного ЦАП и 30 единичные установочные входы регистра 11вспомогательного ЦАП могут быть также соединены с последним выходом распределителя тактов 8.Устройство работает следующим образом.Первый импульс распределителя тактов 8 устанавливает разряды регистра 9 основного ЦАП в нулевое состояние, а разряды регистра 11 вспомогательного ЦАП в единичное состояние (или опи были установлены в это состояние последним импульсом распределителя тактов 8 в предыдущем цикле измерения) . Поскольку вспомогательный ЦАПЗ имеет один некоммутируемый разряд, вес которого равен весу младшего разряда, а выходное сопротивление ЦАП 2 и ЦАПЗ равно 4, то после первого такта напряжение на выходе вспомогательного ЦАПЗ составляет2" - 1 /макс 1на выходе основного ЦАП 2 --Гмакс а2 пР на выходах делителя напряжения 4 -- .2 п Умакс, Р=2, 3, 2 п - 2 (смак=2 ЛУ, й - число разрядов ЦАП, ЛУ - квант по уровню) . Таким образом, диапазон измерения /макс разбит на 2"-зон. Компараторы 1 определяют, в какой из 2"-зон находится входной сигнал. Шифратор 5 преобразует состояние компараторов в и-разрядный двоичный код. Следующий импульс распределителя тактов 8 заносит с помощью схем И 6, 10 полученный код в старшие разряды регистров 9 и 11 таким образом, что содержание этих разрядов в обоих регистрах становится одинаковым. Поскольку в исходном состоянии разряды регистра 11 устанавливаются в единичное состояние, то для занесения кода в этот регистр используются инвертированные с помощью схем НЕ 7 сигналы 5 шифратора 5, После второго такта на компараторы подаются напряжения с шагом 1/2 Смаке, а перед последним тактом - с шагом 1/2 п "/максПоследний импульс такта заносит код с вы хода шифратора 5 в и дополнительных разрядов регистра 9 основного ЦАП, которые не связаны с ЦАП 2, Код преобразуемого сигнала может быть снят с регистра 9 основного ЦАП по окончании последнего такта измере ния,Предмет изобретенияПараллельно - последовательный аналогоцифровой преобразователь, содержащий ком параторы, выходы которых подключены кшифратору, делитель напряжения, включенный между одними входами компараторов и выходом цифро-аналогового преобразователя, управляемого регистром, распределитель так тов и схемы И, отличающийся тем, что, сцелью повышения быстродействия и упрощения устройства, в него введен дополнительный цифро-аналоговый преобразователь с регистром, схемы НЕ и дополнительные схемы ЗО И, причем первые входы последних соединены с выходами схем НЕ, входы которых подключены к выходам шифратора, а выходы дополнительных схем И соединены с нулевыми входами регистра дополнительного 35 цифро-аналогового преобразователя, единичные входы регистра - с выходами распределителя тактов.

СмотретьЗаявка

1750718

Автор изобретени, Н. Вьюхин витель Институт автоматики, электрометрии Сибирское отделение СССР

МПК / Метки

МПК: H03M 1/34

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/2-407423-parallelno-posledovatelnyjj-analogo-cifrovojj.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой</a>

Предыдущий патент: Многоканальный усилитель

Следующий патент: Распределитель импульсов наборно-пишущего автомата

Случайный патент: Устройство для улавливания ленты ленточногоконвейера