Преобразователь выходных сигналов параметрических датчиков в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

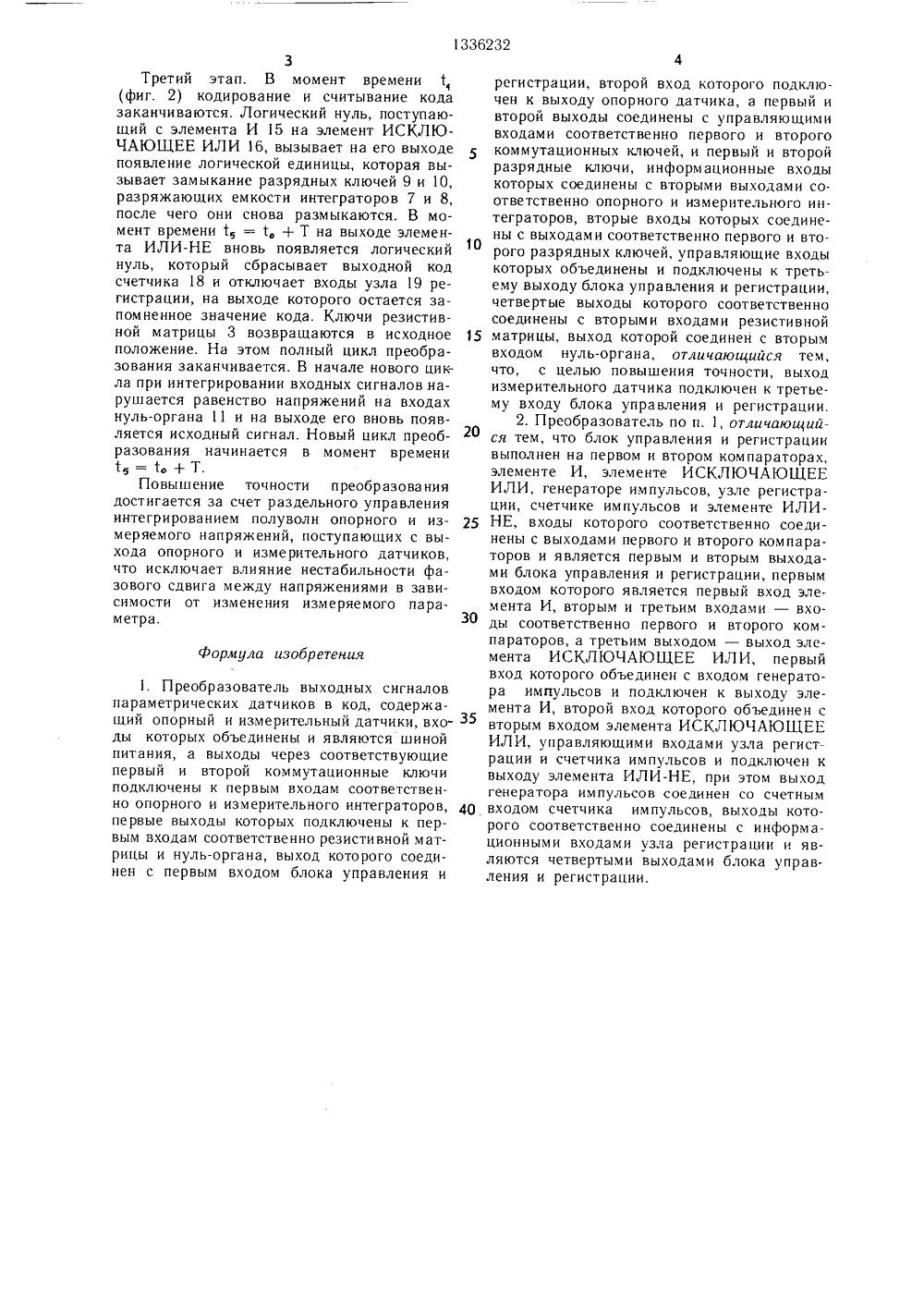

(56) Авторское398008, кл. о 33иациондзеи Г.А. юл. Мй аоникабин8.8)свиде03 и инсти Никола ельство СССРМ 1/00, 1969. Ь ВЫХОДНЫИЧЕС ИХ АТСУДАРСТВЕННЫЙ КОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение относится к технике аналого-цифрового преобразования и может быть использовано в измерительно-информационных системах и системах регулирования. Целью изобретения является повышение точности. Преобразователь работает циклически в соответствии с периодами тока, питающего опорный и измерительный датчики, на выходе которых формируются напряжения, сдвинутые по фазе. На первом,801336232 А 1 этапе осуществляется интегрирование положительных полуволн выходных напряжений датчиков с помощью опорного и измерительного интеграторов. На втором этапе, когда оба выходных напряжения датчиков становятся отрицательными, в блоке управления и регистрации осуществляется подсчет импульсов тактовой частоты с помощью счетчика импульсов, код с выхода которого управляет выходным сигналом резисти вной матрицы, на вход которой поступает сигнал с выходного опорного интегратора. При совпадении на нуль-органе сигналов с резистивной матрицы и измерительного интегратора подсчитанный код фиксируется и схема возвращается в исходное состояние, подготавливая новый цикл преобразования. При а этом точность повышается за счет раздельного управления интегрированием полуволн опорного и измеряемого напряжений, что исключает влияние нестабильности фазового сдвига в зависимости от величины измеряемого параметра. 1 з. и. ф-лы, 2 ил.Изобретение относится к технике аналого-цифрового преобразования и может быть использовано в измерительно-информационных системах регулирования с цифровыми регуляторами.Цель изобретения - повышение точности На фиг. 1 приведена структурная электрическая схема преобразователя; на фиг, 2 - временные диаграммы работы устройства.Преобразователь содержит опорный 1 и измерительный 2 датчики, резистивную матрицу 3, блок 4 управления и регистрации, коммутационные ключи 5 и 6, опорный 7 и измерительный 8 интеграторы с разрядными ключами 9 и 10, нуль-орган 11. Блок 4 управления и регистрации содержит компараторы 12 и 13, элемент ИЛИ-НЕ 14, элемент И 15, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, генератор 17 импульсов, счетчик 18 импульсов, узел 19 регистрации. Входы опорного 1 и измерительного 2 датчиков объединены и являются шиной 20 питания.Устройство работает циклически следующим образом.Каждый цикл преобразования равен одному периоду тока, питающего датчики по шине 20, и разбивается на три этапа. В исходном состоянии коммутационные ключи 5 и 6 разомкнуты и разрядные ключи 9 и 10 отключены, На выходе нуль-органа 11 присутствует логическая единица, В первичной цепи датчиков протекает ток 1 = 1 созыв.На первом этапе в момент времени (фиг. 2), когда напряжение на выходе одно. го из датчиков 1 уже равно нулю, а на выходе другого датчика 2 напряжение запаздывает по фазе, блок 4 управления и регистрации выходным напряжением одного из компараторов 12 замыкает ключ 5 и на вход интегратора 7 поступает напряжение с выходной обмотки датчика 1. Начинается интегрирование положительной полуволны синусоидального напряжения. В момент времени 1, (фиг, 2), когда напряжение на выходе датчика равно нулю, компаратор 13 замыкает ключ 6 и на интегратор 8 поступает напряжение с датчика 2, при этом начинается интегриро ва ние его положительной полу- волны. В момент 1 (фиг. 2), когда напряжение с выхода датчика 1 становится равным нулю, компаратор 12 размыкает ключ 5, и интегрирование напряжения на интеграторе 7 прекращается. На выходе интегратора 7 образуется напряжение 1.1, = .и 11 М А где М = сопз( - взаимная индуктивность между обмотками датчика; А, - масштабный коэффициент интегратора.В момент (, (фиг. 2), когда напряжение на выходе датчика 2 становится равным нулю, компаратор 13 размыкает ключ 6, прекращая интегрирование сигнала с датчика 2 на интеграторе 8. На выходе интегратора 8 5 1 О 15 20 25 30 35 40 45 50 55 2образуется напряжение 1.), =И 1 МА,где М = чаг - взаимная индуктивностьмежду обмотками датчика 2; А - масштабный коэффициент интегратора 8. На этомэтапе заканчивается цикл интегрированиявходных сигналов, Ключи 5 и 6 разомкнуты,на интеграторах 7 и 8 запоминаются напряжения 11, и 11.На втором этапе в момент времени 1, навходах обоих компараторов 12 и 13 напряжение равно логическому нулю и на выходеэлемента ИЛИ-НЕ 14 появляется сигнал,равный логической единице, Этот сигнал поступает на счетчик 18 разрешая счет, атакже поступает на узел 19 регистрации,разрешая прием кода со счетчика 18, поступает на один из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и на один из входов элемента И 15. На второй вход элемента И 15 подается сигнал логической единицы, который выдает нуль-орган 11 при раскоммутированных ключах резистивной матрицы 3 и неравенстве напряжений 11, и 11,.На выходе элемента И 15 появляется логическая единица, которая подается на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, на выходекоторого остается логический нуль (ключи 9и 10 остаются в исходном состоянии), атакже генератор 17 импульсов, который начинает вырабатывать импульсы, поступающие на счетчик 18 и преобразуемые им вкод. Выходному коду счетчика 18, которыйпередается на резистивную матрицу 3, однозначно соответствует положение коммутационных ключей матрицы. В процессе коммутации ключей на выходе резистивной матрицы 3 происходит изменение выходного сигнала.В момент времени 1(фиг. 2) при достижении равенства напряжений с выхода интегратора 8 и с выхода резистивной матрицы 3 поступающий на вход нуль-органа 11на его выходе сигнал изменяется с логической единицы на логический нуль, приводя кзакрыванию элемента И 15 и прекращениюработы генератора 17. Счетчик 18 останавливает счет и выдает на выходе код п, фиксирующийся в узле 19 регистрации и однозначно соответствующий положению ключей резистивной матрицы 3:2п=)(.ц =1 % цг 1 мМАг. к Мз ь , ,..ц.А к 4где 1 с = 1 с - ,- -- коэффициент пропорА,4 фМциональности. Величина кода и пропорциональна взаимной индуктивности обмотокизмерительного датчика 2 и не зависит отнестабильности напряжения питания и отфазового сдвига между выходными напряжениями датчиков, Поскольку взаимная индуктивность функционально связана с измеряемым параметром Х, код и однозначносоответствует параметру Х.3Третий этап. В момент времени 1, (фиг. 2) кодирование и считывание кода заканчиваются. Логический нуль, поступающий с элемента И 15 на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 16, вызывает на его выходе появление логической единицы, которая вызывает замыкание разрядных ключей 9 и 10, разряжающих емкости интеграторов 7 и 8, после чего они снова размыкаются. В момент времени 1 = 1, + Т на выходе элемента ИЛИ-НЕ вновь появляется логический нуль, который сбрасывает выходной код счетчика 18 и отключает входы узла 19 регистрации, на выходе которого остается запомненное значение кода. Ключи резистивной матрицы 3 возвращаются в исходное положение. На этом полный цикл преобразования заканчивается. В начале нового цикла при интегрировании входных сигналов нарушается равенство напряжений на входах нуль-органа 11 и на выходе его вновь появляется исходный сигнал. Новый цикл преобразования начинается в момент времени т = +Т.Повышение точности преобразования достигается за счет раздельного управления интегрированием полуволн опорного и измеряемого напряжений, поступающих с выхода опорного и измерительного датчиков, что исключает влияние нестабильности фазового сдвига между напряжениями в зависимости от изменения измеряемого параметра.Формула изобретения1, Преобразователь выходных сигналов параметрических датчиков в код, содержащий опорный и измерительный датчики, входы которых объединены и являются шиной питания, а выходы через соответствующие первый и второй коммутационные ключи подключены к первым входам соответственно опорного и измерительного интеграторов, первые выходы которых подключены к первым входам соответственно резистивной матрицы и нуль-органа, выход которого соединен с первым входом блока управления и10 15 регистрации, второй вход которого подключен к выходу опорного датчика, а первый и второй выходы соединены с управляющими входами соответственно первого и второго коммутационных ключей, и первый и второй разрядные ключи, информационные входы которых соединены с вторыми выходами соответственно опорного и измерительного интеграторов, вторые входы которых соединены с выходами соответственно первого и второго разрядных ключей, управляющие входы которых объединены и подключены к третьему выходу блока управления и регистрации, четвертые выходы которого соответственно соединены с вторыми входами резистивнойматрицы, выход которой соединен с вторым входом нуль-органа, отличающийся тем, что, с целью повышения точности, выход измерительного датчика подключен к третьему входу блока управления и регистрации.2. Преобразователь по п. 1, отличающийся тем, что блок управления и регистрации выполнен на первом и втором компараторах, элементе И, элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, генераторе импульсов, узле регистрации, счетчике импульсов и элементе ИЛИ НЕ, входы которого соответственно соединены с выходами первого и второго компараторов и является первым и вторым выходами блока управления и регистрации, первым входом которого является первый вход элемента И, вторым и третьим входами - входы соответственно первого и второго компараторов, а третьим выходом - выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого объединен с входом генератора импульсов и подключен к выходу элемента И, второй вход которого объединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющими входами узла регистрации и счетчика импульсов и подключен к выходу элемента ИЛИ-НЕ, при этом выход генератора импульсов соединен со счетным 40 входом счетчика импульсов, выходы которого соответственно соединены с информационными входами узла регистрации и являются четвертыми выходами блока управ.ления и регистрации.1336232 Иых Редактоор В. ПетрашЗаказ 3814/55ВНИИПИ Государственного ко113035,Москва,Производственно-полиграфич Составитель 8. ВотовТехред И. Верес Корректор Тираж 901 Подписное митета СССР по делам изобретений и Ж - 35, Раушская наб., д. 4/5 ское предприятие, г, Ужгород, ул. Пр А. Ильин ткрытнй ктная, 4

СмотретьЗаявка

4058751, 24.04.1986

УФИМСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. СЕРГО ОРДЖОНИКИДЗЕ

ТУРБАБИН ВЛАДИМИР НИКОЛАЕВИЧ, НИКОЛАЕВ ГЕРМАН АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 1/00

Метки: выходных, датчиков, код, параметрических, сигналов

Опубликовано: 07.09.1987

Код ссылки

<a href="https://patents.su/4-1336232-preobrazovatel-vykhodnykh-signalov-parametricheskikh-datchikov-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь выходных сигналов параметрических датчиков в код</a>

Предыдущий патент: Цифровой синтезатор частоты с частотной модуляцией

Следующий патент: Устройство для измерения дифференциальной нелинейности цифроаналоговых преобразователей

Случайный патент: Волновая электростанция