Устройство для дискретной регулировки фазы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1269051

Авторы: Макаровский, Николаев

Текст

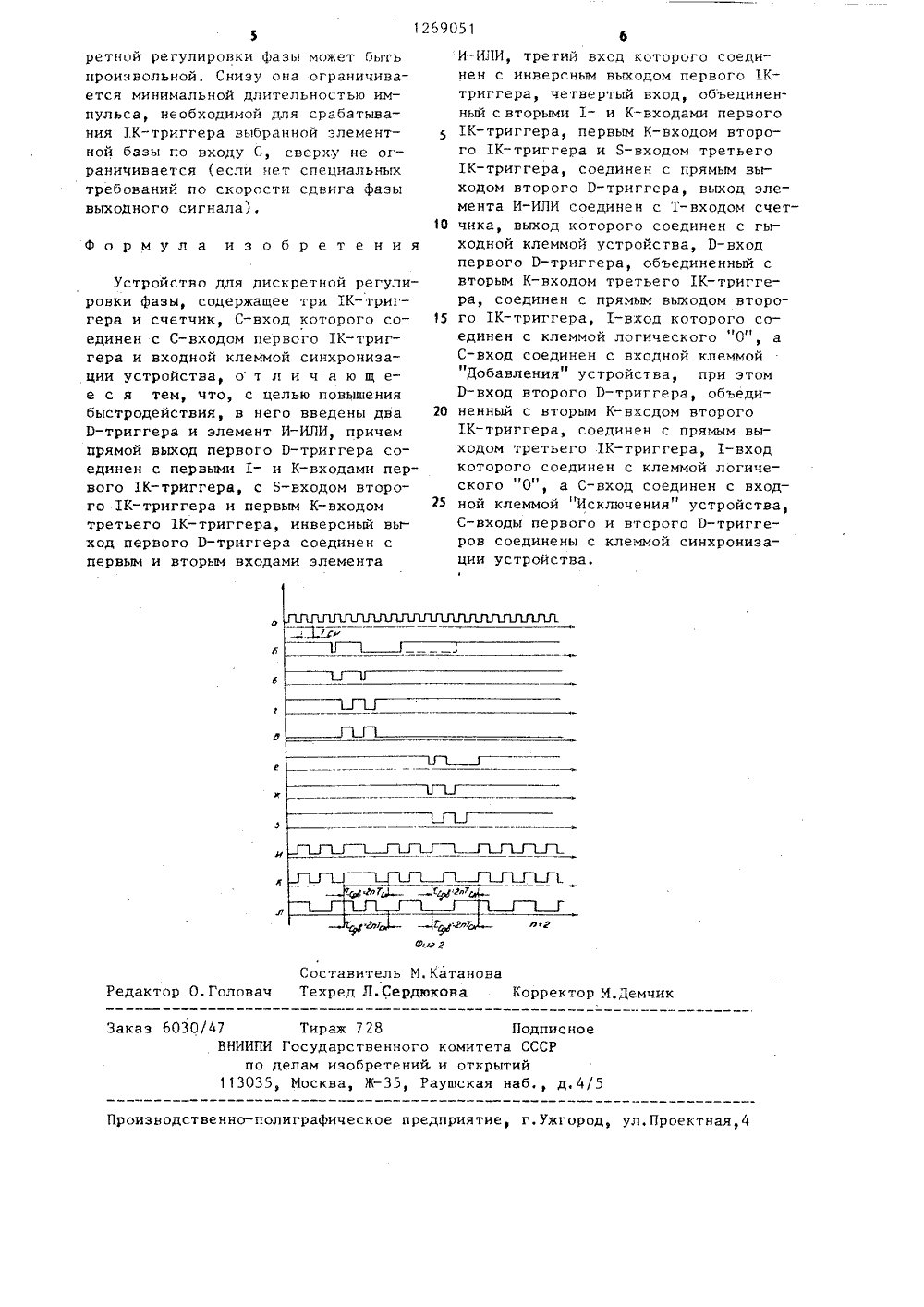

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 69051 А 1 не 8 1) 4 С 01 К 25/00 ИИ ли в ны Р-триггер Кроме того вве 1 ЛИ У3 и э ойст сч тваггеры 1, ствие ус ий рои- фазь акар ыстродеитной регпрототип иро тво ССС 00, 198 о СССР О, 1979 овышаетс о в 1,5 раза. Кро управляющих сиг того, длительностьов в устройстве гули ьной я дискретноит быть произв аничивается м тью импульса, атывания 1 К-т ентной базы п имальноеобходим бран све гера вы ходу С, сли нет оспециальныхвига фазы ограничиваетс требований по ости 2 и я цеыходного сигна Риг,ГОСУДАРСТВЕННЫИ КОМИТЕТ С ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКР ПИСАНИЕ ИЗОБРЕТЕ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(54) УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ РЕЛИРОВКИ ФАЗЫ(57) Изобретение относится к импусной технике и может быть использвано в системах цифровой обработкиналов. Целью изобретения является ишение быстродействия.Для достижени троиство емент И- о содерж тчик 2. ля дискр внению с ки фазы монизу она ог- длительноой для сраной эле 1269051Изобретение относится к импульсной технике и может быть использовано, в частности, в системах цифровойобработки сигналов.Цель изобретения - повышение быстродействия устройства.На фиг. приведена функциональнаясхема устройства; на фиг.2 - временные диаграммы работы устройства.Устройство для дискретной регулировки фазы содержит первый ЕК-триггер 1, счетчик 2 второй 3 и третий4 1 К-триггеры, первый 5 и второй 60-триггеры, элемент И-ИЛИ 7. Прямойвыходпервого 0-триггера 5 соединенс первыми 1- и К-входами первого1 К-триггера 1, объединенных с Б-входом второго 1 К-триггера 3 и первымК-входом третьего ЕК-триггера 4,инверсный выход первого 0-триггера 5соединен с первым и вторым входамиэлемента И-ИЛИ 7, третий вход которого соединен с инверсным выходомпервого 1 К-триггера 1, а четвертыйвход, объединенный с вторыми 1-иК-входами первого 1 К-триггера 1,первым К-входом второго 1 К-триггера 3и Б- входом третьего 1 К-триггера4, соединен с прямым выходом второго 0-триггера 6, выход элемента ИИЛИ 7 соединен с Т -входом счетчика2, выход которого соединен с выходной клеммой устройства, 0-вход первого 0-триггера 5, объединенный свторым К -входом третьего 1 К-триггера 4, соединен с прямым выходом второго 1 К-триггера 3, 1-вход которогосоединен с клеммой логического "О",а С-вход соединен с клеммой "Добавление" устройства, 0-вход второго0-триггера 6, объединенный с вторым-входом второго 1 К-триггера 3, соединен с прямым выходом третьего 1 Ктриггера 4, 1-вход которого соединенс клеммой логического О", а С-.входсоединен с клеммой нИсключение устройства. С-входы первого 1 К-триггера 1, счетчика 2, первого 5 и второго 6 0-триггеров объединены и соединены с клеммой "Синхронизация" устройства,Устройство работает следующим образом.На С-входы первого 1 К-триггера 1, счетчика 2, первого 5 и второго 6 0-триггеров поступают синхроимпульсы (эпюра а ,фиг.2), Пусть в исходном состоянии на прямых выходах втоО 15 20 25 30 35 40 45 50 рого 3 и третьего 4 1 К-триггеров присутствуют логические "1" (эпюры о иж, фиг.2). При этом на прямых выходах первого 5 и второго 6 0-триггеров также присутствуют логические "1"(эпюрыи 3 , фиг. 2), которые подтверждаются с приходом каждого очередного синхроимпульса и разрешают переключения первого 1 К-триггера 1. Устройство работает как обычный счетчик с коэффициентом деления 2 К, , где Кс коэффициент деления счетчика 2(эпюра Л, фиг.2, где К, = 2).При подаче на вход Добавление"о (эпюра 5 )логического "О" на прямом выходе 1 К-триггера 3 в ответ на перепад "1 - О" на его С-входе появляется логический "О" (эпюра 6, фиг. 2), так как на 1-входе - логический "О",на первом и втором К -входах - логические "1" (эпюры ж и 3, фиг.2). Логический О с выхода ЕК-триггера 3 поступает на второй 1 -вход 1 К-триггера 4, блокируя работу устройства по входу Исключение Е . Очередным синхроимпульсом этот логический "О" вписывается в 0-триггер 5. При этом на прямом выходе 0-триггера 5 появляется уровень логического О" (эпюра 1,фиг, 2), который, поступая на Б-вход 1 К- триггера 3, возвращает его в состояние логической "1" (эпюра 6, фиг.2), одновременно блокируя устройство по входу ДобавлениеБ , а также, поступая на первый К-вход 1 К-триггера 4, продолжает блокировку устройства по входу "Исключение" е, Следующим синхроимпульсом 0-триггер 5 возвращается в исходное состояние. (эпюра), так как на его 0-входе в этот момент уже логическая "1" с выхода 1 К-триггера 3 (эпюра 5, фиг,2). Появившаяся на прямом выходе 0-триггера 5 логическая "1" (эпюра 1 ,фиг.2), поступая на Б-вход 1 К-триггера 3 и на второй К-вход 1 К-триггера 4, разблокирует устройство, разрешая работу по управляющим входам Добавление" о и "Исключение" е - устройство возвращается в исходное состояние,Таким образом, на прямом (инверсном) выходе 0-триггера 5 в ответ на появление логического О на входе "Добавление" о устройства (эпюра 3, фиг.2) вырабатывается. отрицательный (положительный) импульс, длитель,ностью в период синхрочастоты Тстрого привязаный к ее активным пе. репадам (эпюра д, фиг.2).Отрицательный импульс с прямого выхода Р-триггера 5, поступая на первые 1- и К-входы 1 К-триггера(эпю ра 1, фиг,2), запрещает изменение состояния 1 К-триггерапри приходе очередного синхроимпульса (эпюра и фиг.2).Сигнал с инверсного выхода 1 К- О триггера(эпюра и ,фиг,2) поступает на третий вход элемента И-ИЛИ 7, где складывается с положительным импульсом с инверсного выхода Р-триггера 5 (эпюра д ,фиг.2), поступающим 5 на первый и второй входы элемента И-ИЛИ 7. Полученный в результате этого уровень логической (эпюра К, фиг.2) поступает с выхода элемента И;ИЛИ 7 на Т-вход счетчика 2, разре шая ему изменять свое состояние при приходе очередного синхроимпульса на С-вход (эпюра и,фиг,2), чего не произошло бы на рассматриваемом такте 1синхрочастоты в случае, если бы на 25 вход "Добавление" Б не был бы подан логический уровень "О". Таким образом, в результате подачи логического уровня "О" на вход 30 "Добавление" 1 фаза выходного сигнала счетчика (эпюра Л ) изменяется (ускоряется) на 2 ц/ 2 КПри подаче логического уровня О"на вход "Исключение" е (эпюра е, 35фиг.2) на прямом выходе 1 К-триггера4 в ответ на перепад " Ь" на егоС-входе появляется логический О"(эпюра ж, фиг,2), так как на 1 в входе - л тический "О", на первом и вто ром К-входах - логические " (эпюраи , фиг.2). Логический "О" свыхода 1 К-триггера 4 поступает навторой К -вход 1 К-триггера 5, блокируя работу устройства по входу "Добавление" Е . Очередным синхроимпульсом этот логический "О" вписывает -ся в Р-триггер б. При этом на прямомвыходе Р-триггера 6 появляется уровень логического "О" (эпюра з, фиг, 502), который, поступая на Я-вход 1 Ктриггера 4, возвращает его в состояние логической (эпюра )К ,фиг.2),одновременно блокируя устройство повходу Исключение" еа также поступая на первый К -вход 1 К-триггера3, продолжает блокировку устройства.по входу Добавление" Ь,Следующим синхроимпульсом Р-триггер б возвращается в исходное состояние (эпиюра, фиг.2), так как на его Р-входе в этот момент уже логическая с выхода 1 К-триггера 4 (эпюра , фиг.2), Появившаяся на прямом выходе Р-триггера 6 логическая (эпюра" фиг,2),поступая на Я-вход 1 К-триггера 4 и на второй К-вход 1 К-триггера 3, разблокирует устройство, разрешая работу по управляющим входам "Добавление" Р и "Исключение" е , устройство возвращается в исходное состояние.Таким образом, на прямом выходе Р-триггера 6 в ответ на появление логического "О на входе "Исключениенустройства (эпюра е, фиг.2) вырабатывается отрицательный импульс, длительностью в период синхрочастоты Тси , строго привязанный к ее активным перепадам (эпюра, фиг.2).Отрицательный импульс с прямого выхода Ъ-триггера 6, поступая на вторые 1- и К-входы ЕК-триггера(эпюра 3, фиг.2), запрещает изменение состояния 1 К-триггераприприходе очередного синхроимпульса (эпюра и , фиг,2).Сигнал с инверсного выхода 1 К- триггера (эпюра и , фиг.2) поступает на третий вход элемента И-ИЛИ 7, где перемножается с отрицательным импульсом с прямого выхода Р-триггера 6 (эпюра 3 , фиг.2), поступающим на четвертый вход элемента И-ИЛИ 7. Полученный в результате этого уровень логического "О" (эпира к, фиг. 2) поступает с выхода элемента И-ИЛИ 7 на Т - вход счетчика 2, запрещая ему изменять свое состояние при приходе очередного.синхроимпульса на С -вход (эпюра П , фиг.2), чего не произошло бы на рассматриваемом такте синхрочастоты в случае, если бы на вход "Исключение" е не был бы подан логический уровень "О".Таким образом, в результате подачи логического уровня "О" на вход "Исключение"е , фаза выходного сигнала счетчика 2 (эпюра д, фиг.2) изменяется (замедляется) на 23 Г(2 К,Таким образом, быстродействие устройства для дискретной регулировки фазы в ,5 раза вьппе, чем у известного.Кроме того, длительность управляющих сигналов в устройстве для диск1269051 ставитель М.Катанохред П.Сердюкова дактор О.Голов Корректор М,Демч аказ 6030/ аж 728 Под рственного комитета СС зобретений,и открытий а, 31-35, Раушская наб,Ти осу лам Мос но ИИПИ по 3035.твенно-полиграФическое предприятие, г,Ужгород, ул,Проектная,4 Прои ретной регулировки Фазы может быть произвольной. Снизу она ограничивается минимальной длительностью импульса, необходимой для срабатывания 1 К-триггера выбранной элементной базы по входу С, сверху не ограничивается (если нет специальных требований по скорости сдвига фазы выходного сигнала). формула изобретения Устройство для дискретной регулировки фазы, содержащее три 1 К-триггера и счетчик, С-вход которого соединен с С-входом первого 1 К-триггера и входной клеммой синхронизации устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, в него введены два Р-триггера и элемент И-ИЛИ, причем прямой выход первого Р-триггера соединен с первыми 1- и К-входами первого 1 К-триггера, с Б-входом второго 1 К-триггера и первым К-входом третьего 1 К-триггера, инверсный выход первого Р-триггера соединен с первым и вторым входами элемента И-ИЛИ, третий вход которого соединен с инверсным выходом первого 1 К- триггера, четвертый вход, объединенный с вторыми 1- и К-входами первого 1 К-триггера, первым К-входом второго 1 К-триггера и Б-входом третьего 1 К-триггера, соединен с прямым выходом второго Р-триггера, выход элемента И-ИЛИ соединен с Т-входом счет- О чика, выход которого соединен с гыходной клеммой устройства, Р-вход первого Р-триггера, объединенный с вторым К-входом третьего 1 К-триггера, соединен с прямым выходом второ го 1 К-триггера, 1-вход которого соединен с клеммой логического 0", а С-вход соединен с входной клеммойДобавления" устройства, при этом Р-вход второго Р-триггера, объеди ненный с вторым К-входом второго1 К-триггера, соединен с прямым выходом третьего 1 К-триггера, 1-вход которого соединен с клеммой логического 0", а С-вход соединен с вход ной клеммой "Исключения" устройства,С-входы первого и второго Р-триггеров соединены с клеммой синхронизации устройства.3

СмотретьЗаявка

3933112, 23.07.1985

ПРЕДПРИЯТИЕ ПЯ В-2203

НИКОЛАЕВ АЛЕКСАНДР НИКОЛАЕВИЧ, МАКАРОВСКИЙ АЛЕКСАНДР СЕРГЕЕВИЧ

МПК / Метки

МПК: G01R 25/00

Метки: дискретной, регулировки, фазы

Опубликовано: 07.11.1986

Код ссылки

<a href="https://patents.su/4-1269051-ustrojjstvo-dlya-diskretnojj-regulirovki-fazy.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для дискретной регулировки фазы</a>

Предыдущий патент: Способ оценки амплитудно-фазовой погрешности фазометров

Следующий патент: Преобразователь параметров комплексных сопротивлений в напряжение

Случайный патент: Устройство для испытания тары на герметичность