Устройство компенсации межсимвольной интерференции многоуровневых сигналов в каналах передачи данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

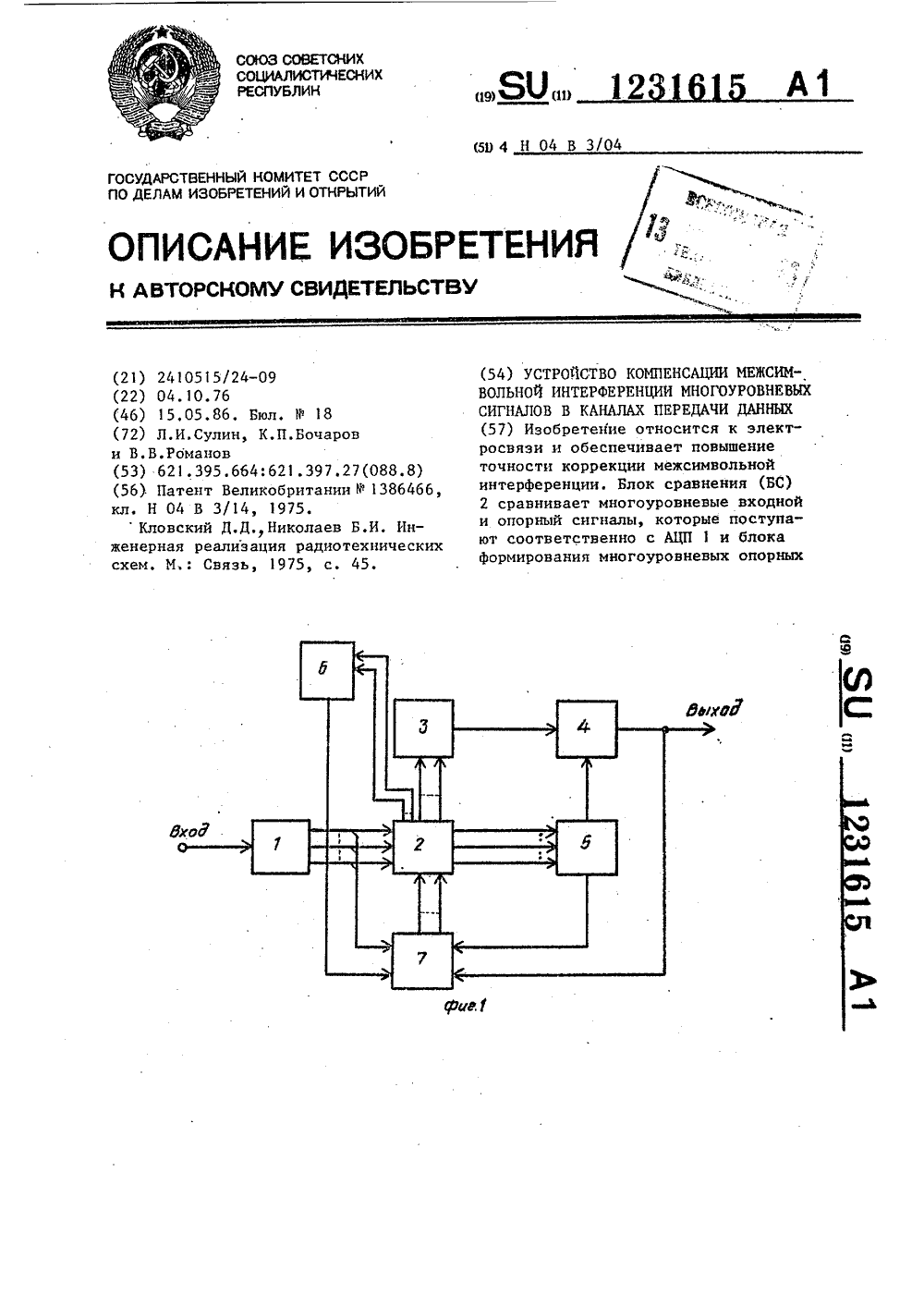

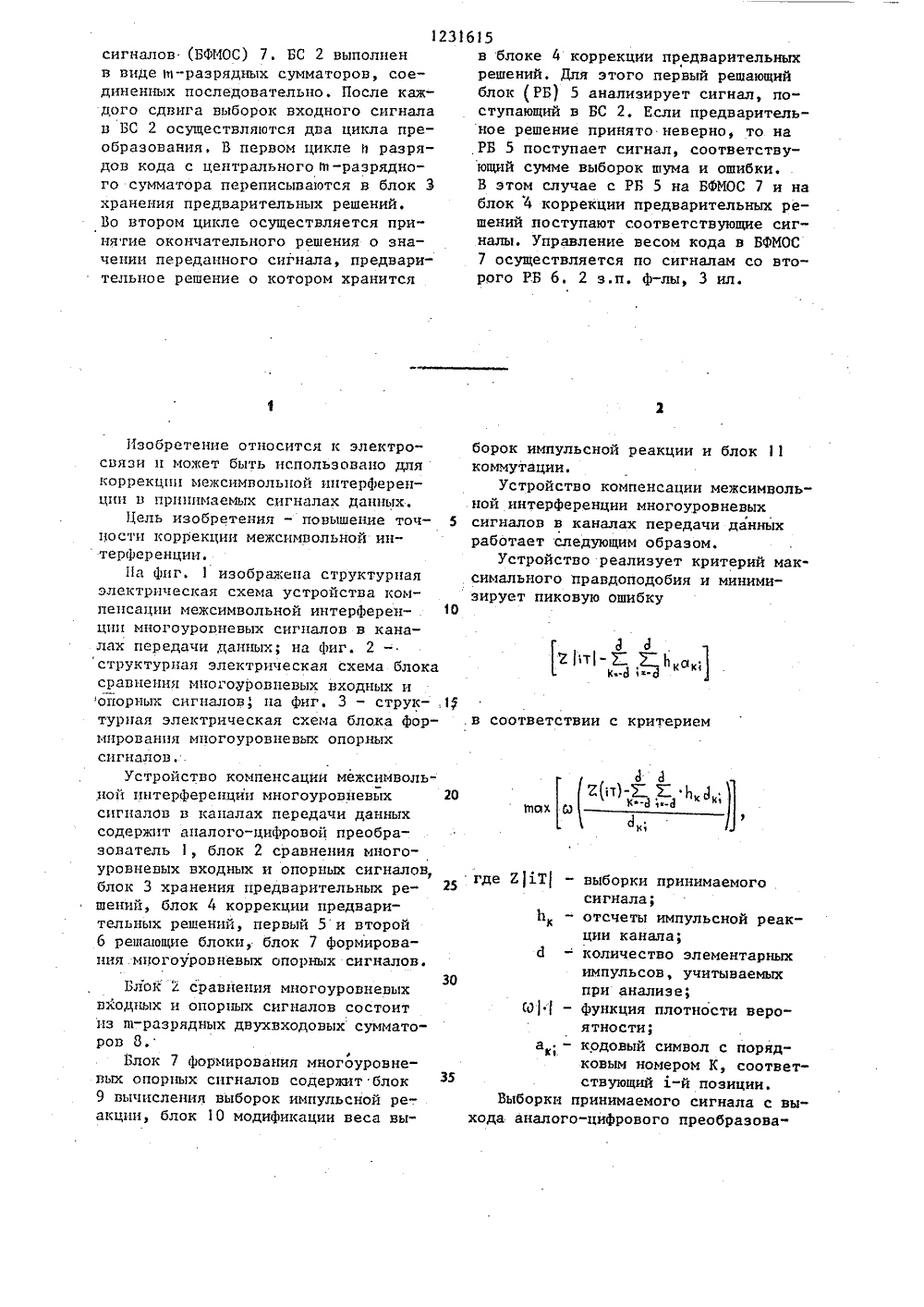

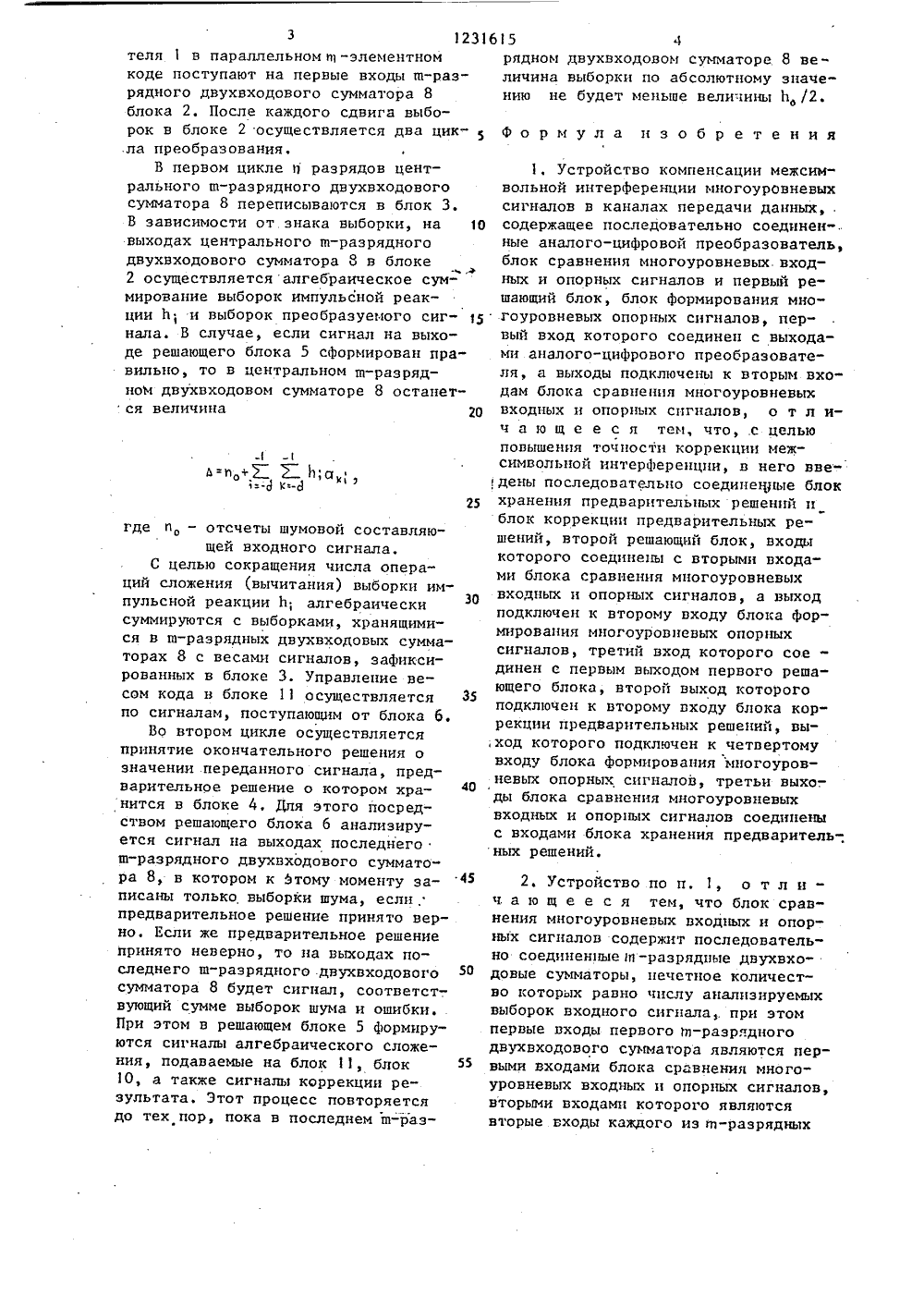

(19) (И) А 1 504 Н 04 В 3/04 ПИСАНИЕ ИЗОБРЕТЕНИ СВИ ЕТЕЛЬСТВУ К АВТОРСК хем. М,УДАРСТВЕННЫЙ НОМИТЕТ СССРделАм изОБРетений и ОтнРытий 515/24-090.765,86, Бюл. Ф 18Сулин, К,П.Бочарованов395.664:621.397.27(088.8нт Великобритании Р 13864В 3/14, 1975.ий Д.Д. Николаев Б.И. Инреализация радиотехничесСвязь, 1975, с. 45.(54) УСТРОЙСТВО КОМПЕНСАЦИИ МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ МНОГОУРОВНЕВЫХСИГНАЛОВ В КАНАЛАХ ПЕРЕДАЧИ ДАННЫХ(57) Изобретение относится к электросвязи и обеспечивает повышениеточности коррекции межсимвольнойинтерференции. Блок сравнения (БС)2 сравнивает многоуровневые входнойи опорный сигналы, которые поступают соответственно с АЦП 1 и блокаформирования многоуровневых опорных1 сигналов (БФМОС) 7, БС 2 выполнен в виде в-разрядных сумматоров, соединенных последовательно, После каждого сдвига выборок входного сигнала в БС 2 осуществляются два цикла преобразования, В первом цикле И разрядов кода с центрального в -разрядного сумматора переписываются в блок 3 хранения предварительных решений. Во втором цикле осуществляется при" нятие окончательного решения о значении переданного сигнала, предварительное решение о котором хранится 231615в блоке 4 коррекции предварительныхрешений. Для этого первый решающийблок ( РБ) 5 анализирует сигнал, поступающий в БС 2. Если предварительное решение принято неверно, то наРБ 5 поступает сигнал, соответствующий сумме выборок шума и ошибки.В этом случае с РБ 5 на БФМОС 7 и наблок 4 коррекции предварительных решений поступают соответствующие сигналы. Управление весом кода в БФМОС7 осуществляется по сигналам со второго РБ 6. 2 з.п. Ф-лы, 3 ил.Блок 2 сравйения многоуровневых входных и опорных сигналов состоит из ш-разряддых двухвходовых сумматоров 8.Блок 7 Формирования многоуровневых опорддых сигналов содержит блок 9 вычисления выборок импульсной ре-. акции, блок 10 модификации веса вы 30 35 Изобретение относится к электро" связи и может быть использовано для коррекции межсимвольной интерференции в принимаемых сигналах данных.Цель изобретения - повышение точ ности коррекции межсимвольной интерференции.1 а Фиг, 1 изображена структурная электрическая схема устройства компепсации межсимвольной интерферен ции многоуроцневых сигналов в каналах передачи данных; на Фиг. 2 - структурная электрическая схема блока сравнения многоуровневых входных и опорных сигналов, па фиг. 3 - струк- .1 туриая электрическая схема блока формирования многоуровневых опорных сигналовУстройство компенсации межсимвольной интерФеренции многоуровневых 20 сигналов в каналах передачи данных содеридт аналого-цифровойд преобразователь 1, блок 2 сравнения многоуровневых входных и опорных сигналов, блок 3 хранения предварительных решений, блок 4 коррекции предварительных решений, первый 5 и второй 6 решающие блоки, блок 7 Формирования многоуровневых опорных сигналов.борок импульсной реакции и блок 1 коммутации.Устройство компенсации межсимвольной интерференции многоуровневых сигналов в каналах передачи данных работает следующим образом.Устройство реализует критерий максимального правдоподобия и минимизирует пиковую ошибку2 Т 1-2-, йкак в соответствии с критерием3е(п)-Е. Е 1,3; мах и х -,1; к к 11 к, где ЕТ " выборки принимаемогосигнала; 1 д - отсчеты импульсной реакции канала; д - количество элементарных импульсов, учитываемых при анализе; Ю 1- Функция плотности вероятности; а - кодовый символ с порядковым номером К, соответствующий -й позиции. Выборки принимаемого сигнала с выхода аналого-цифрового преобразова 3 1231 теля 1 в параллельном щ -элементном коде поступают на первые входы щ-разрядного двухвходового сумматора 8 блока 2. После каждого сдвига выборок в блоке 2 осуществляется два цик ла преобразования.В первом цикле О разрядов центрального щ-разрядного двухвходового сумматора 8 переписываются в блок 3. В зависимости от знака выборки, на 10 выходах центрального щ-разрядного двухвходового сумматора 8 в блоке-ъ .Ф 2 осуществляется алгебраическое суммирование выборок импульсной реакции 1 д; и выборок преобразуемого сиг" 15 нала. В случае, если сигнал на выходе решающего блока 5 сформирован правильно, то в центральном щ-разрядном двухвходовом сумматоре 8 останется величина 20ь=д с С 11;адзк"-С 1 25где и, - отсчеты шумовой составляю"щей входного сигнала.С целью сокращения числа операций сложения (вычитания) выборки импульсной реакции Ь; алгебраически суммируются с выборками, хранящимися в пд-разрядных двухвходовых сумматорах 8 с весами сигналов, зафиксированных в блоке 3. Управление весом кода в блоке 11 осуществляется 35 по сигналам, поступающим от блока 6.Во втором цикле осуществляется принятие окончательного решения о значении переданного сигнала, предварительное решение о котором хра О нится в блоке 4. Для этого посредством решающего блока 6 анализируется сигнал на выходах последнего ш-разрядного двухвходового сумматора 8, в котором к этому моменту за писаны только выборки шума, если, предварительное решение принято верно, Если же предварительное решение принято неверно, то ца выходах последнего ш-разрядного двухвходового сумматора 8 будет сигнал, соответст-. вующий сумме выборок шума и ошибки. При этом в решающем блоке 5 формируются сигналы алгебраического сложения, подаваемые на блок 1, блок 1 О, а также сигналы коррекции результата, Этот процесс повторяется до тех пор, пока в последнем щ-раз 615 4рядном двухвходовом сумматоре 8 величина выборки по абсолютному значению не будет меньше величины Ь /2.Формула изобретения1, Устройство компенсации межсимвольной интерференции многоуровневых сигналов в каналах передачи данных, .содержащее последовательно соединен".ные аналого-цифровой преобразователь, блок сравнения многоуровневых входных и опорных сигналов и первый решающий блок, блок формирования мно" гоуровневых опорных сигналов, первый вход которого соединен с выходами аналого-циФрового преобразователя, а выходы подключены к вторым входам блока сравнения многоуровневых входных и опорных сигналов, о т л ич а ю щ е е с я теи, что, .с целью повышения точддостд коррекции межсимвольной интерференции, в него вве дены последовательцо соедине 1 дые блок хранения предварительных решений цМблок коррекции предварительных решений, второй решающий блок, входы которого соединедды с вторыми входами блока сравнения многоуровневых входных и опорных сигналов, а выход подключен к второму входу блока формирования многоуровневых опорных сигналов, третий вход которого сое - динен е первым выходом первого решающего блока, второй выход которого подключен к второму входу блока коррекции предварительных решений, вы,ход которого подключен к четвертому входу блока формирования ицогоуровневых опорных сигналов, третьи выхо-.ды блока сравнения многоуровневых входных и опорных сигналов соединены с входами блока хранения предваритель-, ньдх решений.2. Устройство по п, 1, о т л и " ч. а ю щ е е с я тем, что блок сравнения многоуровневых входных и опорных сигналов содержит последовательно соединенные дп -разрядные двухвходовые сумматоры, цечетцое количество которых равно числу анализируемых выборок входного сигнала,. при этом первые входы первого ддд-разрядддого двухвходового сумматора являются первыми входами блока сравнения многоуровневых входных и опорных сигналов, вторыми входами которого являются вторые входы каждого из ддд-разрядных1231 б 15 Ф 7 АЗель Ш,ЭвьянГортвай, Коррек стави едактор А.Рев Л.Пилипен ехре аз 2 бб 2/58 Тираж 624 НИИПИ Государств по делам изобре 35, Иосква, ЖПодписнонного комитета СССений и открытийРаушская наб., д,Производственно-полиграфическое предприятие, г. ул. Проектная,двухвходовых сумматоров, выходы (и++1) старших разрядов центрального,й-разрядного двухвходового сумматораявляются первыми выходами блока сравнения многоуровневых входных и опор-ных сигналов, вторыми выходами которого являются выходы последнегоФ-разрядного двухвходового сумматора,а третьими выходами являются выходып разрядов и)-разрядного двухвходово-го сумматора, предшествующего центральному,3. Устройство по п. 1, о т л и -ч а ю щ е е с я тем, что блокформирования многоуровневых опорныхсигналов содержит последовательносоединенные блок вычисления выборокФ импульсной реакции, вход которого является первым входом блока формирования многоуровневых опорных сигналов, блок модификации веса выборок импульсной реакции и блок коммутации, В-разрядный выход которого является выходом блока формирования многоуровневых опорных сигналов, вторым вхо О дом которого являются объединенныевторой вход блока модификации веса выборок импульсной реакции и второй вход блока коммутации, третий вход.которого является третьим входом бло ка формирования многоуровневых опорных сигналов, четвертым входом которого является третий вход блока модификации веса выборок импульсной реакции.

СмотретьЗаявка

2410515, 04.10.1976

ВОЕННАЯ ОРДЕНА ЛЕНИНА КРАСНОЗНАМЕННАЯ АКАДЕМИЯ СВЯЗИ ИМ. С. М. БУДЕННОГО

СУЛИН ЛЕВ ИППОЛИТОВИЧ, БОЧАРОВ КОНСТАНТИН ПАВЛОВИЧ, РОМАНОВ ВИКТОР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04B 3/04

Метки: данных, интерференции, каналах, компенсации, межсимвольной, многоуровневых, передачи, сигналов

Опубликовано: 15.05.1986

Код ссылки

<a href="https://patents.su/4-1231615-ustrojjstvo-kompensacii-mezhsimvolnojj-interferencii-mnogourovnevykh-signalov-v-kanalakh-peredachi-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство компенсации межсимвольной интерференции многоуровневых сигналов в каналах передачи данных</a>

Предыдущий патент: Приемо-передающий модуль

Следующий патент: Способ измерения амплитудно-частотной характеристики тракта связи

Случайный патент: Способ защиты трехфазного потребителя от изменения чередования и обрыва фаз и устройство для его осуществления