Устройство для суммирования -разрядных последовательно поступающих чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

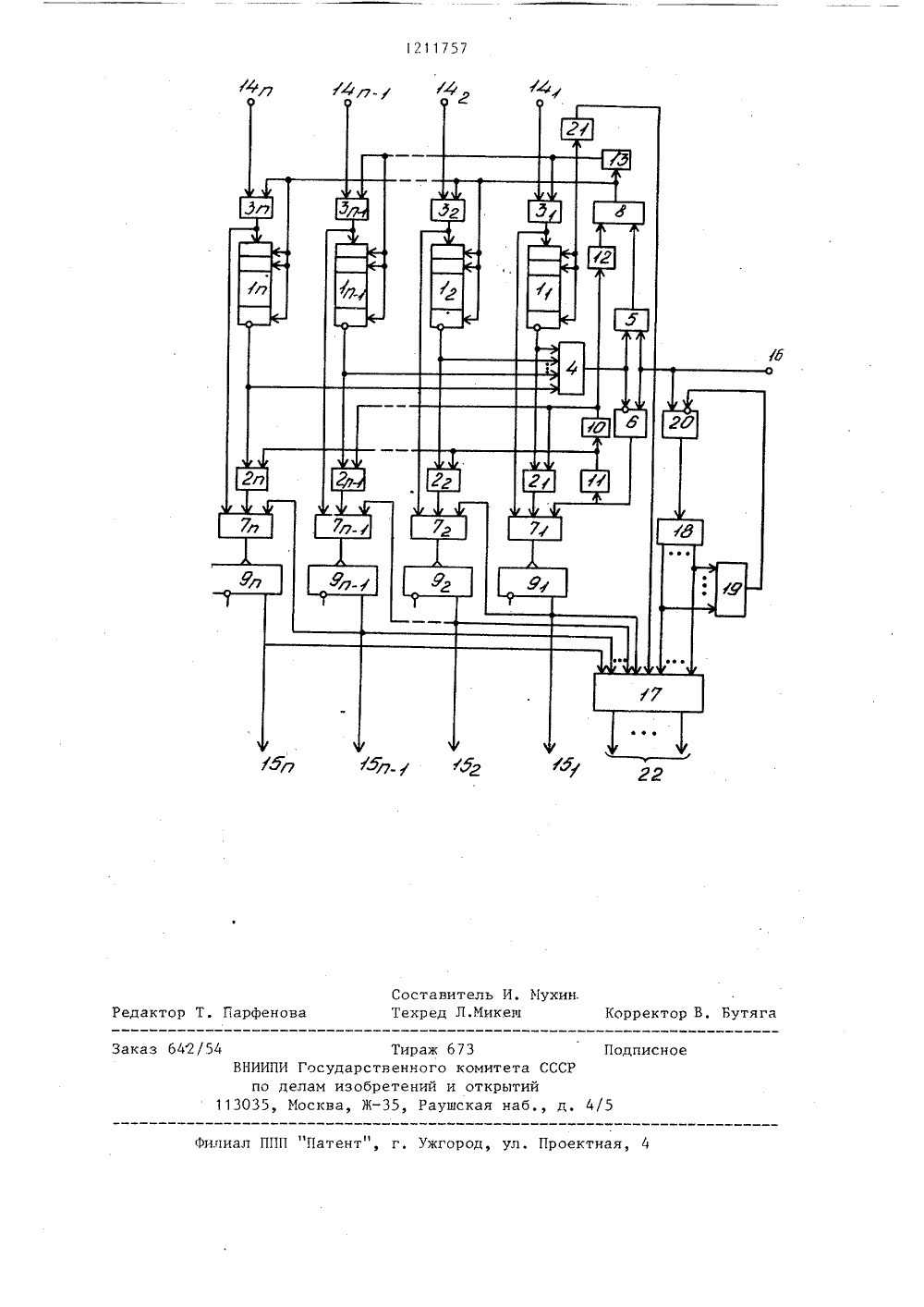

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 511 с С 06 Р 15/3 РЕТ а ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗ ВТОРСНОМУ СВИДЕТЕЛЬСТВ(54)(57) УСТРОЙСТВО ДЛЯ СЛМИРОВАНИЯМ и -РАЗРЯДНЫХ. ПОСЛЕДОВАТЕЛЬНО ПОСТУЛАЮЩИХ ЧИСЕЛ по авт.св.91075260,о т л и ч а ю щ е е с я тем, что,с целью расширения функциональныхвозможностей за счет определенияскользяшего среднего, в него введеныблок деления, дешиАратор, счетчик,дополнительный элемент запрета, пятьщ элемент задержки, вход которого соединен с выходом четвертого элемента задержки, выход пятого элементазадержки подключен к входу синхронизации блока деления, вход 1 -го(=1-и) разряда первой группы входовкоторого соединен с прямым выходом-го триггера, вход-го разряда второй группы входов блока деления обьединен с-м входом дешиАратора и подключен к-му выходу счетчика, счетный вход которого соединен с выходомдополнительного элемента запрета, инверсный вход которого подключен квыходу дешиАратора,прямой вход дополнительного элемента запрета соединенс тактовым входом устройства, выходблока деления является выходом скользящего среднего устройства,Изобретение относится к вычислительной технике и может быть испольезовано в устройствах статистическойобработки информации.Цель изобретения - расширение функциональных возможностей устройства засчет обеспечения вычисления математического ожидания а п -разрядных последовательно поступающих чисел.На чертеже представлена схема устройства,Устройство содержит сдвигающиерегистры 1, -1, группы элементовИ 21-2 и 3,-3 элементы И 4 и 5,элемент запрета 6, группу элементовИЛИ 7, -7 элемент ИЛИ 8, группусчетных триггеров 9, -9, элементы задержки 10-13, информацйонные входы141 ввыходы 15, -15 1 разрядовсуммы, тактовый вход 16, блок деления 2017, счетчик 18, дешифратор 19, элемент запрета 20, элемент задержки21, группу информационных выходов 22.Устройство работает следующим образом, 25В исходном состоянии в регистрах11-1 1 записаны нули, следовательно,по одному входу открыт элемент И 5,триггеры 91-9 , счетчик 18 - в нулевом состоянии, следовательно, на выходе дешифратора 19 числа в низкийпотенциал, и элемент запрета 20открыт. Первый импульс, поступающийна тактовый вход 16, через элементзапрета 20 поступает на счетный вход35счетчика 18, переключая его в состояние "1", а через элементы И 5 иИЛИ 8 поступает на вторые входы элементов И 3 -3 четных разрядов, прогизводят сдвиг в регистрах 1 гчетных разрядов и запись четных разрядовпервого числа в эти регистры, атакже через элементы ИЛИ 7 г -7 втриггеры 9 ги, Этот же импульсчерез элемент задержки 13 по 45ступает на первые входы элементовИ З,-Э, нечетных разрядов, производит сдвиг в регистрах 1, -1 1 нечетных разрядов и запись нечетных разрядов первого числа в эти регистры,а также через элементы ИЛИ 7, -7втриггеры 9,-9. Следовательно, впервых разрядах регистров 11-1 ив триггерах 91 в .9записывается первоечисло из непрерывно поступающей последовательности чисел. Этот же тактовый импульс через элемент задержки21 поступает на вход синхронизацииблока деления 17, в котором вычисляется математическое ожидание;/м 1(в данном случае щ =1), и на выходах22 устройства находится значение поступившего числа.Второй тактовый импульс черезэлемент запрета 20 поступает на счетный вход счетчика 18, переключая егов состояние "2", а через элементыИ 5 и ИЛИ 8 поступает на вторые входы элементов И 3 -3 четных разрядов,производит сдвиг в регистрах 1 -1и запись четных разрядов второгочисла в эти регистры, а также .обеспечивает их поступление через элементыИЛИ 7 -7 на счетные входы триггеИров 9 -9 четных разрядов. При поступлении четных разрядов второго числапроисходит их сложение с четными разрядами первого числа, записанногов триггерах 91-9, следующим образом:при поступлении "0" состояние триггера не меняется, а при поступлении"1" состояние триггера изменяетсяна противоположное, причем при пере"ходе триггера из единичного в нулевое состояние на единичном выходеэтого триггера появляется сигналпереноса в следующий разряд, которыйсуммируется со значением этого разряда и т.д, Затем второй тактовыйимпульс через элемент задержки 13поступает на вторые входы элементовИ 31-3нечетных разрядов, производит сдвиг в регистрах 11 -1., нечетных разрядов и запись нечетных разря;.,дов второго числа в эти регистры,а также обеспечивает их поступлениечерез элементы ИЛИ 7, -7 нечетныхразрядов на счетные входы триггеров91-9 1 нечетных разрядов и сложениес нечетными разрядами числа, записанного в триггерах 91-9 (по аналогиисо сложением четных разрядов), Например, пусть в триггерах 91-9 1 записаночисло 0111, а поступает число 0011.Тогда после первого сложения (четныхразрядов) в триггерах 9,-9 записывается число 1001, а после второгосложения (нечетных разрядов) - сумма 1010. Этот же второй тактовыйимпульс через элемент задержки 21 поступает на вход синхронизации блокаделения 17, разрешая вычисление мате-.матического ожидания,При поступлении тактовых импульсов с третьего по ю -й устройство работает аналогично. После и -го тактового импульса в триггерах 91-9записывается сумма и, чисел, в регист.рах 1,-1 - вся последовательность поступивших чисел, причем в К-х .разрядах регистров 1,-1 , где К= =1,2, , щ, записывается (гп-К+1)-е число поступившей последовательности чисел, а в счетчике 18 значений Ф , следовательно, появляется высокий потенциал на выходе дешифратора 19 числа щ, и элемент запрета 20 закры вается. Таким образом, все последующие тактовые импульсы на счетный вход счетчика 18 не поступают, а на входах делителя блока деления 17 находится постоянное число в . Если первое чис ло из последовательности нуль, то на инверсных выходах всех регистров единицы, элемент И 4 открыт и (в+1)-й такт работы устройства аналогичен предыдущим тактам. Если же первое 20 число не нуль, то элемент И 4 закрывается и открывается элемент запрета 6, (й+1)-й тактовый импульс через элемент запрета 6, элемент ИЛИ 7, поступает на счетный вход триггера 25 9 , т.е. к младшему разряду суммы, находящейся в триггерах 9, -9, прибавляется единица. Этот же импульс через элемент задержки 11 поступает на вторые входы элементов И 2-"230 ,четных разрядов и обеспечивает поступление четных разрядов первого числа в обратном коде через элементы ИЛИ 7 -7 на счетные выходы триггеров 9 -9 и их сложение с суммой, находящейся в триггерах 9-9, Далееэтот же импульс через элемент задержки 10 поступает на вторые входы эле-.ментов И 2-2.,нечетных разрядови обеспечивает поступление нечетныхразрядов первого числа в обратномкоде через элементы ИЛИ 7 -7., насчетные входы триггеров 9,-9 1 нечетных разрядов и их сложение с суммой,находящейся в триггерах 9-9. Лалееэтот.же сигнал через элемент задержки12, элемент ИЛИ 8 поступает на вторыевходы элементов И Здчетных разрядов и т.д, как описано, т.е. производится запись следующего (щ+1)-гочисла в регистры 1,-1, сложение егос суммой,.находящейся в триггерах9-9 и вычисление математическогоожидания в блоке деления 17.Таким образом, при поступлении(в+ )-го тактового импульса из суммы а чисел вычитается 1 -е из поступающих чисел (путем сложения суммы Вчисел с числом, дополнительным, к1-му) и прибавляется вновь поступившее (ш+)-е число, далее определяется математическое ожидание путемделения полученной в триггерах 9-9 псуммы на число в, поступающее сосчетчика 18, в блоке деления 17. Сле-довательно, в триггерах 9-9 всегданаходится сумма т последних чисели поступающей последовательности, ана выходах устройства 22 - математическое ожидание этих чисел,1211757 Составитель И. МухРедактор Т. Парфенова Техред Л.Микещ Корре Бутяг Подписное ка 4 илиал ППП "Патент город, ул. Проектна 41 /54 ВНИИПИ Госуда по делам из 113035, Москва, Тираж 673твенного комитета СС ретений и открытий -35, Раушская наб.,

СмотретьЗаявка

3771723, 17.07.1984

ВОЙСКОВАЯ ЧАСТЬ 25840

ЕРОШКО ГЕННАДИЙ АНТОНОВИЧ, ШУБИНА НАТАЛЬЯ НИКОЛАЕВНА

МПК / Метки

МПК: G06F 17/18, G06F 7/50

Метки: последовательно, поступающих, разрядных, суммирования, чисел

Опубликовано: 15.02.1986

Код ссылки

<a href="https://patents.su/4-1211757-ustrojjstvo-dlya-summirovaniya-razryadnykh-posledovatelno-postupayushhikh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования -разрядных последовательно поступающих чисел</a>

Предыдущий патент: Функциональный преобразователь

Следующий патент: Устройство для определения параметра степенной модели среднего значения случайного сигнала

Случайный патент: Инструмент для горячей прошивки