Устройство для умножения двоичных чисел в дополнительном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

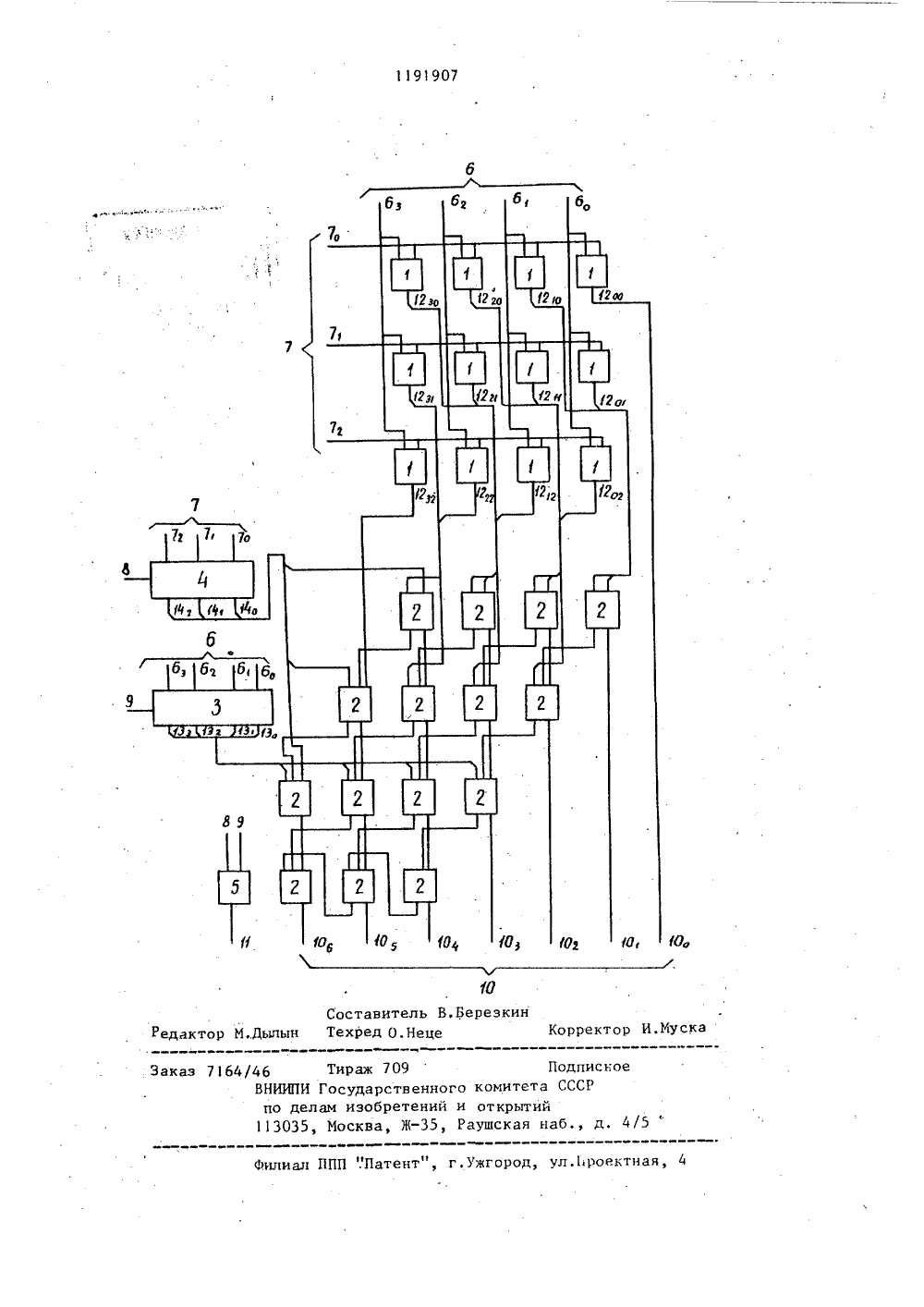

,.13НЙАИО 1 Е 1 А К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) Рабинер Л Гоулд Б. Теория и применение цифровой обработки сигналов. - М.: Мир, 1978, с. 577.Авторское свидетельство СССР В 1037247, кл. С 06 Р 7/52 э,982(54)(57) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯДВОИЧНЬИ ЧИСЕЛ В ДОПОЛНИТЕЛЬНОМКОДЕ, содержащее матрицу элементовИ, матрицу одноразрядных сумматорови сумматор по модулю два, входыкоторого соединены с входами знаковых разрядов первого и второго операндов устройства, а выход подключен к выходу знакового разряда устройства, первые входы элементов Их-го столбца матрицы подключены квходу -го информационного разрядапервого операнда устройства (=1,и;и - количество информационных разрядов первого операнда ), вторые входы элементов И )-й строки матрицыподключены к входу )-го информационного разряда второго операнда устройства (Д=1т; т - количествоинформационных разрядов второго операнда ), выход первого элемента И первой строки матрицы подключен к выхо-.ду первого информационного разрядаустройства, выход суммы каждого одноразрядного сумматора К-го столбцаматрицы подключен к входу следующегоодноразрядного сумматора того же столбца матрицы (К=и + ш - 1), выход суммы последнего одноразрядного сумматора К-го столбца матрицы соединен с выходом (К+)-го информационного разряда устройства, выход переноса каждого одноразрядного сумматора 1-го столбца матрицы подключен к входу одноразрядного сумматора (+1)-го столбца матрицы (1.=1. и+ш), выходы элементоэ И Я -й диагонали матрицы подключены к входам одноразрядных сумматоров Б)-го столбца матрицы (8=2и+ +ш), о т л и ч а ю щ е е с я тем, что, с целью расширения области при менения за счет возможности произ- ф вольного выбора количества разрядов операндов, устройство содержит первый и второй преобразователи пря- С мого кода. в дополнительный, информационные входы которых подключены к Е входам информационных разрядов со- ы ответственно первого и второго операндов устройства, а входы управления включением, соединены- с входаФаай ми знаковых разрядов соответственно второго и первого операндов устройства, выходы первого преобразователя прямого кода в дополнительный 3 с первого по и-й соединены с входами одноразрядных сумматоров столбцов с и-го по (и+ш)-й матрицы соответственно, выходы второго преобразователя прямого кода в дополнительный с первого по ш-й соединены с вхо-. дами одноразрядных сумматоров столбф, цов с и-го по (и+ш)-й матрицы соответственно.Изобретение относится к цифровой электронной вычислительной технике и может быть использовано для построения матричных умножителей в процессорах электронных вычислительных ма шин.Цель изобретения - расширение области применения за счет возможности произвольного выбора количества разрядов операндов.10На чертеже показана функциональная схема устройства для случая п=4, в=3.Устройство содержит матрицу элементов И 1, матрицу одноразрядных 15 сумматоров 2, преобразователи 3 и 4 прямого кода в дополнительный, сумматор 5 по модулю два, входы Ь инфор, мационных разрядов первого операнда, входы 7 информационных разрядоввторо го операнда, вход 8 знакового разряда первого операнда, вход 9 знакового разряда второго операнда, выходы 10 информационных разрядов, выход 11 знакового разряда. Элементы И 1 матри цы и преобразователи 3 и 4 своими выходами соответственно 12, 13 и 14 подключены в соответствии со значениями своих весов с входами одноразрядных су маторов 2 матрицы. Входы эле- З 0 ментов И 1 матрицы соединены с входами Ь и 7. Входы сумматора 5 по мо; дулю два подключены к входам 8 и 9. Информационные входы преобразователей 3 и 4 соединены соответственно с входами Ь и 7, а входы управления включением - с входами 9 и 8. Выходы суммы последних в каждом столбце сумматоров 2 матрицы соединены с выходами 1 О. Выход 40 сумматора 5 по модулю два подключен к выходу 11.Устройство работает следующим образом.В прямом коде при выполнении опе рации умножения осуществляется умножение модулей по формуле)Е) = х 1 1 у 1. (1)Знак результата умножения определяется иэ выражениязхп Е = здп х Щ здп у, (2) Представление в дополнительном коде (и)-разрядного двоичного числа можно описать выражениемМв и ьох=-2 х+ 2. х=-2 х 2 хг к(ь)аО где х - разряды дополнительного кода, которые могут приниматьзначения 10, 1 ;х - знаковый разряд дополнительпного кода, который может принимать значение 0, 1); (и) - разрядность мантиссы числа х,Аналогичным образом может быть записан второй сомножитель:Произведение двух чисел х и у записывается в следующем виде:р ир иЪ рв х=2 ячх . 2-,2 .2 к+ ио 1 рви рь. с. 2 2 Т,. Ф 1:О вгО Учитывая (2 ) выражение (4 ), описывающее так называемый алгоритм Бута, может быть представлено в видеРЬ ифР иЪ рх= 2 (х 0+ ), -2 х 2 з -2":оР в=ОР 1щ 2 х ХХ 2 х хщ) . мсрО тт:ОЧетвертый член выражения (5 ) всегда положителен, что указывает на то, что числа х и у, представленные в дополнительном коде, перемножаются по описанию этой частью выражения так же, как это делается в прямом коде.11 ри этом корректирующие коды, выраженные вторым и третьим членами (5 ), могут присутствовать или отсутствовать в нем в зависимости от наличия или отсутствия знака (-1 у первого или второго сомножителя.Преобразователь 3 (4 )может быть построен в виде совокупности последовательно соединенных разрядных яче" ек,каждая из которых описывается следующей системой логических уравнений;где А - сигнал на входе управлениявключением;В - сигнал на соответствующеминформационном входе преобразователя;С - сигнал на входе переноса;1191907 зО - сигнал на соответствующемвыходе преобразователя;Е - сигнал на выходе переноса1при этом в первой разрядной ячейкев качестве сигнала С используетсясигнал А. данная система уравнений может быть упрощена и соответственно упрощена конструкция преобразователя 3 (4); 10 Суюдость его работы заключается в том, что приналичии сигнала "О" на входе управления включением, соединенном с входом 9 (8), на выходы 13 (14 ) информация не поступает (на этих выходах сформировано значение "О"), а при наличии на этом входе сигнала "1" преобразователь осуществляет лре- образование поступающего на его информационные входы с входов 5 (7) операнда в дополнительный код, который и поступает с выходов 13 (14) преобразователя 3 (4) на входы соответствующих сумматоров 2 матрицы. 4Срабатывание устройства происходит после подачи на его входы х и у сигналов операндов.С входов 6 и 7 сигналы операндов поступают на элементы И 1 матрицы. На выходах элементов И 1 вырабатываются сигналы произведений ху3 С выходов элементов И 1 матрицы сигналы поступают на входы соответству-. ющих сумматоров 2 матрицы. Одновременно с подачей сигналов на входы элементов И 1 сигналы операндов подаются на информационные входы преобра- . зователей 3 и 4, которые при наличии информации о том, что другой операнд отрицателен (наличие сигнала 1" на входах 9 и 8 ), вырабатывают значения: дополнительных кодов операндов, поступающие на входы соответствующих сумматоров 2 матрицы.Процесс установленияв матрицесум-. маторов 2 начинается справого верхнего угла и распространяется вниз ивлево, Процесс заканчиваетсяустановлением значения старшего разряда нижней строкис1191907 Составитель В,Береэкинедактор МДыпын Техред О,Неце Корр И,Муска аж 709 к н и Патент", г.ужго Филиал оектная 7164/46ВНИИПИ Гпо делам113035,сударств изобрет осква, Ж Подписноео комитета СССРи открытииРаушская наб., д. 4

СмотретьЗаявка

3594250, 20.05.1983

ПРЕДПРИЯТИЕ ПЯ Г-4097

ДМИТРИЕВ АНАТОЛИЙ АЛЕКСАНДРОВИЧ, ГРУЗНЫХ АНАТОЛИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: двоичных, дополнительном, коде, умножения, чисел

Опубликовано: 15.11.1985

Код ссылки

<a href="https://patents.su/4-1191907-ustrojjstvo-dlya-umnozheniya-dvoichnykh-chisel-v-dopolnitelnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двоичных чисел в дополнительном коде</a>

Предыдущий патент: Сумматор по модулю два

Следующий патент: Устройство для вычисления квадратного корня

Случайный патент: Распределитель-питатель для пневматической подачи табака к сигаретным и т. п. машинам