Устройство для вычисления быстрого преобразования фурье с основанием 4

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

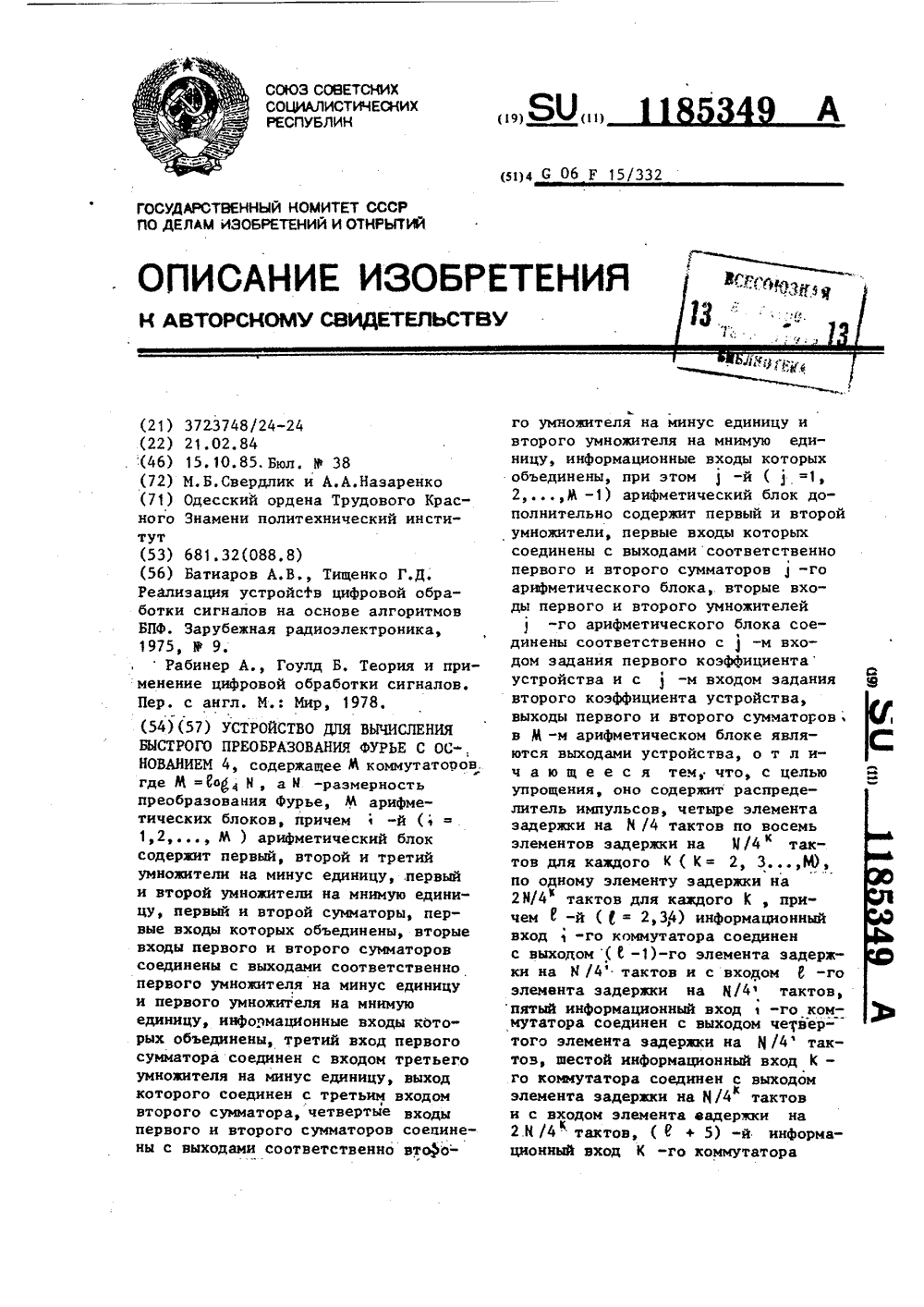

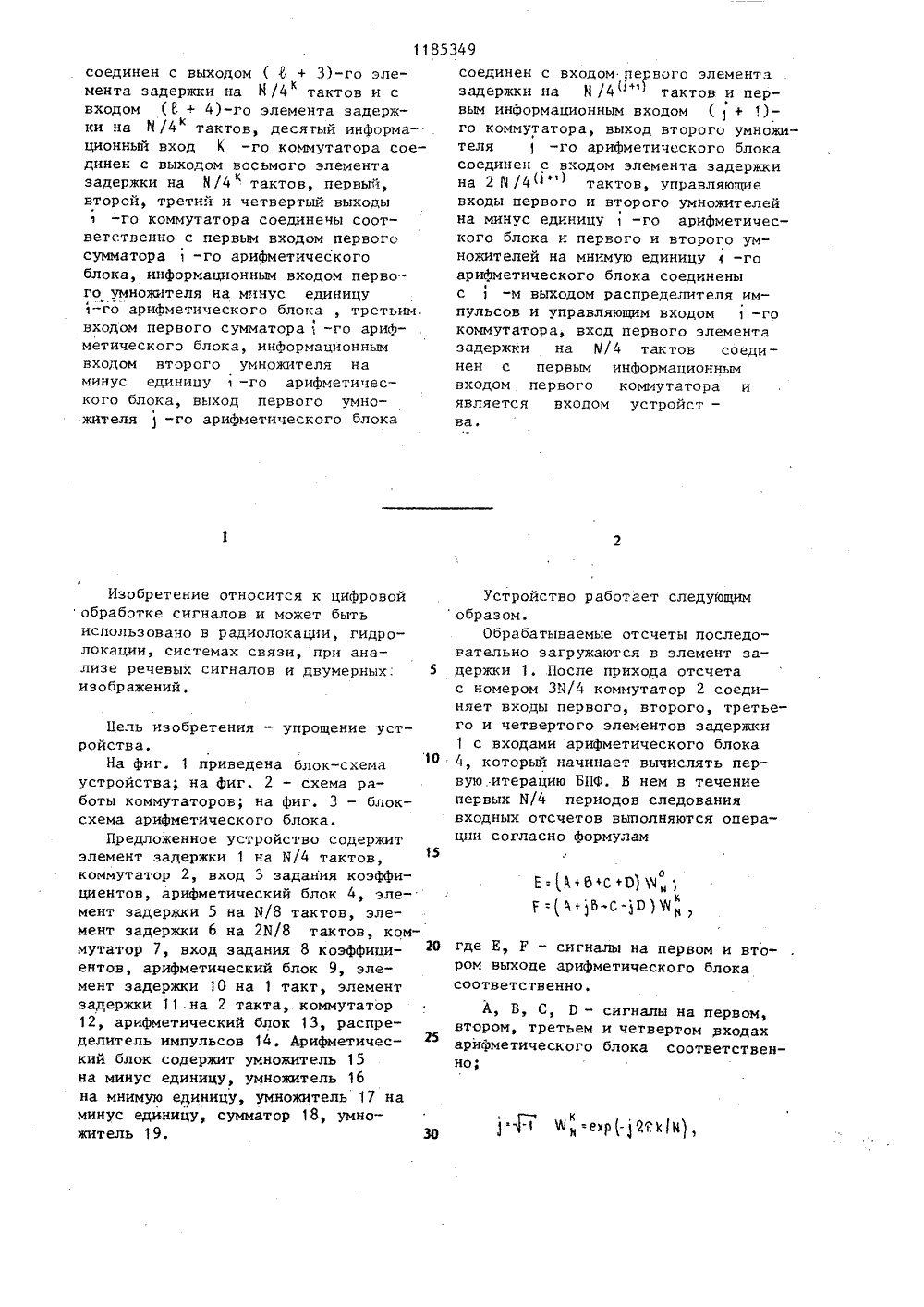

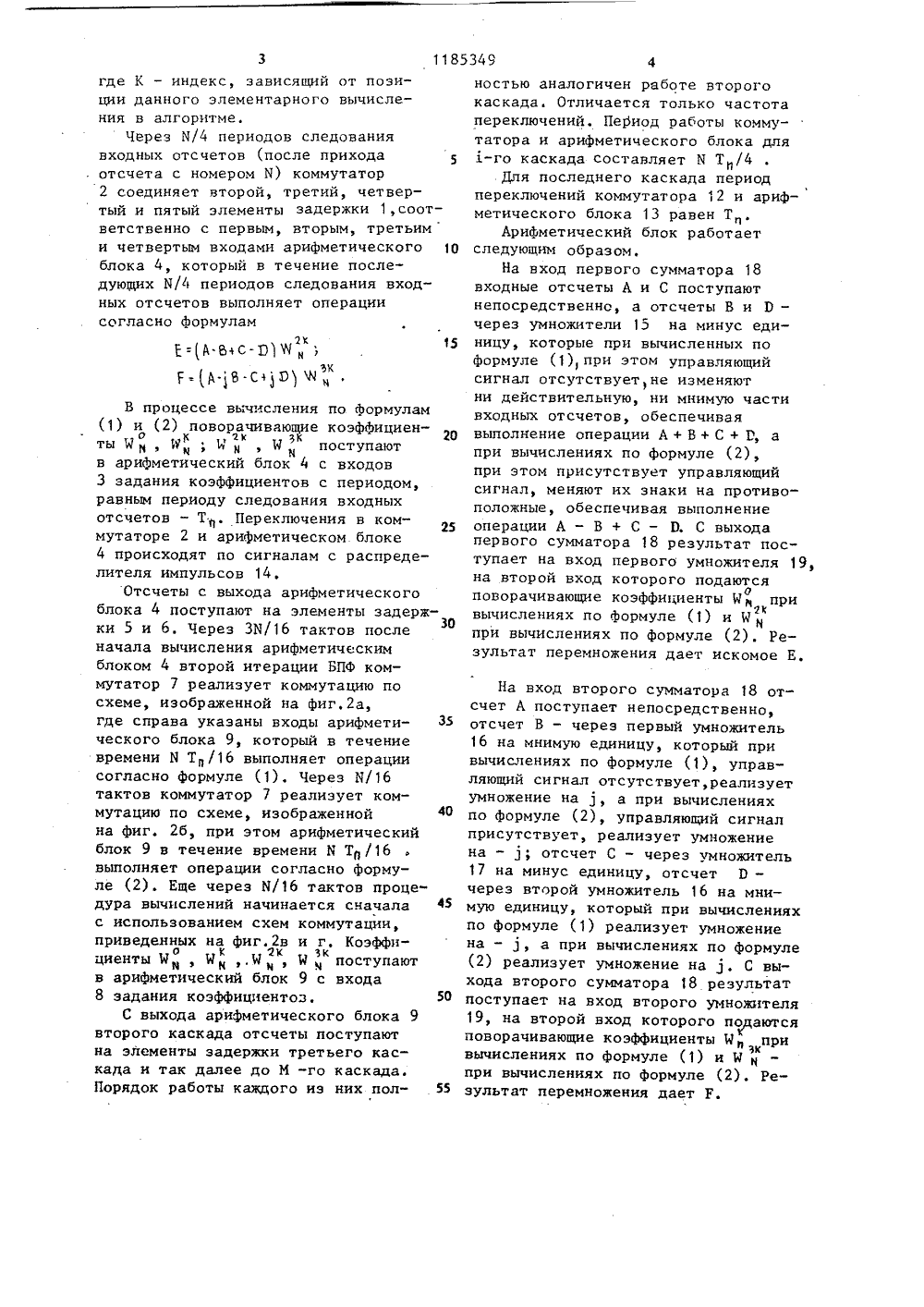

)4 С 06 Г 15/332 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(71) Одесский ордена Трудового Красного Знамени политехнический институт(56) Батиаров А.В Тищенко Г,Д,Реализация устройсФв цифровой обработки сигналов на основе алгоритмовБПф. Зарубежная радиоэлектроника,1975, У 9.Рабинер А., Гоулд Б. Теория и применение цифровой обработки сигналов.Пер, с англ, М,: Мир, 1978,(54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯБЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ С ОСНОВАНИЕМ 4, содержащее М коммутаторовгде М = ОЙ М, а И -размерностьпреобразования фурье, М арифметических блоков, причем 1 -й (1,2 М ) арифметический блоксодержит первый, второй и третийумножители на минус единицу, .первыйи второй умножители на мнимую единицу, первый и второй сумматоры, первые входы которых объединены, вторыевходы первого и второго сумматоровсоединены с выходами соответственнопервого умножителя на минус единицуи первого умножителя на мнимуюединицу, инфо.)мационные входы которых объединены, третий вход первогосумматора соединен с входом третьегоумножителя на минус единицу, выходкоторого соединен с третьим входомвторого сумматора, четвертые входыпервого и второго сумматоров соепинены с выходами соответственно втофого умножнтеля на минус единицу и второго умножителя на мнимую единицу, информационные входы которых объединены, при этом 1 -й ( 1 =1, 2 В -1) арифметический блок дополнительно содержит первый и второй умножители, первые входы которых соединены с выходами соответственно первого и второго сумматоров-го арифметического блока, вторые входы первого и второго умножителей-го арифметического блока соединены соответственно с-м входом задания первого коэффициента устройства и с-м входом задания второго коэффициента устройства, выходы первого и второго сумматоровв М -м арифметическом блоке являются выходами устройства, о т л ич а ю щ е е с я тем; что, с целью упрощения, оно содержит распределитель импульсов, четыре элемента задержки на И /4 тактов по восемь элементов задержки на М /4 такк тов для каждого К ( К = 2, З,М), по одному элементу задержки на 2 М/4" тактов для каждого К , причем Р -й (= 2,34) информационный вход 1 -го коммутатора соединен с выходом ( , -1)-го элемента задержки на М /4 тактов и с входом 6 -го элемента задержки на К/4 тактов, пятый информационный вход 1 -го коммутатора соединен с выходом четвертого элемента задержки на Ц/4 тактов, шестой информационный вход К - го коммутатора соединен с выходом элемента задержки на й/4 тактовки с входом элемента вадержки на 2 К /4тактов, (+ 5) -й информационный вход К -го коммутатора1185349 Е = А+ 6+С+о) ЧЧ;Е =(.Ь-С-;О) а",соединен с выходом ( 8 + 3)-го элемента задержки на М/4 тактов и сКвходом (В + 4)-го элемента задержки на М /4 тактов, десятый информакционный вход 1 -го коммутатора соединен с выходом восьмого элемента задержки на 1 /4 " тактов, первый, второй, третий и четвертый выходы-го коммутатора соединечы соответственно с первым входом первого сумматора 1 "го арифметического блока, информационным входом первого умножителя на минус единицуА1-го арифметического блока , третьим.1 входом первого сумматора-го арифметического блока, информационным входом второго умножителя на минус единицу 1 -го арифметического блока, выход первого умно- жителя 1 -го арифметического блока Изобретение относится к цифровойобработке сигналов и может быть использовано в радиолокации, гидро- локации, системах связи, при анализе речевых сигналов и двумерных: изображений,Цель изобретения - упрощение устройства.На Фиг. 1 приведена блок-схема1 Оустройства; на фиг, 2 - схема работы коммутаторов; на фиг. 3 - блоксхема арифметического блока,Предложенное устройство содержитэлемент задержки 1 на И/4 тактов,коммутатор 2, вход 3 задания коэффициентов, арифметический блок 4, элемент задержки 5 на И/8 тактов, элемент задержки 6 на 2 И/8 тактов, коммутатор 7, вход задания 8 коэффициентов, арифметический блок 9, элемент задержки 10 на 1 такт, элементзадержки 11 на 2 такта,. коммутатор12, арифметический блок 13, распределитель импульсов 14. Арифметический блок содержит умножитель 15на минус единицу, умножитель 16на мнимую единицу, умножитель 17 наминус единицу, сумматор 18, умножитель 19. 30 соединен с входом первого элемента задержки на И /4" тактов и первым информационным входом ( 1 + 1)- го коммутатора, выход второго умножителя 1 -го арифметического блока соединен с входом элемента задержки на 2 5 /4( "1 тактов, управляющие входы первого и второго умножителей на минус единицу-го арифметического блока и первого и второго умножителей на мнимую единицу 1 -го арифметического блока соединены1с 1 -м выходом распределителя импульсов и управляющим входом 1 -го коммутатора, вход первого элемента задержки на Ю/4 тактов соединен с первым информационным входом первого коммутатора и является входом устройст - ва. Устройство работает следующимобразом.Обрабатываемые отсчеты последовательно загружаются в элемент задержки 1 После прихода отсчета с номером ЗИ/4 коммутатор 2 соединяет входы первого, второго, третьего и четвертого элементов задержки 1 с входами арифметического блока 4, который начинает вычислять первую итерацию БПФ. В нем в течение первых И/4 периодов следования входных отсчетов выполняются операции согласно Формулам где Е, Р - сигналы на первом и втором выходе арифметического блокасоответственно. А, В, С, В - сигналы на первом, втором, третьем и четвертом дходах арифметического блока соответственно;где К - индекс, зависящий от позиции данного элементарного вычисления в алгоритме.Через И/4 периодов следования входных отсчетов (после прихода5 отсчета с номером И) коммутатор 2 соединяет второй, третий, четвертый и пятый элементы задержки 1,соответственно с первым, вторым, третьим и четвертым входами арифметического 1 О блока 4, который в течение последующих И/4 периодов следования входных отсчетов выполняет операции согласно Формуламк 15=1.ас% ;ькГ=А-в-с о) а,В процессе вычисления по Формулам(1) и (2) поворачивающие коэффициено к 12 к зкты Ч , Ю,; ь и, У поступаютв арифметический блок 4 с входов3 задания коэффициентов с периодом,равным периоду следования входныхотсчетов - Т. Переключения в коммутаторе 2 и арифметическом блоке4 происходят по сигналам с распределителя импульсов 14.Отсчеты с выхода арифметическогоблока 4 поступают на элементы задержки 5 и 6, Через ЗИ/16 тактов после30начала вычисления арифметическимблоком 4 второй итерации БПФ коммутатор 7 реализует коммутацию посхеме, изображенной на фиг,2 а,где справа указаны входы арифмети- З 5ческого блока 9, который в течениевремени Н Т /16 выполняет операциисогласно формуле (1). Через Б/16тактов коммутатор 7 реализует коммутацию по схеме, изображеннойна фиг. 2 б, при этом арифметическийблок 9 в течение времени М Т 0 /16выполняет операции согласно формуле (2), Еще через И/16 тактов процедура вычислений начинается сначала 45с использованием схем коммутации,приведенных на фиг.2 в и г. Коэффио к як зкциенты М И,.М, И,поступаютв арифметический блок 9 с входа8 задания коэффициентоз, 50С выхода арифметического блока 9второго каскада отсчеты поступаютна элементы задержки третьего каскада и так далее до М -го каскада.Порядок работы каждого из них пол ностью аналогичен работе второгокаскада. Отличается только частотапереключений. Период работы коммутатора и арифметического блока для1-го каскада составляет И Т/4Для последнего каскада периодпереключений коммутатора 12 и арифметического блока 13 равен Т.Арифметический блок работаетследующим образом,На вход первого сумматора 18входные отсчеты А и С поступаютнепосредственно, а отсчеты В и Р -через умножители 15 на минус единицу, которые при вычисленных поформуле (1),при этом управляющийсигнал отсутствуетне изменяютни действительную, ни мнимую частивходных отсчетов, обеспечиваявыполнение операции А + В + С + Г, апри вычислениях по Формуле (2),при этом присутствует управляющийсигнал, меняют их знаки на противоположные, обеспечивая выполнениеоперации А - В + С - Р. С выходапервого сумматора 18 результат поступает на вход первого умножителя 19,на второй вход которого подаютсяоповорачивающие коэффициенты И при21вычислениях по формуле (1) и Упри вычислениях по формуле (2). Результат перемножения дает искомое Е. На вход второго сумматора 18 отсчет А поступает непосредственно, отсчет В - через первый умножитель 16 на мнимую единицу, который при вычислениях по формуле (1), управляющий сигнал отсутствует, реализует умножение на 1, а при вычислениях по Формуле (2), управляюп;ий сигнал присутствует, реализует умножение на - 1; отсчет С - через умножитель 17 на минус единицу, отсчет Р - через второй умножитель 16 на мнимую единицу, который при вычислениях по формуле (1) реализует умножение на - 1, а при вычислениях по формуле (2) реализует умножение на 3. С выхода второго сумматора 18 результат поступает на вход второго умножителя 19, на второй вход которого подаются поворачивающие коэффициенты Чц при вычислениях по формуле (1) и Ипри вычислениях по формуле (2). Результат перемножения дает Р.

СмотретьЗаявка

3723748, 21.02.1984

ОДЕССКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

СВЕРДЛИК МЕШУЛИМ БЕНИЯМИНОВИЧ, НАЗАРЕНКО АНАТОЛИЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, вычисления, основанием, преобразования, фурье

Опубликовано: 15.10.1985

Код ссылки

<a href="https://patents.su/4-1185349-ustrojjstvo-dlya-vychisleniya-bystrogo-preobrazovaniya-fure-s-osnovaniem-4.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления быстрого преобразования фурье с основанием 4</a>

Предыдущий патент: Устройство для моделирования систем связи

Следующий патент: Устройство для обработки изображений

Случайный патент: Устройство для измерения электрической проводимости жидкости