Устройство для вычисления функции = +

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

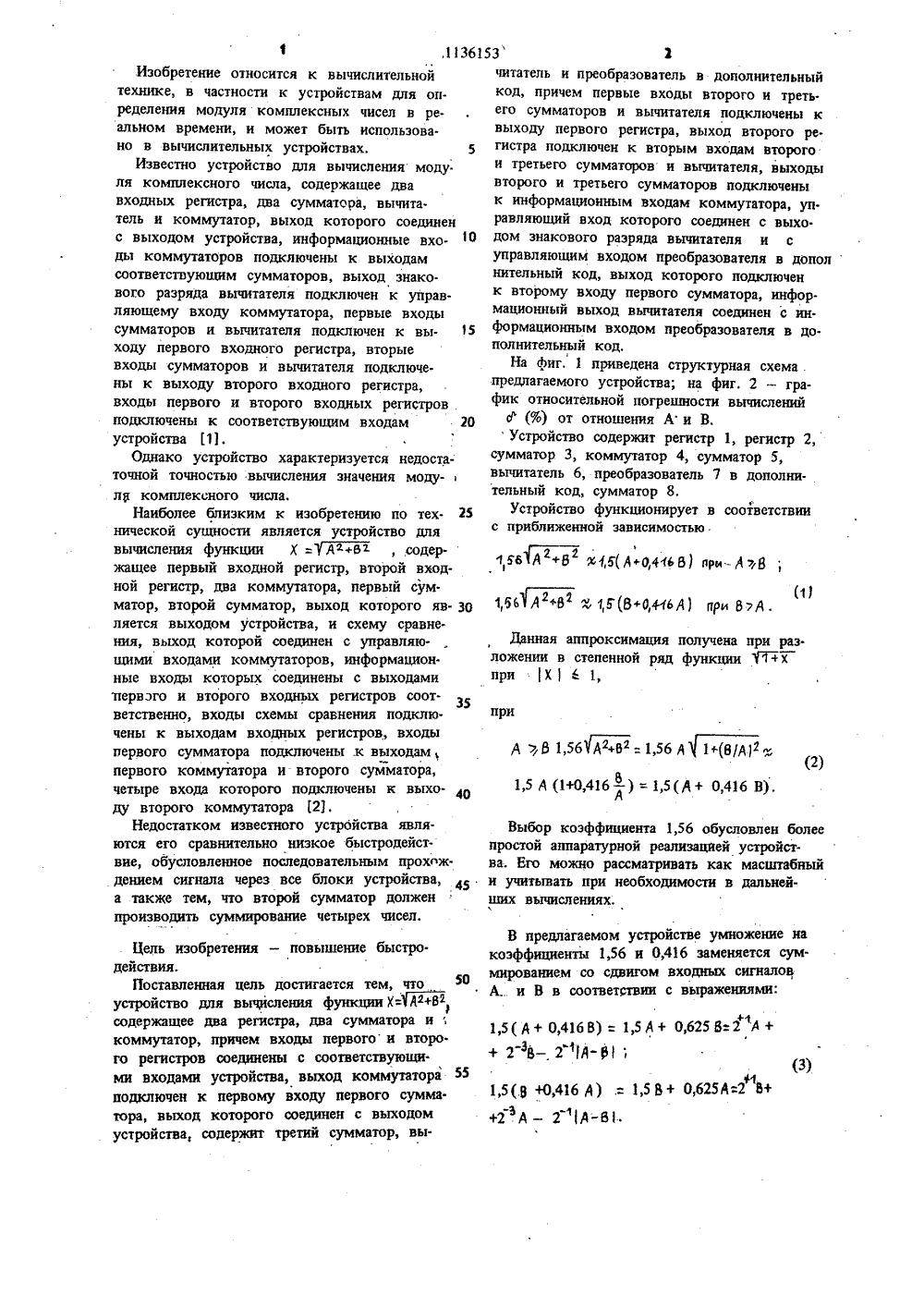

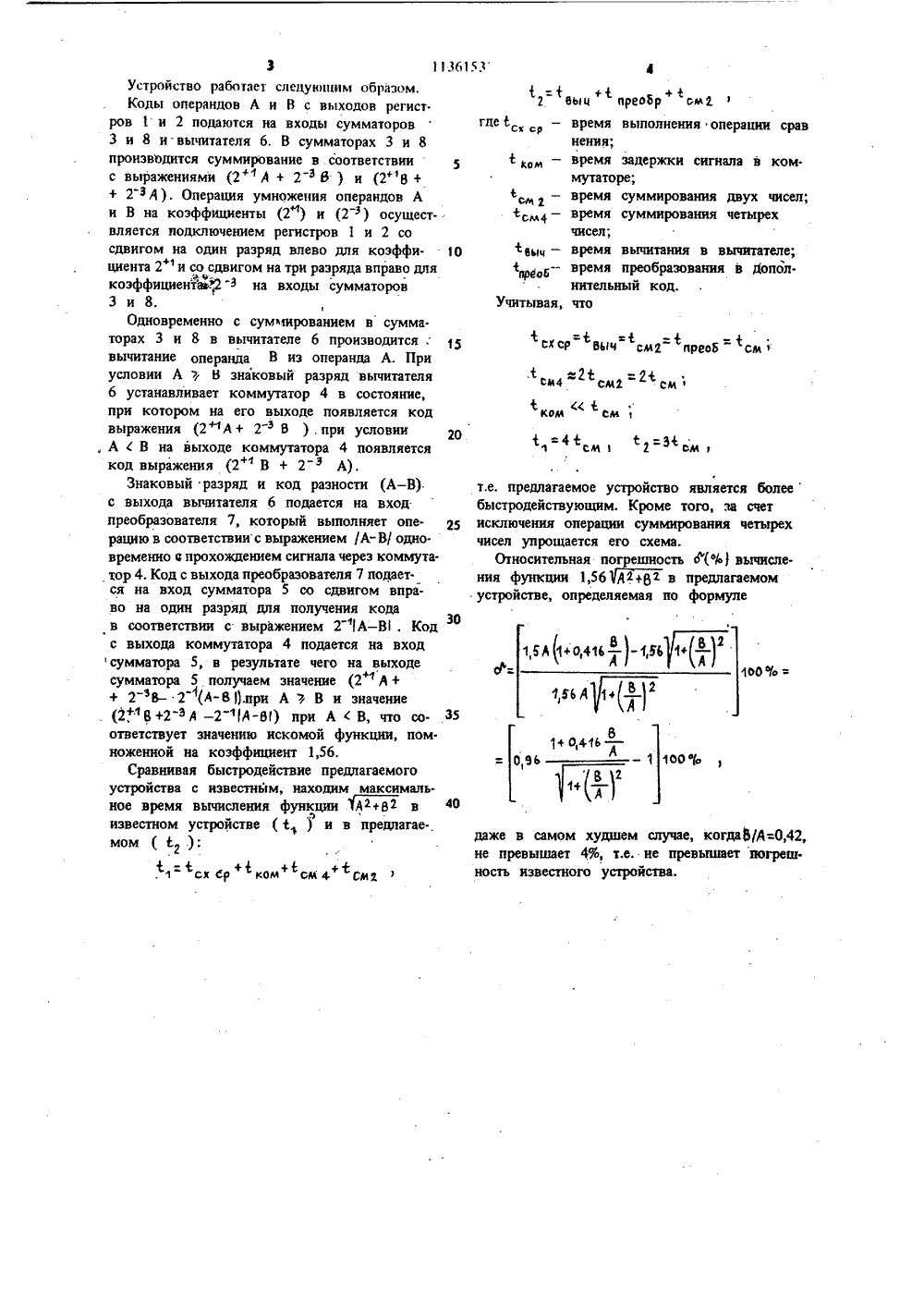

СОЮЗ СОВЕТСНИХСОЦИАЛИСТ ИЧЕСНИХРЕСПУБЛИН 1) 6 06 Р 7/544 ПИСАНИЕ ИЗОБРЕТЕ ВИДЕТЕЛЬС АВТОРСНО ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(56) 1. Авторское свидетельство СССР КФ 1001085, кл. 6 06 Р 7/38, 1981.2. Авторское свидетельство СССР Р 964634, кл. 6 06 Р 7/552, 1981 (прототип).(54) (57) УСТРОЙСТВО ЛЛЯ ВЬИИСЛЕНИЯФУНКЦИИ УФ 1 Йаеаа, ееаержаеаее ееерегистра, два сумматора и коммутатор, при.чем входы первого н второго регистров соединены с соответствующими входами устройства, выход коммутатора подключен к первому входу первого сумматора, выход которого соединен с выходом устройства, о тличаюшееся тем,что,сцелью 801136153 повышения быстродействия, оно содержиттретий сумматор, вычитатель и преобразователь в дополнительный код, причем первыевходы второго. и третьего сумматоров и вычитателя подключены к выходу первого регистра, выход второго регистра подключенк вторым входам второго и третьего сумматоров и вычитателя, выходы второго итретьего сумматоров подключены к информационным входам коммутатора, управляющий вход которого соединен с выходомзнакового разряда вычитателя и с управля.ющим входом преобразователя в дополнительный код, выход которого подключен к второму входу первого сумматора, информационный выход вычитателя соединен с информационным входом преобразователя в дополнительный код.,11361Изобретение относится к вычислительнойтехнике, в частности к устройствам для определения модуля комплексных чисел в реальном времени, и может быть испольэовано в вычислительных устройствах. 5Известно устройство для вычисления модуля комплексного числа, содержащее двавходных регистра, два сумматора, вычита.тель и коммутатор, выход которого соединенс выходом устройства, информационные входы коммутаторов подключены к выходамсоответствующим сумматоров, выход знакового разряда вычитателя подключен к управляющему входу коммутатора, первые входысумматоров и вычитателя подключен к выходу первого входного регистра, вторыевходы сумматоров и вычитателя подключены к выходу второго входного регистра,входы первого и второго входных регистровподключены к соответствующим входам 20устройства 1.Однако устройство характеризуется недостаточной точностью вычисления значения модуля комплексного числа,Наиболее близким к изобретению по технической сущности является устройство длявычисления функции // иГяеее, севержащее первый входной регистр, второй входной регистр, два коммутатора, первый сумматор, второй сумматор, выход которого яв. 30ляется выходом устройства, и схему сравнения, выход которой соединен с управляющими входами коммутаторов, информацион.ные входы которых соединены с выходамипервэго и второго входных регистров соответственно, входы схемы сравнения подклю.чены к выходам входных регистроввходыпервого сумматора подключены,к выходампервого коммутатора и второго сумматора,четыре входа которого подключены к выходу второго коммутатора 21Недостатком известного устройства являются его сравнительно низкое быстродействие, обусловленное последовательным прохож.дением сигнала через все блоки устройства,а также тем, что второй сумматор долженпроизводить суммирование четырех чисел. 53 1читатель и преобразователь в дополнительныйкод, причем первые входы второго и треть.его сумматоров и вычитателя подключены квыходу первого регистра, выход второго ре.гистра подключен к вторым входам второгои третьего сумматоров и вычитателя, выходывторого и третьего сумматоров подключенык информационным входам коммутатора, уп.равляющий вход которого соединен с выхо.дом знакового разряда вычитателя и суправляющим входом преобразователя в дополнительный код, выход которого подключенк второму входу первого сумматора, информационный выход вычитателя соединен с ин.формационным входом преобразователя в до.полнительный код,На фиг, 1 приведена структурная схема.предлагаемого устройства; на фиг, 2 - график относительной погрешности вычисленийд" (%) от отношения А и В.Устройство содержит регистр 1, регистр 2,сумматор 3, коммутатор 4, сумматор 5,вычитатель 6, преобразователь 7 в дополнительный код, сумматор 8,Устройство функционирует в соответствиис приближенной зависимостью15 ЕГА В К/5(6 ОЕЧ 6 В) енн-МВВ1 /1,56 Я +8 Ф 1,58+0,И 6 Я) при 8)Я.Данная аппроксимация получена при разложении в степенной ряд функции +х при Х - ).,при(2)1,5 А (1+0,416 - ) =115(А+ 0,416 В).Выбор коэффициента 1,56 обусловлен более простой апнаратурной реализацией устройства, Его можно рассматривать как масштабный и учитывать при необходимости в дальнейших вычислениях.чЦепь изобретения - повышение быстродействия,Поставленная цель достигается тем, что50 устройство для вычисления функции Х=)ГА+8 содержащее два регистра, два сумматора и: коммутатор, причем входы первого и второ. го регистров соединены с соответствующими входами устройства, выход коммутатора 55 подключен к первому входу первого сумма. тора, выход которого соединен с выходом устройства, содержит третий сумматор, вы ф1,5(А+ 054168) = 155 А+ 016258=2 А+(3) В предлагаемом устройстве умножение на коэффициенты 1,56 и 0,416 заменяется суммирование.м со сдвигом входных сигналов А и В в соответствии с выражениями:=4 см ) 2=5 Ьом 400% ф 1)ЮЬА 1+ -см 4 См 2 3Устройство работает слецук)цим образом.Коды операндов А и В с выходов регист.ров 1 и 2 подаются на входы сумматоров3 и 8 н.вычитателя 6. В сумматорах 3 н 8производится суммирование в соответствиис выражениями (2+"4 + 2 э В ) и (2+8++ 2 ЗА). Операция умножения операндов Аи В на коэффициенты (2 ) и (2 Р) осуществляется подключением регистров 1 и 2 сосдвигом на один разряд влево для коэффи Оциента 2+ и со сдвигом на три разряда вправо длякоэффнциентжфна входы сумматоров3 и 8.Одновременно с сумчированием в сумма.торах 3 и 8 в вычитателе 6 производится .вычитание операнда В из операнда А. Приусловии АВ знаковый разряд вычитателя6 устанавливает коммутатор 4 в состояние,при котором на его выходе появляется кодвыражения (2+)А+ 2 з 6 ) .при условииА С В на выходе коммутатора 4 появляетсякод выражения (2+ В + 2 з А),Знаковый разряд и код разности (А - В).с выхода вычитателя 6 подается на входпреобразователя 7, который выполняет опе- о 5рацию в соответствиис выражением /А-В/ одновременно о прохождением сигнала через коммутатор 4, Код с выхода преобразователя 7 подается на вход сумматора 5 со сдвигом вправо на один разряд для получения кодав соответствии с выражением 2 "1 А - В 1 . Код30с выхода коммутатора 4 подается на входсумматора 5, в результате чего на выходесумматора 5 получаем значение (2 "А+. (2+" В+2 ЭА - 2 ф 14-61) при А ( В, что со- з 5ответствует значению искомой функции, пом.ноженной на коэффициент 1,56.Сравнивая быстродействие предлагаемогоустройства с известным, находим максимальное время вьииевенин функции 62 гна в ео+2 Еыц преовр ом 2 ) время выполнения операции сравпения;время задержки сигнала в ком.мутаторе;время суммирования двух чисел;время суммирования четырехчисел;время вычитания в вычитателе;время преобразования в дополнительный код.что сх ср Вь)ч см 2 лрео 5 = см ) т.е. предлагаемое устройство является более быстродействующим. Кроме того, эа счет исключения операции суммирования четырех чисел упрощается его схема.Относительная погрешность У(цй 1 вычислении Функции 1,5 о)Яаеяа в предлагаемом устройстве, определяемая по формуле 1 оА 1+041 Ь - -1 оЬ 1+ -г АА 1+ 041 Ь -ВА 0,Ь - 1 100 фЬ )1136153 47 И ОУ Заказ 10286/36 Тираж ВНИИПИ Государстве по делам изобре 113035, Москва, Ж, лиап ППП "Патент", г. Ужгород,ектная,Редактор Н. Бобков пгОЕМФиг.8 оставитель В. БерезкинТехред М, Кузьма Корректор М.Демчик 710 Подписноенного комитета СССРний и открытийаушская наб., д, 4)5

СмотретьЗаявка

3603695, 09.06.1983

ПРЕДПРИЯТИЕ ПЯ М-5075

КАСАТКИН НИКОЛАЙ НИКОЛАЕВИЧ, ТАРАСОВ АЛЕКСАНДР СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычисления, функции

Опубликовано: 23.01.1985

Код ссылки

<a href="https://patents.su/4-1136153-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции = +</a>

Предыдущий патент: Число-импульсное множительное устройство

Следующий патент: Функциональный преобразователь

Случайный патент: Монтажный столик