Устройство для исправления одиночных и обнаружения многократных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1115055

Авторы: Звездогляд, Смирнов, Шарыгин

Текст

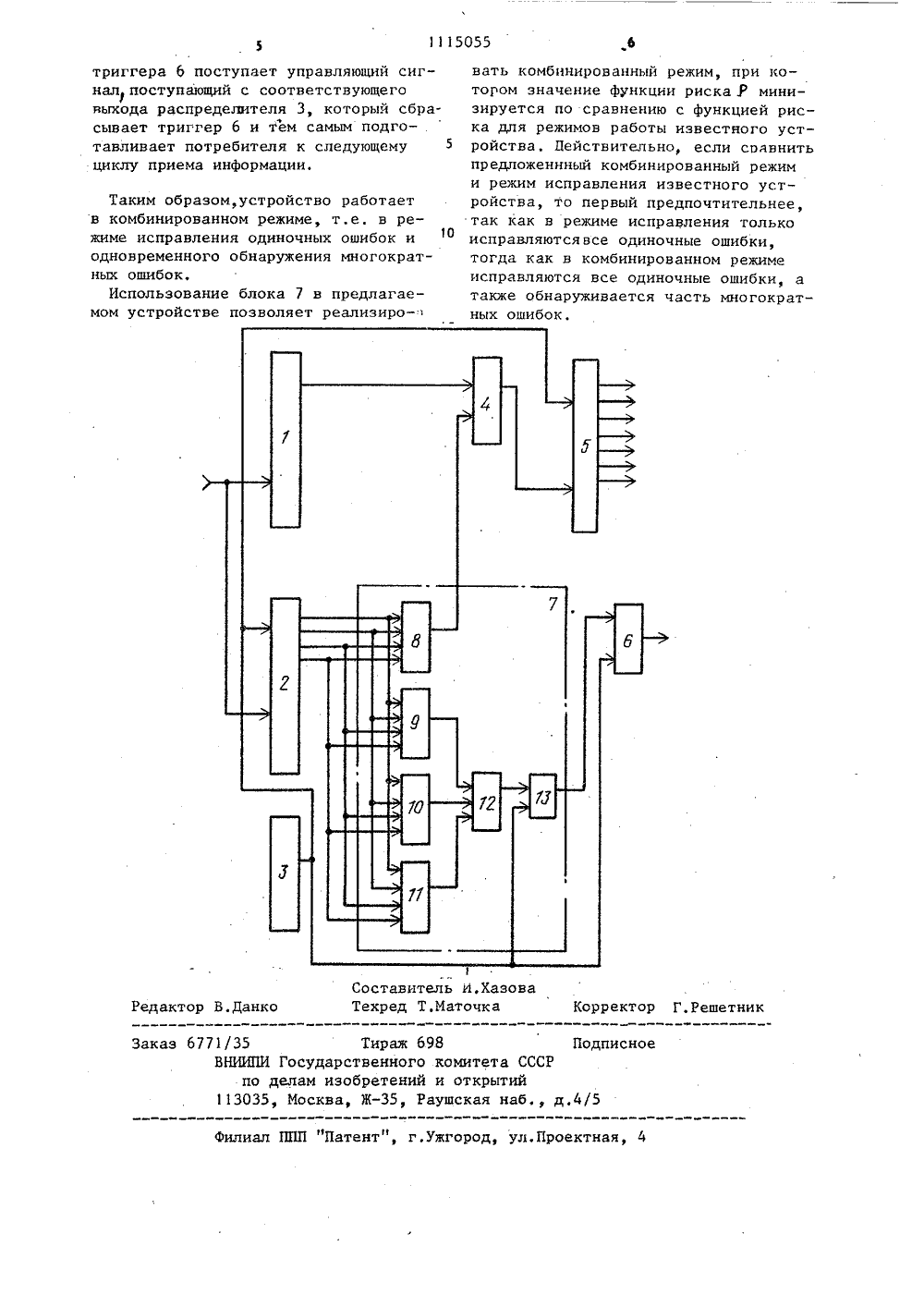

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН За 1 С 06 Г 11/10 ОПИСАНИЕ ИЗОБРЕТЕНИЯ БИБЛИОТЕКА ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 21) 3375342/18-24(56) 1. Авторское свидетельство СССР1 323778, кл. С 06 Р 11/08, 1969.2. Авторское свидетельство СССРВ 196441, кл. С 06 Р 11/08,Н 04 1, 1/10,1966 поототип).(54) (57) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫК И ОБНАРУЖЕНИЯ ГНОГОКРАТНЫХ ОШИБОК, содержащее входной регистр и блок деления, информационные входы которых объединены и образуют информационный вход устройства, сумматор по модулю два, выход которого соединен с информационным входом выходного регистра, выходы которого являются информационными выходами устройства, выход входного регистра соединен с первым входом сумматора по модулю два, распределитель импульсов, выход которого соединен с управляющими входами входного регистра, блока деления, выходного регистра и первымвходом триггера, блок обнаруженияошибок, о т л и ч а ю щ е е с я тем,что, с целью повышения достоверностиконтроля, блок обнаружения ошибоксодержит дешифратор исправляемых ошибок, группу дешифраторов неисправляемых ошибок, элемент КПИ и элемент И,причем выход дешифратора исправляемых ошибок соединен с вторым входомсумматора по модулю два, выходы дешифраторов неисправляемых ошибок группы через элемент ИЛИ соединены с пер- ,вым входом элемента И, второй вход Екоторого соединен с выходом распреде- ррлителя импульсов, а выход - соединен %Ф Фс вторым входом триггера, выход кото- Срого является выходом ошибки устройсва, входы дешифратора исправляемыхошибок и дешифраторов неисправляемых ошибок группы соединены с соответствующими разрядными выходами бло-ка даления.Изобретение относится к автоматике и вычислительной технике и может найти применением в устройствах и системах передачи цифровой информации.Известно устройство для исправле ния одиночных и обнаружения многократных ошибок, содержащее регистры сдвига и сумматоры по модулю два и функционирующее на основе цикличес- КИХ КОДОВ 13 е 10Недостаток устройства состоит в том, что оно может работать либо в режиме исправления ошибок, либо в режиме обнаружения многократных ошибок.Наиболее близким по технической 15 сущности к изобретению является устройство для исправления одиночных и обнаружения многократных ошибок, содержащее регистр-накопитель, регистр- делитель, блок управления, сумматор 20 по модулю два, выходной регистр,триггер и блок обнаружения ошибок, причем вход устройства соединен с информационными входами регистра-накопителя и регистра-делителя, выход регистра накопителя соединен с первым входом сумматора по модулю два, выход которого соединен с информационным входом выходного регистра, выходные разряды регистра-делителя соединены со отвественно с входами контрольного остатка обнаружения ошибок, выходы сигнада исправления одиночной ошибки и сигнала неисправляемой кратной ошибки которого соединены соответственно с входом сумматора по модулю два и первым входом триггера, выход которого является выходом неисправляемой кратной ошибки, устройства, выходы блока управления соединены соответственно с управляющими входами регистра накопителя, регистра-делителя, блока обнаружения ошибок, триггера,и выходного регистра, выходные разряды которого являются информационными выхода 45 ми устройства 21Недостаток известного устройства состоит. в следующем.Корректирующая способность устройст ва для исправления одиночных и обнаружения многократных ошибок может быть оценена функцией риска Р ,кото. рая представляет собой взвешенную сумму вероятности ошибки принятого сообщения Р ы и вероятности пропуска Ряр и выражается зависимостьюР =Ф:Рош+ Рр где сс и Р - весовые коэффициенты, которые определяют относительные потери при декодировании с ошибкой и при пропусхе соотвественно.При использовании известного устройства с циклическим кодом (п,Е), которое может обеспечить исправление одиночных ошибок или обнаружение одиночных и многократных ошибок, возможны два режима работы: режим исправления и режим обнаружения. В первом режиме исправляются все одиночные ошибки, но многократные ошибки приводят к приему кодовой комбинации с ошибкой и к значительному увеличению значения Ров. Во втором режиме устройство обнаруживает одиночные и частично многократные ошибки при значительном увеличении значения Ряр.Таким обра-, зом, в целом в обоих режимах работы известного устройства значение функции риска Р оказывается существенным, что свидетельствует о значительном снижении помехоэащищенности передаваемой информации и не- . высоких функциональных возможностях известного устройства.Цель изобретения - повышение достоверности контроля устройства.Поставленная цель достигается тем, что в предлагаемом устройстве, содержащем входной регистр и блок деления, информационные входы которых объединеф ны и образуют информационный вход устройства, сумматор по модулю два, выход которого соединен с информационным входом выходного регистра, выходы которого являются информационными выходами устройства, выход входного регистра соединен с первым входом сумматора по модулю два, распределитель импульсов, выход которого соединен с управляющими входами входного регистра, блока деления, выходного регистра и первым входом триггера, блок обнаружения ошибок, последний содержит дешифратор исправляемых ошибок, группу дешифраторов неисправляемых ошибок, элемент ИЛИ и элемент И, причем выход дешифратора исправляемых ошибок соединен с вторым входом сумматора ло модулю два, выходы дешнфраторов неисправляемых ошибок группы через элемент ИЛИ соединены с первым входом элемента И, второй вход которого соединен с выходом распределителя импульсов, а вы15055 3ход - с вторым входом триггера, выходкоторого является выходом ошибки устройства, входы дешифратора исправляемых ошибок и дешифраторов неисправляемых ошибок группы соединены с со;ответствующими разрядными выходамиблока деления.На чертеже представлена блок-схема.предлагаемого устройства.Устройство содержит входной регистрО1 , блок.2 деления, распределитель3 импульсов, сумматор 4 по модулюдва, выходной регистр 5, триггер 6,блок 7 обнаружения ошибок, содержащий дешифратор 8 исправляемых ошибок, группу дешифраторов 9-1 неисправляемых ошибок, элементы ИЛИ 12и И 13.Устройство работает следующим образом. 20В основе работы устройства лежитприменение укороченного циклического кода УЦК (12,8), кодовая комбинация которого содержит 12 символов:8 информационных и 4 контрольных, 25поступающих одновременно через информационные входы на регистр 1 и блок 2.Случай приема без ошибок. В регистр1 происходит запись 12-символьнойпоследовательности по сигналам, поступающим на управляющий вход регистра 1 с выхода распределителя 3,Одновременно в блоке 2 происходит деление принимаемой 12-символьной последовательности на образующий поли- З 5ном х + х + 1. Затем после записи12-го символа происходит быстрое счи-тывание из регистравосьми информационных символов, а в блоке 2 - продолжение деления остатка. Оба процес са заканчиваются до прихода первогосимвола следующей кодовой комбинации.Выходной код регистра 1 проходит через сумматор 4 без изменений, таккак сигнал исправляемой ошибки не вы рабатывается дешифратором 8, настроенным на двоичное число 1110 (при нулевом остатке в блоке 2).При этом в регистре 5 записываются по управляющимсигналам с распределителя 3 информационные символы принятой кодовой комбинации. Сигнал ошибки в этом случаетакже не вырабатывается, так как принулевом остатке в блоке 2 не срабатывает ни один из дешифраторов 9-11, 55настроенных на определенные двоичные числа, отличные от Муля и соответствующие многократным ошибкам. В случае, если произошла одиночная ошибка, остаток от деления принятой кодовой комбинации на образующий полином не равен нулю. Тогда в момент быстрого считывания срабатывает дешифратор 8 и на его выходе вырабатывается сигнал, причем по временному положению этот сигнал соответствует месту искаженного символа, При этом 8-разрядный последовательный код с выхода регистра 1 суммируется на сумматоре 4 с сигналом дешифратора, 8 и происходит исправление пораженного символа, а следовательно, принятой кодовой комбинации. Однако сигнал на выходе триггера 6 по-прежнему не вырабатывается так как при делении на образующий полином остатка в момент быстрого считывания последний не принимает значений,.на которые настроены дешифраторы 9-11.В случае двойной ошибки (или ошибки большей степени кратности) возможны два варианта полученных остатков при делении принятой кодовой комбинации на образующий полином, В первом варианте остаток может соответствовать единичной ошибке, тогда в момент быстрого считывания вырабатывается сигнал на выходе дешифратора 8, который суммируется с кодовой комбинацией, и происходит дополнительная ошибка. Устройство в этом случае производит прием с ошибкой. Во втором варианте остаток может соответствовать двойной ошибке, Тогда в момент быстрого считывания срабатывает один из дешифраторов 9-11, так как последние настроены на двоичные числа 001, 1101,1111, соответствующие многократ ным ошибкам. Полученный сигнал, проходя через элемент ИЛИ 12, поступает на двухвходовый элемент И 13, где стробируется сигналами, поступающими с выхода распределителя 3. Стробирование необходимо, так как в блоке 2 деление принимаемой кодовой комбинации на образукщий полином происходит за время всего цикла, и могут произойти ложные срабатывания дешифраторов 9-11. С выхода элемента И 13 таким образом сформированный сигнал поступает на первый вход триггера 6, на котором формируется сигнал неисправляемой кратной ошибки, поступающий к потребителю и сигиалиэирующий о том, что принятый код с выхода регистра 5 искажен, На второй вход1115055 Составитель И,ХазоТехред Т.Маточка Корректор Г.Решетни Редактор В.Даик Под Тираж 698 осударственного комитета СС ам изобретений и открытий Москва, Ж, Раушская наб, аказ 6771/ВНИИПИ по дел1130351 д,4/5 Патент", г.ужгород, ул.Проектная Фил триггера 6 поступает управляющий сигнал поступающий с соответствующеговыхода распределителя 3, которыч сбрасывает триггер 6 и тем самым подготавливает потребителя к следующемуциклу приема информации. Таким образом, устройство работает в комбинированном режиме, т.е. в режиме исправления одиночных ошибок и одновременного обнаружения многократных ошибок.Использование блока 7 в предлагаемом устройстве позволяет реализиро вать комбинированный режим, при котором значение функции риска Р минизируется по сравнению с функцией риска для режимов работы известного уст 5 ройства, Пействительно, если соавнитьпредложеннный комбинированный режими режим исправления известного устройства, то первый предпочтительнее,так как в режиме исправления толькоОисправляютсявсе одиночные ошибки,тогда как в комбинированном режимеисправляются все одиночные ошибки, атакже обнаруживается часть многократных ошибок,

СмотретьЗаявка

3375342, 05.01.1982

ПРЕДПРИЯТИЕ ПЯ В-8624

ЗВЕЗДОГЛЯД ВИКТОР НИКИТОВИЧ, СМИРНОВ СЕРГЕЙ БОРИСОВИЧ, ШАРЫГИН БОРИС ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 11/10

Метки: исправления, многократных, обнаружения, одиночных, ошибок

Опубликовано: 23.09.1984

Код ссылки

<a href="https://patents.su/4-1115055-ustrojjstvo-dlya-ispravleniya-odinochnykh-i-obnaruzheniya-mnogokratnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления одиночных и обнаружения многократных ошибок</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для контроля делительного блока

Случайный патент: Ребристый купол