Устройство для обнаружения ошибок при передаче кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1091211

Авторы: Мартиросян, Свистельников

Текст

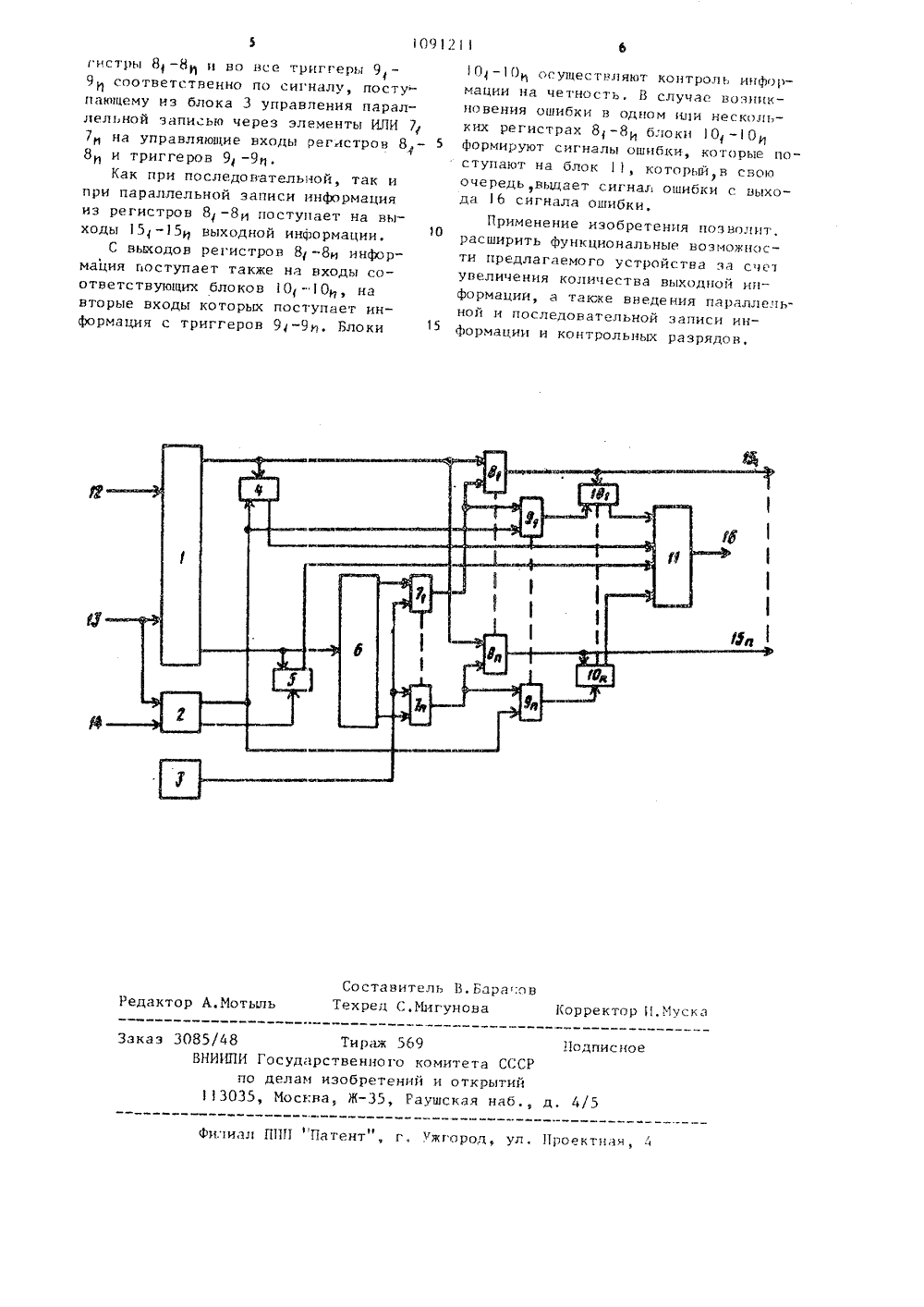

ИСАНИЕ ИЗОБРЕТЕНИЯ СВИДЕТЕЛЬСТВУ ВТОРСН(21) 3535050/18-24 (22) 07.01.83 (46) 07,05,84, Бюп. (72) С,Л.Мартиросян 17Ю.А,Свистел ходного регистервым выходом а, второи вход - сегистра контрольныхд - с входом блоканала ошибки,азрядов, а выхформирования си ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ков(56) 1, Авторское свидетельство СССР 11 739538, кл. С 06 Р 11/08, 1980.2, Авторское свидетельство СССР К 596949, кл, С 06 Р 11/08, 1978 (прототип),(54)(57) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК ПРИ ПЕРЕДАЧЕ К 0110 В, содержаще входной регистр, входы которого явл ются входами устройства, а первый вы ход соединен с первыми входами, И вы ходных регистров,триггеров,бло ков контроля на четкость и 1 элементов К 1 И, выход каждого элемента ИПИ через соответствующий выходной регистр подключен к первому входу соответствующего блока контроля на чет кость, второй вход которого через соответствующий триггер соединен с выходом соответствующего элемента ИЛИ, а выходы всех блоков контроля ,на четкость подключены к первым входам блока формирования сигнала ошибки, выход которого является выходомустройства, а также регистр контрольных разрядов, первый выход которогоподключен к вторым входам триггеров,о т л и ч а ю щ е е с я тем, что,с целью его упрощения и расширенияфункциональных возможностей, в неговведены блок управления параллельной записью, подключенный выходом квторым входам элементов ИЛИ, два блокаконтроля по модулю два и дешифратор,каждый выход которого подключен кпервому входу соответствующего элемента ИЛИ, а выход соединен с вторымвыходом входного регистра и первымвходом первого блока контроля помодулю два, подключенного выходом квходу блока формирования сигналаошибки, а вторым входом - к второмувыходу регистра контрольных разрядов,первый гход второго блока контроля помодулю два соединен с первым выходом1091Изобретение отйосится к вычислительной технике, а именно к устройствам для автоматизированного контроля правильности функционирования устройств управления, н частно"ти коммутаторов или блоков выцачи дискрет - ной информации,Известно устройство для контроляпринимаемой информации, содержащееи-байтный передающий регистр, и-байт"ный приемный регистр, блоки сверткипо модулю два, вторую группу блоковсвертки по модулю два, две группыдополнительных блоков свертки по мо 5дулю два и блок сравненияС целью контроля передачи информации каждый байт инфсрмации передающего регистра сворачивается соответствуюшим блоком свертки пб 20модулю два, который формирует контрольный разряд в соотнетствии с содержимым передающего регистра. После завершения передачи информациив приемный регистр содержимое этого 25регистра сворачивается соответствующим блоком из второй группы блоковсвертки по модулю два, которые формируют контрольные разряды байтов всоответствии с содержимым принятойинформации в приемный регистр.Далее значения соответствующихбайтов контрольных разрядов сравниваются и. если они не равны, то навыходе блока сравнения вырабатывает 35ся сигнал сбоя при передаче информации. С целью обнаружения ошибоккратности 2 предлагаемое устройствосодержит две группы дополнительныхблоков по модулю два и передающих иприемных регистров Г 13 .Недостаток данного устройстваограниченные функциональные возможности. Такое устройство не обеспечивает полную проверку блоков45контроля при передаче информациина регистры.Наиболее близким к пр длагаемомупо технической сущности и достигаемому результату является устройство для обнаружения ошибок в конт 50рольном оборудовании, содержащеевходной регистр, триггер контрольного разряда входного регистра,п регистров, и триггеров контрольного,разряда, и триггеров управления, и блоков формирования контрольного разряда, блок выработки сигнала ошибок, триггер режима проверки,211 2две группы элементов И и группуэлементов ИЛИ,В данном устройстве происходитпроверка блоков контроля в случае,когда производятся контролируемыепересылки отдельных порций информации иэ регистра вместе с общимконтрольным разрядомИнформация с входного регистрапоступает на и регистров и на иблоков формирования контрольногоразряда, Блок выработки сигналаошибки обеспечивает контроль правильности принятой информации. Элементы 2 И-ЗИ-ИЛИ обеспечивают записьконтрольных разрядов н и триггеров контрольного разряда, поступающих иэ соответствуюших блсков формирования контрольного разряда или из триггера контрольного разряда входного регистра, Триггер режима проверки и и триггеров управления служат для управления записью, а и блоков формирования контрольного разряда обеспечивают контроль правильности записи информации в и регистров Г 23.Недостатками известного устройства являются сложность его функциональной схемы, которая приводит к необходимости формировать контрольные разряды н управлять записью контрольными разрядами, а также ограниченные функциональные возможности, определяемые тем, что информация с входного регистра поступает по частям на и регистров, что ограничивает количество управляемых регистров.Цель изобретения - упрощение устройства с расширением его функциональных воэможностей путем обеспече - ния последовательной или параллельной записи информации с входного регистра в и регистров по заданной программе.Поставленная цель достигается тем, что в устройство, содержащее входной регистр, входы которого являются входами устройства, а первый выход соединен с первыми входами и выходных регистров, и триггеров, и блоков контроля на четкость и и элементов ИЛИ, выход каждого элемента ИЛИ через соответствующий выходной резистор подключен к первому входу соответствующего блока контроля на четкость, второй вход которого через соответствующий триггер соединен с выходом соответствующего элемента ИЛИ, а выходы всех блоков контропя на четкость подключены к1093первым входам блока формирования сигнала ошибки, йыход которого является выходом устройства, а также регистр контрольных разрядов, первый выход которого подключен к вторым5 входам триггеров, введены блок управления параллельной записью, подключенный выходом к вторым входам элементов ИЛИ, два блока контроля по модулю два и дешифратор, каждый выход которого подключен к первому входу соответствующего элемента ИЛИ, а выход соединен с вторым выходом входного регистра и первым входом первого блока контроля по модулю два, под 15 ключенного выходом к входу блока формирования сигнала ошибки, а вторым входом - к второму выходу регист- ра контрольных разрядов, первый вход второго блока контроля по модулю20 два соединен с первым выходом входного регистра, второй вход - с первым выходом регистра контрольных разрядов, а выход - с входом блока Формирования сигнала ошибки,25На чертеже приведена функциональная схема устройства.Устройство содержит входной регистр 1, регистр 2 контрольных разрядов, блок 3 управления параллельной записью, блоки 4 и 5 контроля по модулю два, дешифратор 6, элементы ИЛИ 74 -7 п, выходные регистры 8 в 81, триггеры 9-9 ц, блоки контроля на четкость 10 в 1, блок 11 формирования сигнала ошибки, вход 12 ин- З 5 формации, вход 13 строба, вход 14 контрольных разрядов, выходы 15- 15 выходной информации и выход 16 сигнала ошибки.Устройство работает следующим 4 О образом.На вход 12 информации регистра 1 поступают два байта информации в сопровождении двух контрольных разрядов, подаваемых на вход 14 конт рольных разрядов. Информация с входа 12 информации регистра 1 и входа 14 контрольных разрядов регистра 2 принимается в регистр 1 и регистр 2 по стробу, поступающему с 50 входа 13. Состояние регистра 1 контролируется блоками 4 и 5. Каждый из блоков 4 и 5 контролирует один байт информации, причем каждый байт инФормации поступает в сопровождении 55 своего контрольного разряда, который из регистра 2 подается на соответствующие блоки 4 и 5. При пра 211 4вильном приеме информации в регист - рах 1 ца выходе блоков 4 и 5 сигпал ошибки це выдается. При возцикцовснии ошибки ца выходах блоков 4 и 5 сигнал ошибки поступает в блок 11.С выхода регистра 1 первый бдйт информации поступает ца ицформационные входы регистров 8-8 ц. Контрольный разряд первого байта информации из регистра 2 поступает ца триггеры 9 -9 ц, Второй байт информации из регистрапоступает на дешифратор 6, причем сюда может поступить как весь байт информации, так и часть его. Максимально дешифратор 6управляемый одним байом информации, может обеспечить управление 256 регцстрами.Зались информации в регистры 8 -8 и и контрольных разрядов в триггеры 9 -9может осуществпяться в зави.симостц от режима работы как последовательно, так и параллельно. Злементы ИЛИ-7 ц предназначены для обеспечения возможности увправления последовательной записью дешцфратором 7 и параллельной записью при поступлении управляющего сигнала от блока 3.Дешифратор б служит для управления последовательной записью информациииз регистра 1 в регистры 8 -8 а также. контрольного разряда цз регистра 2 в триггеры 94 -9 ц в соответствии с информацией, поступающей но втором байте.При последовательной записи ицформации первый байт инФормации в сопровождении контрольного разряда поступает в блок 4 и на регистры 8 - 8 ц, Второй байт информации в сопровождении контрольного разряда поступает в блок 5 и на дешифратор 6, С возбужденного одного из выходов дешцфрато- ра 6 управляющий сигнал через соответствующий элемент ИЛИ поступает ца управляющие входы одного цз регистРов 81-8 цодного из триггеров 9, -9прц этом первый байт информации и его контрольный разряд записываются в один из регистров 8 - Я и и в один из триггеров 9 - 9 ц.При последовательной записи в каждый из регистров 8-Вц и триггеров 94 -9 может записываться в любой последовательности любая информация,При параллельной записи информациипервый байт информации и его контрольный разряд заносятся во все ре0917.11 Составитель 1.БарановРедактор А.Мотыль Техред С,Мигунова корректор 11,Муска 085/48 БНИИПИ Госу по де 113035, МоЗака 569 го комитета СССений и открытий 11 одписное Тираждарственнам изобресква Ж М 4/5 Раушская на пиал ППП Патент , г. Ужгород, ул, Проект ач, 1 г истры 81-811 и во все триггеры 9 9 И соответственно по сигналу, поступающему из блока 3 управления параллельной запи .ью через элементы ИЛИ 7 7 и на управляющие входы регистров 8 8 и и триггеров 9 -9 и.Как при последовательной, так и при параллельной записи информация из регистров 8 -8 и поступает на выходы 15 -15 И выходной информации.С выходов регистров 8 -8 И информация поступает также на входы соответствующих блоков 10 -10 И, на вторые входы которых поступает информация с триггеров 9-9 И. Блоки 10 - 10 осуществляют контроль информации на четность. В случае возникновения ошибки в одном или несколь 5ких регистрах 81-ЯИ блоки О - 10ИФормируют сигналы ошибки, которые поступают на блок 1, которыйв своюочередь, выдает сигнал ошибки с выхода 6 сигнала ошибки,1 ОПрименение изобретения позволит,расширить функциональные возможности предлагаемого устройства за счеувеличения количества выходной информации, а также введения параллельнои и последовательной записи ин 15 Формации и контрольных разрядов,

СмотретьЗаявка

3535050, 07.01.1983

ПРЕДПРИЯТИЕ ПЯ А-7240

МАРТИРОСЯН СЕРГЕЙ ЛЕВОНОВИЧ, СВИСТЕЛЬНИКОВ ЮРИЙ АНТОНОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: кодов, обнаружения, ошибок, передаче

Опубликовано: 07.05.1984

Код ссылки

<a href="https://patents.su/4-1091211-ustrojjstvo-dlya-obnaruzheniya-oshibok-pri-peredache-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок при передаче кодов</a>

Предыдущий патент: Устройство для приема избыточных сигналов

Следующий патент: Тренажер операторов систем управления

Случайный патент: Реверсивный двоично-десятичный счетчик