Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

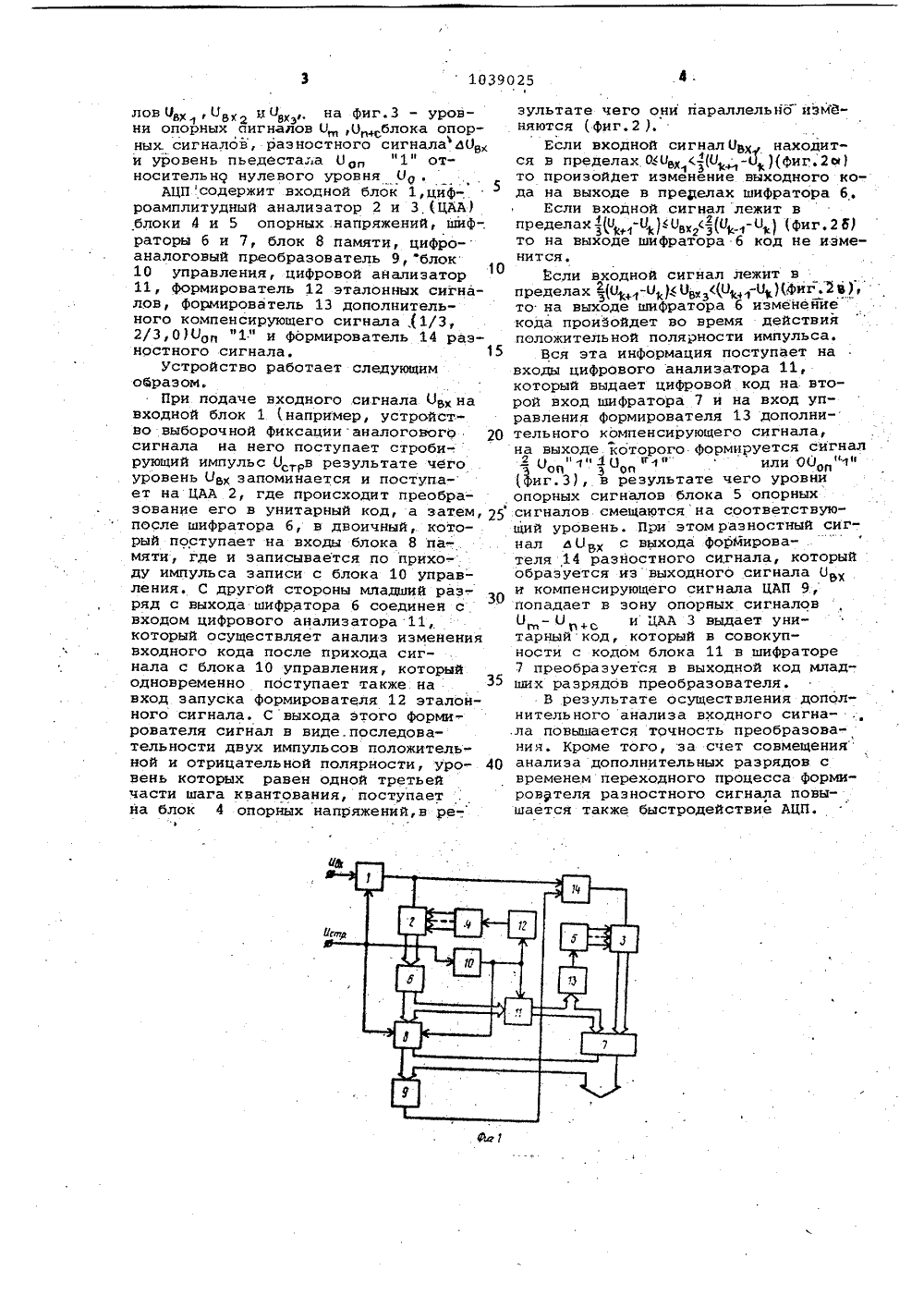

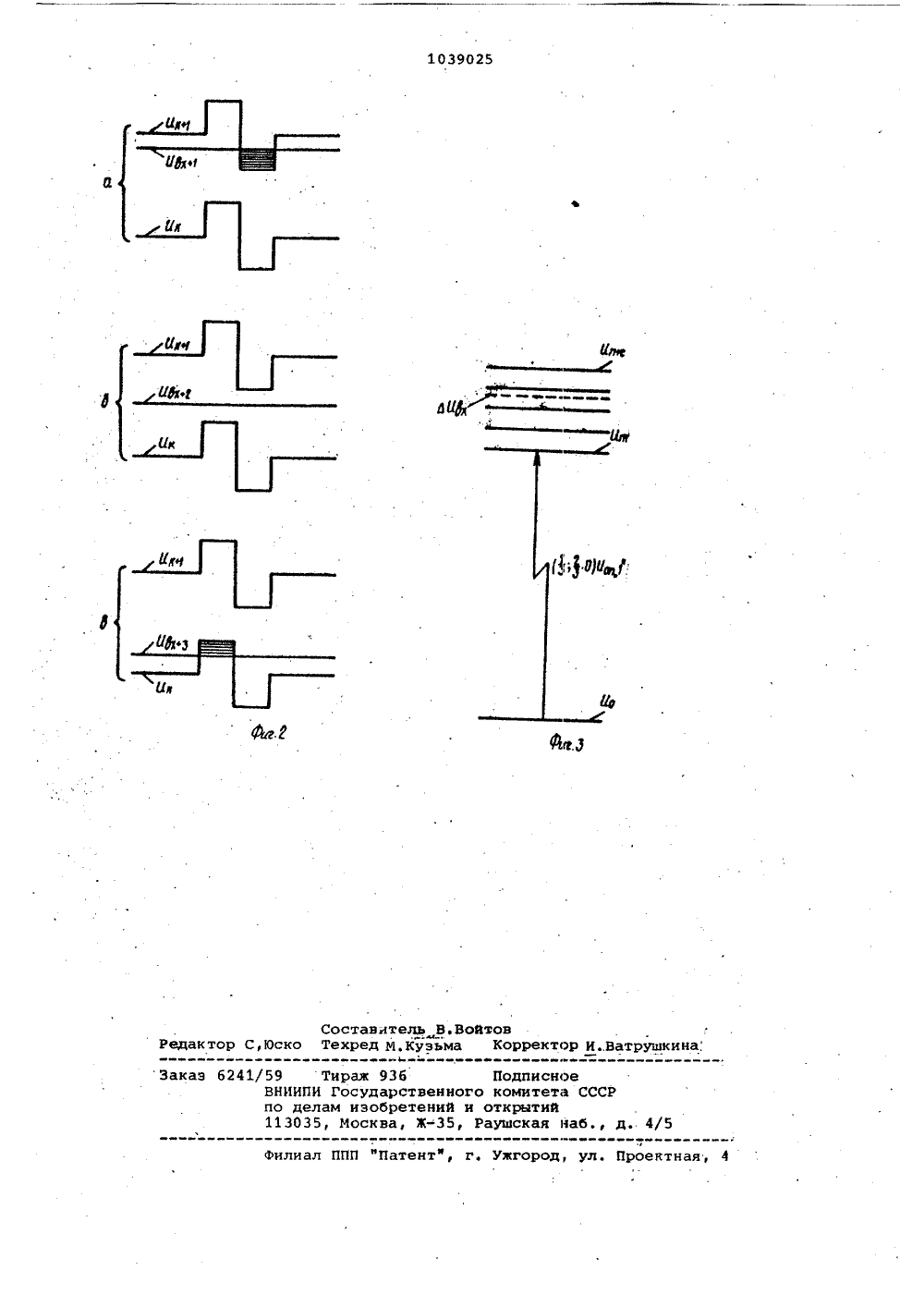

,103 СЮ Н 03 К 13 02 рми ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГЩ(56) 1; Авторское"свидетельство СССР М 660242,.кл. Н 03 К 13/18, 8.12.75.2. Бахтиаров Г.Д. и др. Аналого цифровые преобразователи. М., 1180, . с.200, рис. 7,24 (прототип). (54)(57) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий входной блок, вход которого соединен с входной шиной, а выход .подключен к первому входу формирова.теля разностного сигнала и входу первого цифрового амплитудного ана-. лизатора, опорные входы которого соединены с соответствующими выходами первого блока опорных напряжений,.а выход через последовательно подклю-ченные первый шифратор и блок памяти, первый вход управления которого соединен со стробирующей шиной под,ключен к соответствующим старшим разрядам выходной шины и входам цифро-аналогового преобразователя, выход которого соединен с вторым входом формирователя разностного сигнала, выход которого соединен с входом второго цифрового амплитудного анализатора, опорные входы кое торого подключены к соответствующим выходам второго блока опорных напряжений, а выход - к первому входу второго шифратора, выходы которого соединены с,соответствующими младшими разрядами выходной шины, о тл и ч а ю щ и и с я . тем, что, . с целью повышения быстродействия и точйости преобразовании, в него введены формирователь дополнительного компенсирующего сигнала,дифровой анализатор, формирователь эталонных сигналов и блок управления, вход которого соединен Со стробирую-щей шиной, а выход через формирователь эталонных сигналов подключен к входу первого блока опорных напряжений и непосредственно к второму входу управления блока па.мяти входу управления цифрового ана- Я лизатора, вход которого соединен с выходом мпадшегО разряда первого шифратора, а выход - с вторым входом второго шифратора и входом Фо рователя дополнительного компенсирующего .сигнала, выход которого ( подключен к входу второго блока опор-ных напряжений.Изобретение относится к вычислительной и измерительной .технике и может быть использовано в аппаратуре автоматического контроля и управления для преобразования аналоговогог 5 сигнала в цифровой кодИзвестен аналого-цифровой преоб-; ,разователь ( АЦП ), который содержит шесть резисторов, пять компараторов, шифратор и регистр, усилитель, три ключа, два элемента И-НЕ, элемент И,30 два элемента И-ИЛИ-НЕ, два триггера и логическое устройство.Первый вход усилителя соединен с вторыми входами первого и пятого компараторов, а выход соединен с вто рыми входами первого и пятого компараторов, а выход соединен с вторыми входами второго третьего и четвертого компараторон. Второй вход усилителя соединен с выходами трех ключей, 20 вход первого ключа соединен с общей шиной источника эталонного напряжения, вход второго ключа соединен с первым входом пятого кампаратора, первый вход третьего ключа - с пятым и 25 шестым резисторами, управляющий вход первого ключа через элемент И-НЕ - с вторым входом элемента И, с выходом второго элемента И-ИЛИ-НЕ и с первым входом второго триггера. Вторые входы триггеров соединены с входной шиной генератора тактовых импульсов, Два выхода каждого триггера соединены с четырьмя входами логического устройства. Четыре входа первого элемента И-ИЛИ-НЕ соединены соответственно с первым выходом первого, второго, третьего и четвертого компараторов и с пятым, шестым, седьмым и восьмым входами логического устройства, четыре входа второго элемента 40 И-ИЛИ-НЕ соединены соответственно с вторыми выходами второго, третьего,: четвертого и пятого компараторов и с девятым, десятым, одиннадцатым и двенадцатым входами логического 45 устройстна. Второй выход первого компаратора и первый выход пятого компаратора соединены соответственно с тринадцатым и четырнадцатым входами логического устройства, а его выход соединен с входом шифратора, а выход элемента И соединен с вздорим входом третьего ключа 1.1Недостатком преобразователя при многоразрядном преобразовании является большое число пороговых элементов во втором разряде обработки.Известен параллельно-последовательный АЦП, содержащий входной блок, выход которого соединен с пер вым входом формирователя резйстного сигнала и с входом первого парал" лельного АЦП, выполненного на цифровом амплитудном анализаторе, блоке опорных напряжений, шифраторе и блоке памяти, выход первого АЦП подключен через цифроаналогдвый преобразователь ЦАП к второму входу формирователя разностного сигнала, выходкоторого соединен с вторым параллельным АЦП младших разрядов обработки 2 ,К недостаткам известного преобразо нателя следует отнести ограниченную точность и быстродействие.Цель изобретения - понышение быстродействия и точности преобразования.Поставленная цель достигается тем, что, в параллельно-последовательный аналого-цифровой преобразователь, содержащий входной блок, вход которого соединен с входной шиной, а выход подключен к первому входу формирователя разностного сигнала и входу первого цифрового амплитудного анализатора, опорные входы которого соединены с соответствующими выходами первого блока опорных напряжений, а выход через последовательно подключенные первый шифратор и блок памяти, первый вход управления которого соединен со стробирующей шиной подключен к соответствующим старшим разрядам выходной шины и входам цифро-аналогового преобразователя, выход которого соединен с вторым входом формирователя разностного сигнала, выход которого соединен с входом второго цифрового амплитудного анализатора, опорные входы которого подключены к соответствующим выходам второго блока опорных напряжений, а выход - к первому входу второго шифратора,. выходы которого соединены с соответстнующими младшими разрядами выходной шины, дополнительно введены формирователь дополнительного компенсирующего сигнала, цифровой анализатор, формирователь эталонных сигналов и блок управления, вход которого соединен со стробирующей шиной, а выход через формирователь эталонных сигналов подключен к входу первого блока опорных напряжений и непосредственно к второму вхо" ду управления блока памяти и входу управления цифрового анализатора, вход которого соединен с выходом младшего разряда первого шифратора,. а выход - с вторым входом второго шифратора и входом формирователя дополнительного компенсирующего сигнала, выход которого подключен к входу второго блока опорных напряжений.На фиг.1 приведена структурная электрическая схема параллельно-последовательного аналого-цифрового преобраЗователя АЦП), на фиг.2 временные диаграмы ойорных сигналов 0 , О к+1 и входных сигназультате чего они параллельно изменяются (фиг.2 ).Если входной сигналОВХ находится в пределах 00 в О, -)(фиг.2 а) то произойдет измененйе вйходного кода на выходе в пределах шифратора 6.Если входной сигнал лежит в пределах ЦО -Ц)6 О(ЯО, -О,) (фиг2 Й то на выходе шифратора б код не изменится.Если входной сигнал лежит в пределах -(О,+1-ОД Озз 0,-0,) Йиг.2) у то на выходе шифратора 6 изменейие кода произойдет во время действия положительной полярности импульса.Вся эта информация поступает на входы цифрового анализатора 11, который выдает цифровой код на второй вход шифратора 7 и на вход управления Формирователя 13 дополнительного компенсирующего сигнала, на выходе которого Формируется сигналОП 3 Оп0 "1 ц 10 ф"или ОО "1"оп 1 иг,3), в результате чего УРовни опорных сигналов блока 5 опорных сигналов смещаются на соответствующий уровень. При этом разностный сигнал аОВх с выхода форМирователя 14 разностного сигнала, который образуется извыходного сигнала ОЭ и компенсирующего сигнала ЦАП 9, попадает в зону опорных сигналов И - О + и ЦАА 3 выдает унип р+старный код, который в совокупности с кодом блока 11 в шифраторе 7 преобразуется в выходной код младших разрядбв преобразователя.В результате осуществления дополнительного анализа входного сигна.ла повышается точность преобразования. Кроме того, за счет совмещения анализа дополнительных разрядов с временем переходного процесса формирователя разностного сигнала повышается также быстродействие АЦП. лов Овх, Ивк и Из,. на Фиг.3 - уровззни опорных сигналов 00 блока опорных, сигналов, разностного сигнала й 0и уровень пьедестала Оо "1" относительно нулевого уровня 0 .АЦПсодержит входной блок 1,циф-. роамплитудный анализатор 2 и 3,(ЦАА) блоки 4 и 5 опорных напряжений, шиф-, раторы б и 7, блок 8 памяти, цифро- аналоговый преобразователь 9, блок 10 управления, цифровой анализатор 11, формирователь 12 эталонных сигналов, формирователь 13 дополнительного компенсирующего сигнала,(1/3, 2/3,0)Иол "1" и формирователь 14 разностного сигнала. 15Устройство работает следующим образом.При подаче входного сигнала Оэ на входной блок 1 1 например, устройство выборочной Фиксациианалогового 20 сигнала на него поступает стробирующий импульс О в результате чЕго уровень Ивх запоминается и поступает на ЦАА 2, где происходит преобразование его в унитарный код, а затем, 25 после шифратора б, в двоичный, который поступает на входы блока 8 па- мяти, где и записывается по прихо-. ду импульса записи с блока 10 управления. С другой стороны младший разряд с выхода шифратора б соединен с30 входом цифрового анализатора 11, который осуществляет анализ изменения входного кода после прихода сигнала с блока 10 управления, который одновременно пбступает также на вход запуска формирователя 12 эталонного сигнала. С выхода этого формирователя сигнал в виде.последовательности двух импульсов положительной и отрицательной полярности, уро вень которых равен одной третьей части шага квантования, поступает на блок 4 опорных напряжений,в .Ре-Ф1039025 Составитель В.Войтоведактор С,Юско Техред М,Кузьма Корректое а Еав И Ватрушкина,д. 4 лиал ППП "Патентф, г. ужгород, ул. Проектная, 4Заказ 6241/59 Тираж 93 бВНИИПИ Государственно по делам изобретений 113035, Москва, ЖПодписноео комитетаоткрытийРауыская на

СмотретьЗаявка

3368323, 08.12.1981

ПРЕДПРИЯТИЕ ПЯ В-2201

ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ, МАХОВ ВЛАДИМИР АЛЕКСАНДРОВИЧ, ВОЛОЩЕНКО СЕРГЕЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H03K 13/02

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 30.08.1983

Код ссылки

<a href="https://patents.su/4-1039025-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Устройство для обнаружения сбоев в импульсной последовательности

Следующий патент: Преобразователь кода в частоту

Случайный патент: Устройство для отображения информации на газоразрядной индикаторной панели