Запоминающее устройство с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

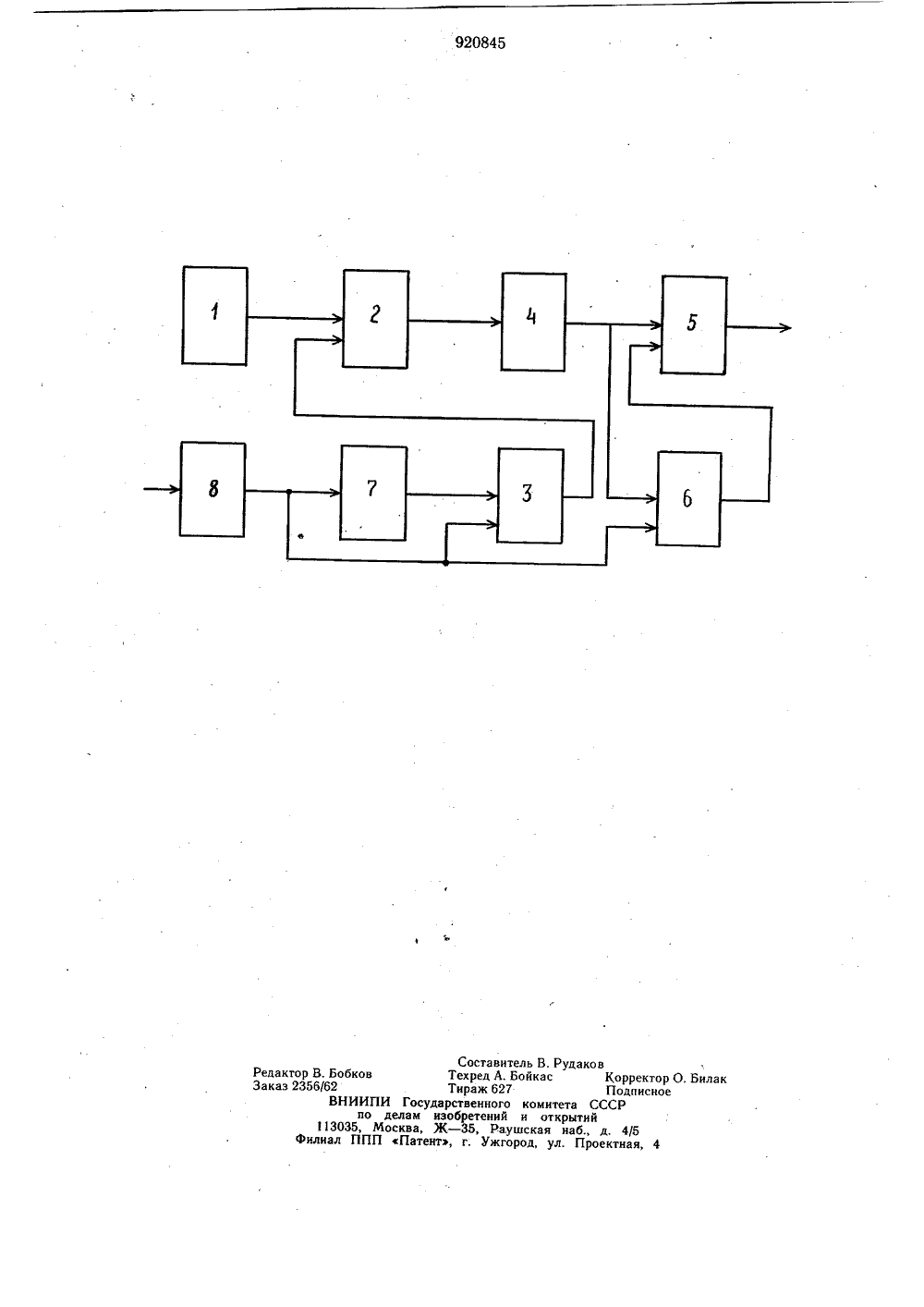

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик1Изобретение относится к запоминающимустройствам.Известно запоминающее устройство, содержащее накопитель, регистры адреса и числа и схему сравнения 1,Недостатком этого устройства являетсято, что оно только обнаруживает ошибку,не исправляя ее.Наиболее близким к данному техническим решением является устройство, содержащее накопительный блок, регистр считанного слова, кодирующий и декодирующийблок и блок коррекции 2.Недостатком этого устройства являетсяотсутствие . возможности полной проверкинакопительного, кодирующего и декодирующего блоков при помощи каких-либо тестов, 15задаваемых, например, из процессора. Таким образом, отсутствует возможность пол-,ного контроля запоминающего устройства иневозможна локализация неисправности, чтоснижает надежность устройства,20Цель изобретения - повышение надежности устройства.Поставленная цель достигается тем, чтов запоминающее устройство с исправлениемошибок, содержащее накопитель, регистр числа, выход которого подключен к первым входам блока коррекции и блока кодирования- декодирования, .выход которого соединен с вторым входом блока коррекции, выход которого является выходом устройства, введены сумматоры по модулю два, генератор импульсов, регистр сдвига и блок местного управления, причем входы сумматоров по модулю два подключены соответственно к. выходам накопителя и регистра сдвига, а выходы - ко входам регистра числа, выход блока местного управления соединен свторым входом кодирования-декодирования, первым входом регистра сдвига и входом геНератора импульсов, выход которого подключен ко второму входу регистра сдвига, вход блока местного управления является управляющим входом устройства.На чертеже изображена структурная схема запоминающего устройства с исправлением ошибок.Устройство содержит накопитель 1. группу сумматоров по модулю два 2, регистр 3 сдвига с числом разрядов на единицу больше числа разрядов считанного слова, регистр 4, числа, блок 5 коррекции, блок 6 кодирования-декодирования, генератор 7 импульсов,служащий для генерации начальной единицы, блок 8 местного управления, состоящий, например, из последовательно соединенных двухразрядного регистра и дешифратора режима диагностики (на чертеже не показаны).5Выход регистра 4 подключен к первым входам блока 5 и блока 6, выход которого соединен со вторым входом блока 5. Входы сумматоров 2 подключены соответственно к выходам накопителя 1 и регистра 3, а выходы - к входам регистра 4. Выход блока 8 соединен со вторым входом блока 6, первым входом регистра 3 и входом генератора 7, выход которого подключен ко второму входу регистра 3. Вход блока 8 является управляющим входом устройства, на который подаются сигналы процессора (на чертеже не показан) .Работу устройства проиллюстрируем при функционировании в трех основных режимах.Основной рабочий режим. Слово, считанное из накопителя 1, через сумматоры 2 поступает на регистр 4. Поскольку в этом режиме регистр 3 постоянно находится в нулевом состоянии, то слово поступает на регистр 4 без изменения. Если при считывании произошла ошибка, то блок 6 формирует коррек тирующий код и блок 5 исправляет ошибку ,или, если произошла двойная ошибка, то блок 6 запрещает коррекцию и выдает сигнал сбоя.Первый режим диагностики. Из процессора выдается код режима Д 1, при котором блок 8 формирует сигнал, запрещающий коррекцию ошибок. При этом считанная информация поступает в процессор без исправления и сравнивается с эталоном. Таким образом может быть обнаружена неисправная ячейка памяти.Второй режим диагностики. Из процессора выдается код режима Д 2, при котором блок 8 снимает запрет коррекции ошибок и включает генератор 7.При считывании информации:накопителя 4 О 1 начальная единица заносится в нулевой разряд регистра 3, что приводит к инверсии нулевого разряда считанного слова. Таким образом имитируется одиночная ошибка в нулевом разряде, которая должна быть ис правлена, что контролируется процессором путем сравнения с эталоном. При каждом последующем считывании информации единица в регистре 3 передвигается в следующий разряд, т.е. происходит имитация одиночной ошибки поочередно в каждом разряде считанного слова. При переходе единицы в последний разряд регистра 3 происходит инверсия сразу в двух разрядах считанного слова, т.е. имитируется двойная ошибка, которая не исправляется, но должна быть обнаружена.Таким образом, при правильной работе блока 6 при к-циклах считывания (где м - число разрядов. считанного слова) происходит сравнение с эталоном, а в (к 1)-ом цикле считывания происходит запланированный сбой, который учитывается процессором.Использование средств, обеспечивающих работу запоминающего устройства в описанных выше режимах диагностики, позволяет контролировать все ячейки накопителя и блок кодирования-декодирования. В результате обеспечивается полнота запоминающего устройства с исправлением ошибок, что приводит к повышению надежности устройства и сокращению времени поиска неисправности.Формула изобретенияЗапоминающее устройство с исправлением ошибок, содержащее накопитель, регистр числа, выход которого подключен к первым входам блока коррекции и блока кодирования-декодирования, выход которого соединен с вторым входом блока коррекции, выход которого является выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит сумматоры по модулю два, генератор импульсов, регистр сдвига и блок местного управления, причем вхбды сумматоров по модулю два подключены соответственно к выходам накопителя и регистра сдвига, а выходы - к входам регистра числа, выход блока местного управления соединен с вторым входом блока кодирования-декодирования, первым, входом регистра сдвига и входом генератора импульсов, выход которого подключен к второму входу регистра сдвига, вход блока местного управления является управляющим входом устройства.Источники информации,принятые во внимание при экспертизе 1. Хетагуров Я. А Руднев Ю. П. Повышение надежности цифровых устройств методами избыточного кодирования, М., Энергия, 1976, с. 224.2, Авторское свидетельство СССР Юо 607281,кл. б 1 1 С 29/00, 1976 (прототип),Составитель В. Рудаков Редактор В. Бобков Техред А. Бойкас Корректор О. Билак Заказ 2356/62 Тираж 627 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий13035, Москва, Ж - 35, Раушская наб д. 4/5 Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2830665, 17.10.1979

ПРЕДПРИЯТИЕ ПЯ М-5769

АЙНШТЕЙН ГЕРМАН ИОСИФОВИЧ, ЛЕВШИН ВЕНИАМИН ИВАНОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, ошибок

Опубликовано: 15.04.1982

Код ссылки

<a href="https://patents.su/3-920845-zapominayushhee-ustrojjstvo-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением ошибок</a>

Предыдущий патент: Аналоговое запоминающее устройство

Следующий патент: Устройство для контроля блоков долговременной памяти

Случайный патент: Подогреватель