Устройство для исправления ошибок в дискретной информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

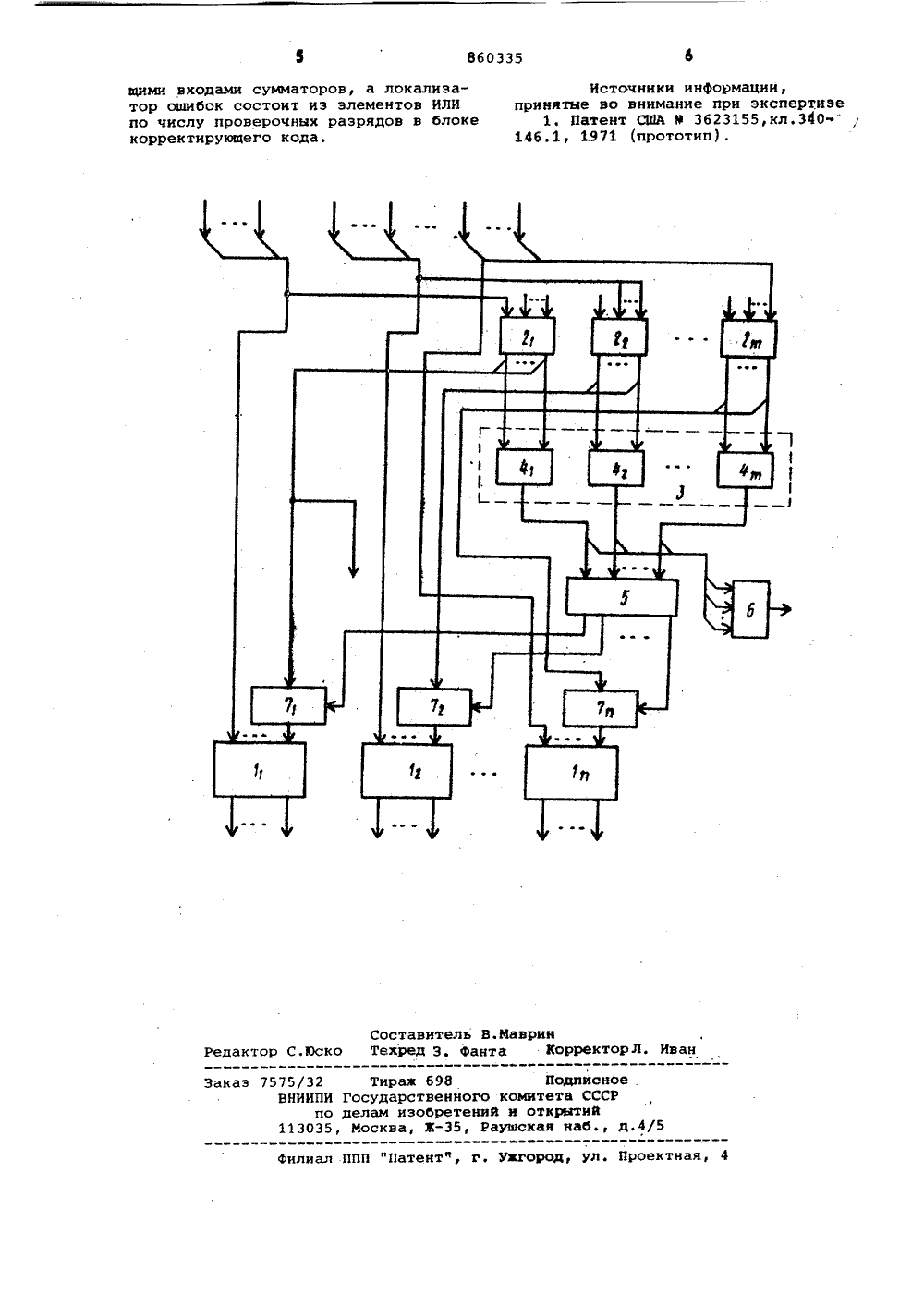

Сеез Сфеетсмнх Соцмалнстмческих РеспубликОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДИТИЛЬСТВУ(22) Заявлено 220678 (21) 2634206/18-09с присоединением заявки Ио(и)860335 Рм Кз Н 0411/08 Н 03 К 13/34 Государствеииый комитет СССР ио делам изобретеиий и открытий(53) УДК 621.394. .14(088.8) Дата опубликования описания 300881(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В ДИСКРЕТНОЙ ИНФОРМАЦИИ Изобретение относится к электросвязи и может использоваться в многоканальных системах передачи информацииаИзвестно устройство для исправления сшибок в дискретной информации,содержащее локалиэатор ошибок, выходы которого соединены с соответствующими входами дешифратора и с соответствующими входами элемента ИЛИ,а также сумматоры по числу разрядовв блоке корректирующего кода ).1 1Однако известное устройство обеспечивает исправление только однойошибки и не позволяет обнаруживать 15и исправлять ошибки в М смежных двоичных разрядах.Цель изобретения - повышение исправляющей способности за счет исправления ошибок в группах смежных разрядов блока корректирующего кода,Для достижения цели в устройстводля исправления ошибок в дискретнойинформации, содержащее локализаторошибок, выходы которого соединены с 25соответствуххцими входами дешифраторай с соответствующими входами элемента ИЛИ, а также суммат.ры по числуразрядов в блоке корректирующего коа, введены дополнительные сумматоры 30 по числу проверочных разрядов в блоке корректирующего кода и блоки ключей йо числу разрядов в блоке корректирующего кода, при этом входы сумматоров объединены с соответствующими входами дополнительных сумматоров, выходы ко" торых соединены с соответствующими входами локализатора ошибок и с соответствующими сигнальньвщ входами блоков ключей, управляющие входы и выкоды которых соединены соответственно с соответствующими выходами дешифратора и с соответствующими входами сумматоров, а локалиэатор ошибок состоит из элементов ИЛИ по числу проверочных разрядов в блоке корректирующего кода.На чертеже приведена структурнаяэлектрическая схема предложенного устройства.устройство содержит сумматоры 11,1 2у 1 н, дополнительные сумматорй 2, 2 2 н, локалиэатор 3 ошибок, состоящий иэ элементов ИЛИ 4, 4 4 дешифратор 5, элемент ИЛИ 6, блоки 7, 7 7 ключей.Устройство работает следуФцим Ьбраэом.Прн поступлении по,входным шинам входного корректирующего кода в каж 860335Формула изобретения 45 50 55 60 дом дополнительном сумматоре 24 осуществляется проверка соответствующего контрольного соотношения путем сложения и вычитания соответствующих Р-ичных разрядов. В результате в каждом дополнительном сумматоре 24, 2 у,2 п, фиксируется значение ".О", еслиукаэанных разрядах нет одиночной шибки, и величина ошибки со своим знаком в противоположном случае, На выходе каждого элемента ИЛИ 4 локалиэатора 3 появляется сигнал "О", если в дополнительном сумматоре 24 получено значение "О", и сигнал "1", если это значение отлично от нуля. Если на выходе хотя бы одного элемента ИЛИ 4 локализатора 3 появляется ф 1" элемент ИЛИ формирует сигнал о наличии ошибки. Кроме того, совокупность сигналов на выходе элементов ИЛИ 4,4 локализатора 3 указывает номер отказавшего разряда. Этот номер ( поступает на вход дешифратора 5 и йа его соответствующем ( -м) выходе появляется сигнал, отпирающий блок 7, ключей. При этом на одни входысоответствующего сумматора 1 поступает со входных шин значение 1-го(искаженного) Р-ичного разряда, а надругие - значение ошибки в этом разряде с выходов дополнительного сумматора 2 через блок 7 ключей. В сумматоре 1 производится вычитание эначения ошибки из значения искаженногоразряда (или сложение с ннм в зависимости от знака, с которым полученаошибка), в результате чего на выходах этого сумматора 1 формируетсяисправленное значение этого разряда.В других сумматорах 1, соответствую-:щих неискаженным разрядам, на входы поступают только значения этих разрядов со входных шин, которые беэ изменения передаются на выход, поскольку соответствующие блоки 7 ключей (кро-. ме 7 заперты сигналами с выходов дешнфратора 5.Например, вместо правильной кодовой комбинации 0221131 принята комбинация 0221101, т,е.произошло искааение шестого слева Р-ичного разряда(нуль), вместо двоичной комбинации11 в этом разряде принята комбинация00, что соответствует двоичной ошибке(М). Проверка контрольных соотношений в дополнительных сумматорах 24, 2 2, 2 , (по модулю 4) дает соответственно значения 1 - 1 " 0 - 1 =-13, 2 - 2 - 0 - 1 =-1. = 3, О - 21 - 1 = О, вместо 1 - 1 -3 - 1 = 0,2 - 2 - 3 - 1 = О, О - 2 - 1 - 1 = О. Наличие ненулевых результатов на выходах сумматоров 24, 2 вызывает. положение сигналов "1" на выходах элементов ИЛИ 44, 42 локализатора 3 и на входы дешифратора 5 поступает двоичный код 110, обозначающий номер искааенного разряда (6). На шестом выходе дешифратора 5 появляется сигнал 5 10 15 20 25 30 35"1", который открывает блок 7 ключей, и в сумматоре 1 б происходит сложение значения искаженного шестого разряда (О) со значением ошибки с выходов дополнительного сумматора 2 (3). В результате на выходах сумматора 1 появляется исправленное значение шестого разряда (3). Остальные разряды проходят на выходные шины Юеэ изменений,Если ошибка происходит в разрядах 1, 2, 4, соответствующих контрольным разрядам х, у, , то в этом случае значение ошибки в соответствующем доволнительном сумматоре (2 З 2 й 2 ) получается с противоположным знаком. Поэтому в сумматорах 1 , 1, 14 при коррекции производится операция вычитания, а не сложения,Технико-экономические преимущества предлагаемого устройства заключаютсяв его более высокой корректирующейспособности, поскольку оно может обнаруживать и исправлять ошибки кратности М в соответствующих Р-ичныхразрядах кода, одновременно устройство является более быстродействующим, чем корректирующие устройства,исправляющие ошибки кратности М ипостроенные на основе последовательных сдвигающих регистров с обрарнымисвязями, так как требует для коррекции меньше тактов. Арифметическиесумматоры, используемые в предлагаемом устройстве, выпускаются серийнов виде единой интегральной схемы(например, четырехразрядный арифметико-логический блок),так что оно .обладает высокой технологичностью,Устройство для исправления ошибок в дискретной информации, содержащее локализатор ошибок, выходы которого соединены с соответствующими входами дешифратора и с соответствующими входами элемента ИЛИ, а также сумматоры по числу разрядов в блоке кор ректирующего кода, о т л и ч а ю - щ е е с я тем, что, с целью повышения исправляющей способности за счет исправления ошибок в группах смеаных разрядов блока корректирующего кода, введены дополнительные сумматоры по числу проверочных разрядов в блоке корректирующего кода и блоки ключей по числу разрядов в блоке корректирующего кода, при этом входы сумматоров объединены с соответствующими входами дополнительных сумматоров, выходы которых соединены с соответствующими входами локалиэатора ошибок и с соответствующими сигнальными входами блоков ключей, управляющие входы и выходы которых соединены соответственно с соответствующими выходами дешифратора и с соответствуюа филиал ППП "Патент", г, Уагород, ул. Проектна щими входами сумматоров, а локалиэатор ошибок состоит из элементов ИЛИпо числу проверочных разрядов в блокекорректирующего кода75/32 Тирам 698 ВНИИПИ Государственногопо делам иэобретени 113035, Москва, й, Р Источники инФормации,принятые во внимание при экспертизе 1, Патент СЮА 9 3623155,кл.340 146.1, 1971 (прототип).Подписное омитета СССР и открытий ушская наб., д.4/5

СмотретьЗаявка

2634206, 22.06.1978

ПРЕДПРИЯТИЕ ПЯ Г-4677, ВОЕННАЯ ОРДЕНОВ ЛЕНИНА, ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ И СУВОРОВА АКАДЕМИЯ ИМ. Ф. Э. ДЗЕРЖИНСКОГО

ЕЩИН КОНСТАНТИН КОНСТАНТИНОВИЧ, ЗАВОЛОКИН АНАТОЛИЙ КУЗЬМИЧ, ЗАРОВСКИЙ ВИТАЛИЙ ИВАНОВИЧ, МОШКОВ АЛЕКСЕЙ АЛЕКСЕЕВИЧ, МУСАТОВ ИГОРЬ ФЕДОРОВИЧ, РЕЙНЕР ВАЛЕНСИЯ ИВАНОВНА, ЮФЕРОВА ЕВГЕНИЯ КИРИЛЛОВНА

МПК / Метки

МПК: H03M 13/05

Метки: дискретной, информации, исправления, ошибок

Опубликовано: 30.08.1981

Код ссылки

<a href="https://patents.su/3-860335-ustrojjstvo-dlya-ispravleniya-oshibok-v-diskretnojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок в дискретной информации</a>

Предыдущий патент: Устройство цикловой синхронизации

Следующий патент: Устройство для измерения частости искажения блоков информации различной длины

Случайный патент: Сушилка кипящего слоя