Демодулятор дискретных сигналовс фазоразностной модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

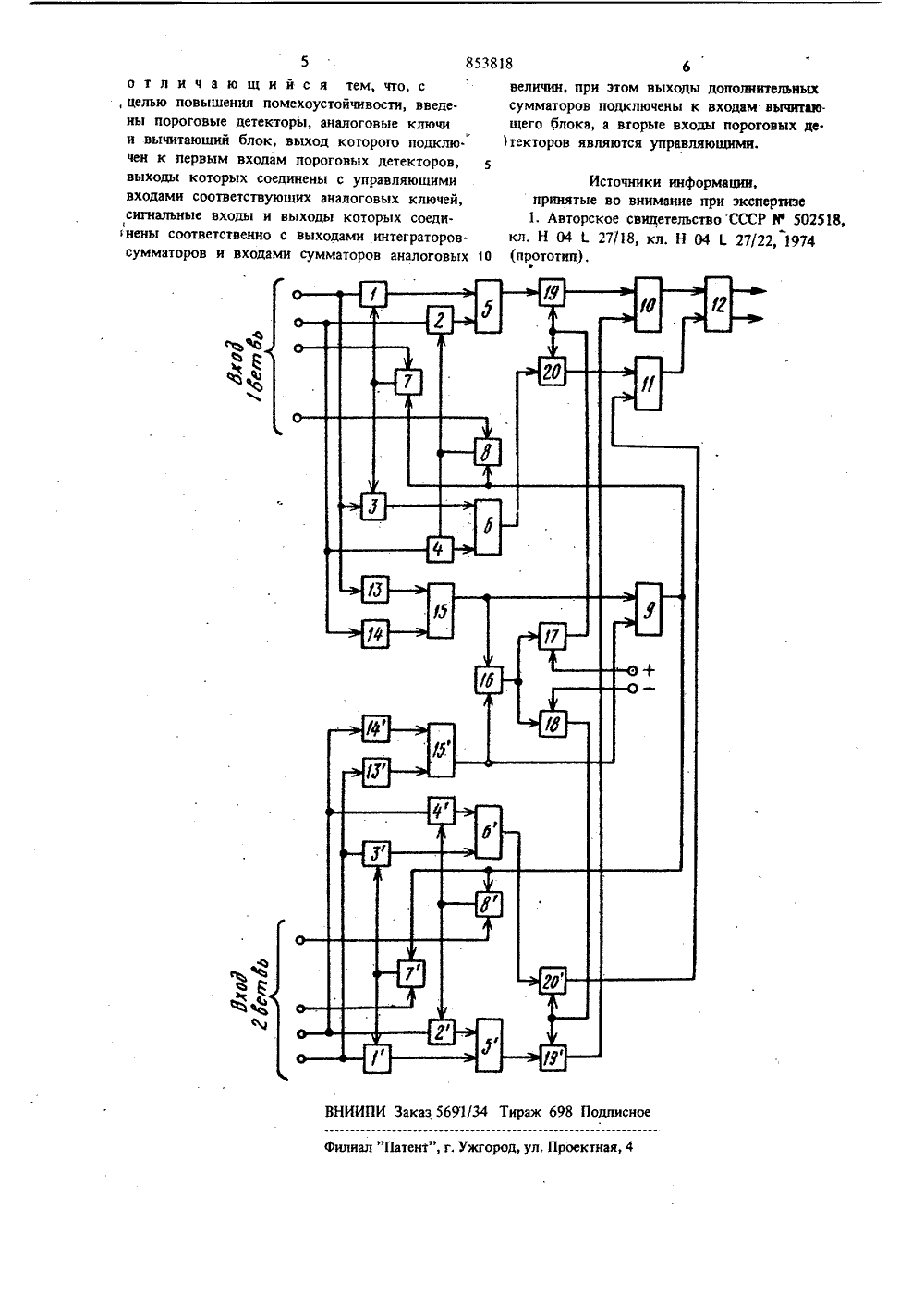

(п 853818 ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(5)М; Кд. Н 04 1. 27/22 Ркударстеенный квинтет СССР ае делам язебратений к открытей(72) Автор зобретени епкин и Ю. Ф. Пелег(54) ДЕМОДУЛЯТОР ДИСКРЕТНЫХ СИГНАЛОВ С ФАЗОРАЗНОСТНОМОДУЛЯЦИЕЙ известен фззорззодные ые с соот. у авт. св. 1 Р 502518 скретных сигналов с цией, содержащий вх множители, соединенн По основн демодулятор постной мод ключевые пе Изобретение относится к технике связи,ожет использоваться в системах передачи дискретной информации и является усовер шенствованием известного изобретения, опи анного в авт, св. 1 Р 502518.ветствующимн интеграторами. сумматорами и подключенные управляющими входами к выходам компараторов, на сигнальные входы которых поданы сигналы, задержанные на одну посылку, а управляющие входы подключе. иы к выходу генераторз линейно изменяющего. ся напряжения, и сумматоры аналоговых вели чии, входы которых подключены к выходам соответствующих интеграторов-сумматоров, а выходы - к решающему блоку, содержацпш также блок вычисления модулей входных сигналов, соединенный с дополнительным сумматором, выход .которого подключен к генератору линейно изменяющегося напряжения (Ц. Однако известный демодулятор дискретных сигналов имеет низкую помехоустойчивость.Цель изобретения - повышение помехоус. тойчнвости.Для этого в известный демодулятор дискрет ных сигналов с фазораэностной модуляцией, содержащий входные ключевые перемножители, соединенные с соответствующими интегратора. мн.сумматорами и подключенные управлявши. ми входами к выходам компараторов, на сигнальные входы которых поданы сигналы, задержанные на одну посылку а управляющие входы подключены к выходу генератора ли. нейно изменяющегося напряжения, и суммато. ры аналоговых величин, входы которых подключены к выходам соответствующих интеграторов-сумматоров, а выходы - к решающему блоку, содержащий также блок вычисления модулей входных сигналов, соединенный с дополнительным сумматором, выход которого подключен к генератору линейно изменяющегося напряжения, введены пороговые детекторы, аналоговые ключи и вычнтающий блок, выход которого подключен к первым входамДемодулятор дискретных сигналов с фазоразностной модуляцией содержит входныеключевые перемиожители 1 - 4, 1 - 4, интеграторы.сумматоры 5, 6, 5, 6, компараторы7, 8, 7, 8, генератор 9 линейно изменяющего.ся напряжения, сумматоры аналоговых величин 10, 11, решающий блок 12, блоки вы.числения модулей входных сигналов 13, 14,13, 14, дополнительные сумматоры 15, 15,вычитаюший блок 16, пороговые детекторы17, 18, аналоговые ключи 19, 20, 19, 20.Демодулятор дискретных сигналов с фазо.разностной модуляцией работает следующимобразом,15 20 25 Если уровни сигналов в обеих ветвях раэ.несения примерно одинаковы, то сигналы из канальных фильтров приемника, содержащие синфазные и квадратурные составляющие п.ой посылки, передаются на входные клю.чевые перемножители 1 - 4 и 1 - 4, и синфазные и квадратурные составляющие и-вой35 посылки - на компараторы 7, 8 и 7, 8, которые сравнивают входные сигналы с линейно изменяющимся напряжением генератора 9 и формируют временные интервалы, в те.чение которых входные сигналы подаются на интеграторы сумматоры 5,6 и 5, 6 соответ.ственно. Напряжения с выходов интеграторов. сумматоров через замкнутые аналоговые ключи 19, 20 и 19, 20 поступают на входы сумматоров аналоговых величин 10, 11, которые управляют работой решающего блока 12,Генератор 9 формирует линейно изменяю.щееся напряжение, скорость изменения кото.рого прямо пропорциональна сумме модуль ных величин синфазной и квадратурной со.ставляющих принимаемого сигнала по обеим ветвям разнесения, которая получается иа выходах дополнительных сумматоров 15, 15, Модульные величины входных сигналов форми. руются в блоках 13, 14 и 13, 14 путем умножения аналоговой величины на ее знак. Та. ким образом, входные сигналы подаются на интеграторы-сумматоры 5, 6 и 5, 6 в течение 30 пороговых детекторов, выходы которых соединены с управляющими входами соответствующих аналоговых ключей, сигнальные входы и выходы которых соединены соответственно с выходами интеграторов-сумматоров и входа. ми сумматоров аналоговых величин, При этом выходы дополнительных сумматоров подключены к входам вычитающего блока, а вторые входы пороговых детекторов являются управляющими входами. 0На чертеже изображена структурная электрическая схема предложенного демодулятора,времени, прямо пропорционального значениямниии-, 1где Х - синфазная составляющая и.войпосылки первой ветви разнесения;- квадратурная составляющая инойпосылки первой ветви разнесения;х 1 - сиифазная составляющая п-", -войпосылки второй ветви разнесения;У- квадратурная составляющая и вой посылки второй ветви разнесения,и обратно пропорционально сумме модулейвеличины напряжения, поступающих на входгенератора линейно изменяющегося напряже.ния 9.При изменении уровней сигналов в ветвяхразнесения, например при замираниях, вычи.тающий блок 16 через пороговые детекторы17, 18 управляет аналоговыми ключами 19,20 и 19, 20 таким образом, что, если на.пряжение на выходе вычитающего блока 16положительно и по абсолютной величине боль.ше порогового напряжения, размыкаются ана.логовые ключи 19, 20, и сигнал первой ветви разнесения не проходит на сумматорыаналоговых величин 10, 11. Если же напряжение иа выходе вычитающего блока 16 отрицательно и по абсолютной величине большепорогового напряжения, размыкаются аналоговые ключи 19, 20, и сигнал второй ветвиразнесения не проходит на сумматоры аналоговых величин 10 и 11. Таким образом авто.матически отключается та ветвь разнесения,уровень сигнала в которой оказывается нижепорогового, и имеющиеся в этой ветви помехи не влияют на работу решающего блока 12.Пороговое напряжение выбирается такимобразом, что управляющий сигнал проходитчерез пороговые детекторы 17, 18 на аиало.говые ключи 19, 20 и 19, 20 с выхода вычитающего блока 16 лишь при увеличенииразности напряжений, поступающих на входыблока 16 с выходов сумматоров 15 и 15,приблизительно в десять раэ. Если же раз.ность между этими напряжениями меньше,управляющий сигнал с вычитаюшего блока16 на аналоговые ключи не проходит, и дан.ный демодулятор работает как известный,Технико. зкономический эффект, создаваемый данным устройством, состоит в снижении требуемого защитного отношения сигнал/помеха при сохранении заданной достоверности, что позволяет использовать передатчики меньшей мощности,Формула изобретенияДемодулятор дискретных сигналов с фазо-разиостной модуляцией по авт, св, Яф 502518,853818 чо е Ъ НИИПИ Заказ 5691/34 Тираж 698 Подписное Филиал "Патент", г. Ужгород, ул, Проектная,о т л и ч а ю щ и й с я тем, что, с , целью повышения помехоустойчивости, введены пороговые детекторы, аналоговые ключи и вычитающий блок, выход которого подклю. чен к первым входам пороговых детекторов, выходы которых соединены с управляющими входами соответствующих аналоговых ключей, сигнальные входы и выходы которых соедииены соответственно с выходами интеграторов- сумматоров и входами сумматоров аналоговых 1 О величин, при этом выходы дополнительныхсумматоров подключены к входам вычитаю.щего блока, а вторые входы пороговых де.детекторов являются управляющими,Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР Иф 502518,кл, Н 0427/18, кл, Н 0427/22, 1974

СмотретьЗаявка

2861289, 16.11.1979

ПРЕДПРИЯТИЕ ПЯ Г-4492

РЕПКИН ВИКТОР ПЕТРОВИЧ, ПЕЛЕГОВ ЮРИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, дискретных, модуляцией, сигналовс, фазоразностной

Опубликовано: 07.08.1981

Код ссылки

<a href="https://patents.su/3-853818-demodulyator-diskretnykh-signalovs-fazoraznostnojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор дискретных сигналовс фазоразностной модуляцией</a>

Предыдущий патент: Частотный манипулятор

Следующий патент: Устройство для приема многопозиционныхсложных сигналов

Случайный патент: Цепная муфта