Устройство преобразования дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

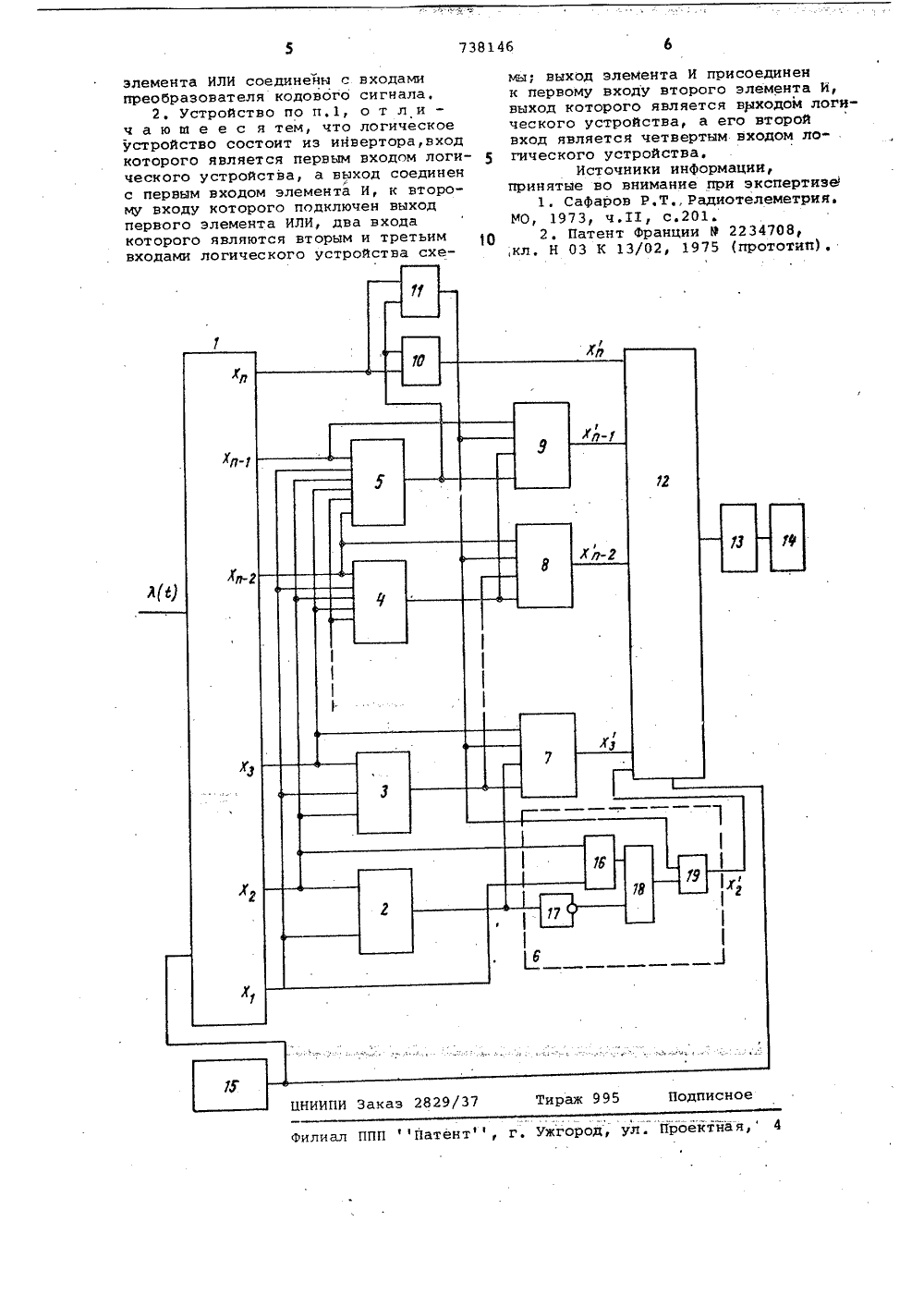

(н)738146 Союз Советскня Социалистических РеспубликОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕТЕДЬСТВУ(61) Допо (22) Заявл нительиое к авт, свид-ву ено 250577 (21) 2488786 нением заявки Мо 18-21 рис осударствениый комитет СССР по делам изобретений н открытий3) Приори о 20 Опубликовано 3005,80 Бюллетень йДата опубликования описания 30.05.8) УСТРОЧСТВО ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ Изобретение относится к телеметрии св яэи.Известно устройство преобразования дискретных сигналов, позволяющее каждую выборку представить в виде и-значного двоичного сигнала, содержащее коммутатор каналов, преобразователь зналог - цифра, накопитель, преобразователь кода и передатчик (1Недостатком этого устройства является то, что при передаче цифровых сигналов простым двоичным кодом при равномерном законе распределения значений выборок исходных сообщений на каждую выборку в среднем - едии ничных посылок.Известно устройство преобразования дискретных сигналов, содержащее преобразователь аналог-циФра, соединенный через анализатор качества посылок с триггером, синхронизатором, выходы которого соединены с синхронными входами преобразователя аналог-код, триггера и синхронизатора (2)Недостатком устройства является необходимость применения на приемной стороне преобразователя сигналов и сложной схема символьной синхронизации. 2Цель изобретения - обеспечение:энергетического выигрыша и уменьшения до нуля систематической ошибкиквантования,5 укаэанная цель достигается тем,что в устройство преобразования дискретных сигналов, содержащее преобразователь аналог-цифра, синхрониэатор, преобразователь кодоэого сиг1 О нала, передатчик,к первому выходупреобразователя аналог-цифра подключены запараллеленные первые, а квторому выходу - эапараллеленные вторые входы элементов И. от первого до15 (и - 2)-го, к-й выход преобразователяаналог-цифра подключен на эапарал,леленные к-е входы элементов И ог=3, 4 и - 1; и-й выход преобра 20 эователя аналог-цифра подключен назапараллельные первые входы элемента ИЛИ и дополнительного элемента И,Выход каждого элемента И присоединенк"первОму входу соответствующего25 логического устройства, у каждого иэкоторых, кроме первого, первый входпредыдущего устройства соединен евторым входом последующего устрбйства, а второй вход первого логичес 30 кого устройства связан с первым выходом преобразователя аналог-циФра. Третьи эапараллеленные входы всех, логических устройств подключены к выход(у дополнительного элемента И, а четвертый вход каждого логического устройства связан соответственно с (г + 1)-м входом элемента И, где г=1, 2 и - 2, Выходы всех логических устройств, а также выход элемента ИЛИ соединены с входами преобразователя кодового сигнала.Логическое устройство состоит изинвертора, вход которого являетсяпервым входом логического устройства, а выход соединен с первым входомэлемента И, к второму входу которогоподключен выход первого элемента ИЛИ,два входа которого являются вторымй третьим входами логического устройства. Выход элемента И присоединенк первому входу второго элемента И,выход которого является выходом логического устройства, а его второйвход является четвертым входом логического устройства,Структурная электрическая схемаустройства приведена на чертеже.устройство содержит преобразователь 1 аналог-цифра, элементы и2, 3, 4, 5 (их число равно и - 2),логические устройства б, 7, 8, 9(их число равно и - 2), элемент ИЛИ10, дополнительный элемент И 11,преобразователь 12 кодового сигнала,модулятор 13, передатчик 14 и синхронизатор 15. Логическое устройствосостоит иэ первого элемента ИЛИ 16,инвертора 17, элемента И 18 и второгоэлемента ИЛИ 19,устройство работает следующимобразом.Если посылка младшего разрядак=О, то на выходе элемента И 2 будетОф 1 на выходе инвертора 17 1;если посылка х=х, т,е, если х =О,Когда посылка х, =1, то йри х =0на выходе элемента И 2 будет 0,на выходе инвертора 17 1, на выходе элемента 1 б также 1, навыходе элемента 18 - 1 и х, =1.Если х 4 =1, то при х=1 на выходеинвертора 17 будет 0 , на выходеэлемента 18 тоже 10 и х =О, а сигнал х будет зависеть от хЗ. Если2х =О, то х=1; если х =1, то х =0:и т,д.Элементы 10 и 11 предназначены длятого, чтобы при входном сигнале, состоящем из одних единиц (х 4=1, х =1,е е хи=1, х 1 =1) выходной сигналтакже состоял йз единичных сигналов,.т.е., Чтобы х=1, х =1., х=1 ф.Действительно,если хе=х==хл- =1 ето сигнал на выходе элемента И 5будет равен 1, Тогда при х =1 сигнална выходе элемента И 11 будет равен1 и он пройдет через элемент ИЛИ 19всех логических устройств., а сигналх=1 пройдет на вход преобразователя 12 через элемент ИЛИ 10.Прн равномерном законе распределения значений выборок, передаваемых и-значными двоичными сигналами, т.е, когда с одинаковой вероятностью встречаются любые из 2 ц и-значных сигналов от 000000 до 11111, относительное уменьшение количества единичных посылок (в импульсном канале это будут импульсы)и(и.)-и й 2 ,.г" нно с этим систематичесвантования становится Одноврем кая ошибка равной нулюКроме то ней нулевой позволяет л передачи ин средний инт го, отбрасывание последпосылки ( х 1 = 0) всегдаибо увеличить скоростьФормации, либо увеличитьервал между импульсами. Формула изобретен 1, устройство преобразования дискретных сигналов, содержащее преобраЗо зователь аналог-цйфра, вход которогосоединен с выходом синхронизатора и с синхронным входом преобразователя кодового сигнала, выход которого через модулятор соединен с входом З 5 передатчика, о т л и ч а ю щ е е с ятем, что,:с целью обеспечения энергетического выигрыша и уменьшения до нуля систематической ошибки квантования, к первому выходу преобразователя аналог-циФра подключены запарал леленные первые,а к второму выходу -запараллеленные вторые входы элементов И от первого до (и)-го,к-й выход преобразочателя ачалог-цифра подключен назапараллелеичые к-е входы 45 элементов И от (к -1)-го до (и - 2)-.го, где к=3, 4 и - 1; и-й выход преобразователя аналог-цифра подключен на запараллеленные первые входы элемента ИЛИ и дополнительного злеемента И; выход каждого элемента И при- соединен к первому входу соответствующего логического устройства, у каждого из которых, кроме первого, первых вход предыдущего устройства соединен с вторым входом последующего устройства, а второй вход первого логического устройства связан с первым выходом преобразователя аналог-циФра; третьи запараллеленные входы всех логических устройств подключены к 66 выходу дополнительного элемента И,а четвертый вход каждого логического устройства связан соответственно с (г + 1)-м входом элементов И, где г=1, 2 и - 2; выходы всех логи ческих устройств, а также выход738146 ППатенти элемента ИЛИ соединены с входами преобразователя кодового сигнала,2, Устройство по п,1, о т л и ч а ю ш е е с я тем, что логическое устройство состоит нз инвертора,вход которого является первым входом логического устройства, а выход соединен с первым входом элемента И, к второму входу которого подключен выход первого элемента ИЛИ, два входа которого являются вторым и третьим входами логического устройства схеьы; выход элемента И присоединенк первому входу второго элемента И,выход которого является выходом логического устройства, а его второйвход является четвертым входом логического устройства,Источники информации,принятые во внимание при экспертизб1. СаФаров Р,Т., Радиотелеметрия.МО, 1973, ч.11, с.2012. Патент Франции Р 2234708,

СмотретьЗаявка

2488786, 25.05.1977

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

САФАРОВ РИЗА ТАДЖИЕВИЧ, КРАСКИН ВЛАДИМИР БОРИСОВИЧ

МПК / Метки

МПК: H03K 13/02

Метки: дискретных, преобразования, сигналов

Опубликовано: 30.05.1980

Код ссылки

<a href="https://patents.su/3-738146-ustrojjstvo-preobrazovaniya-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство преобразования дискретных сигналов</a>

Предыдущий патент: Аналого-цифровой преобразователь

Следующий патент: Коррелометрический цифровой измеритель действующего значения сигнала

Случайный патент: Устройство для увлажнения воздуха