Устройство для логического прогнозирования событий

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1479937

Автор: Соха

Текст

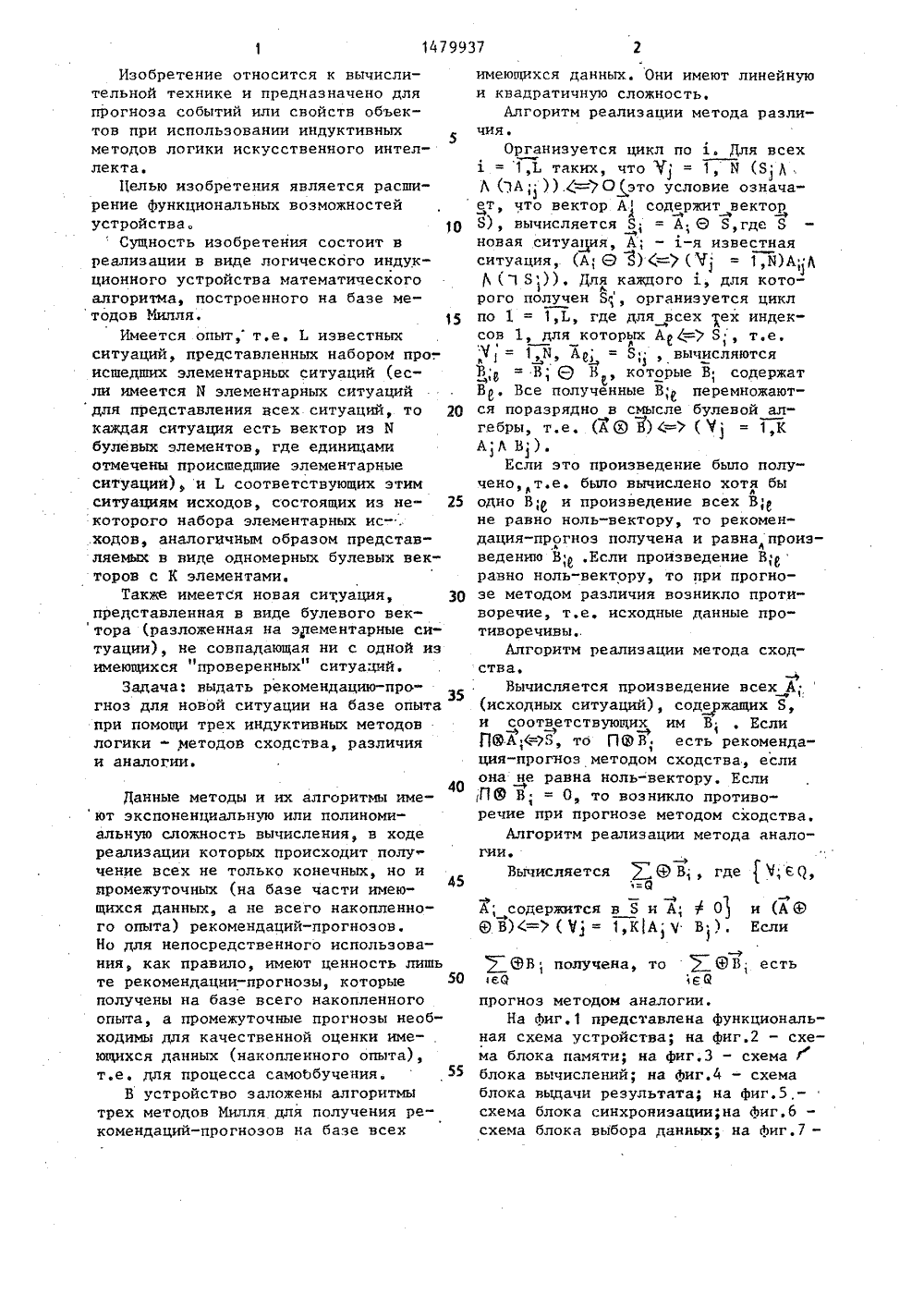

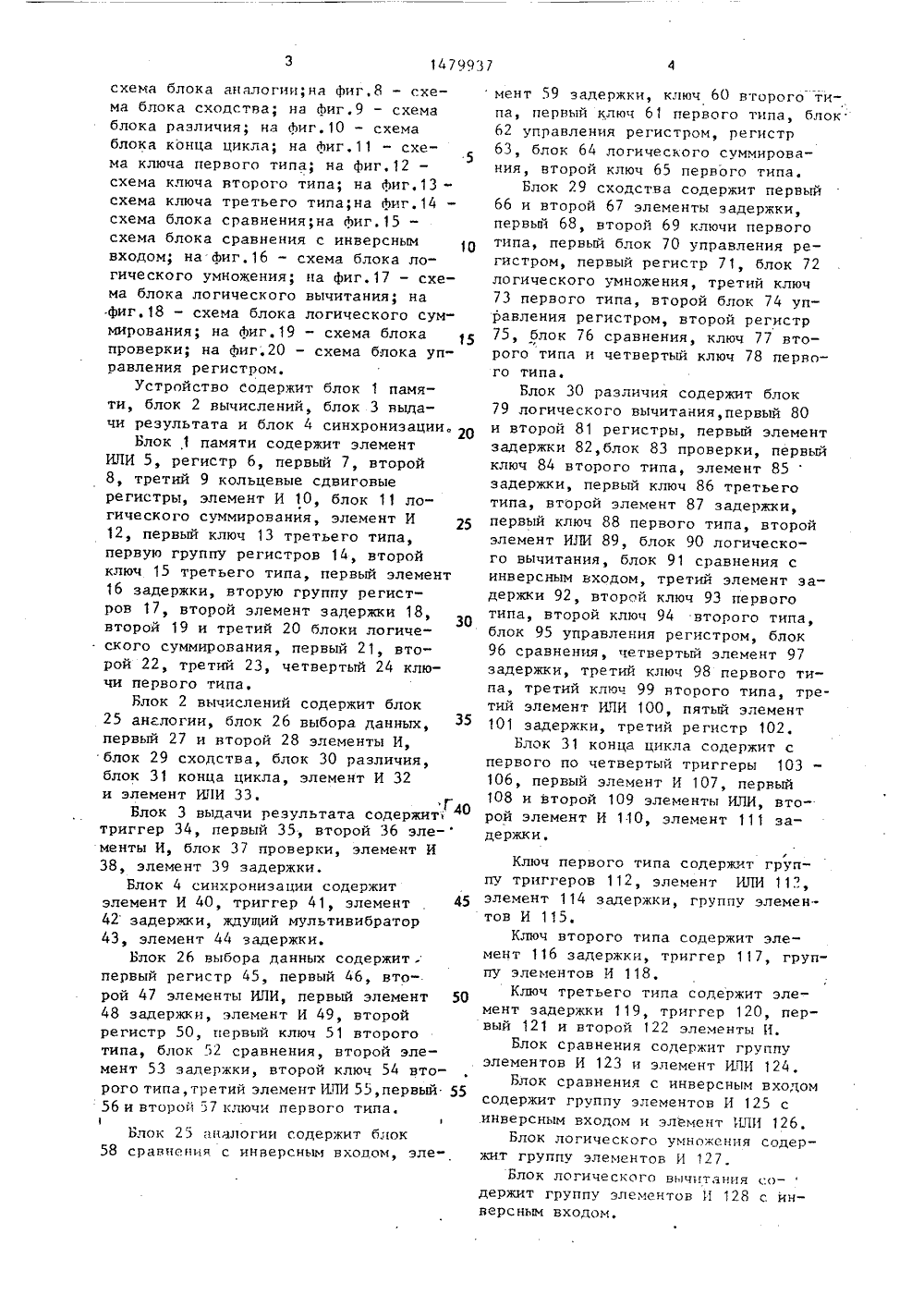

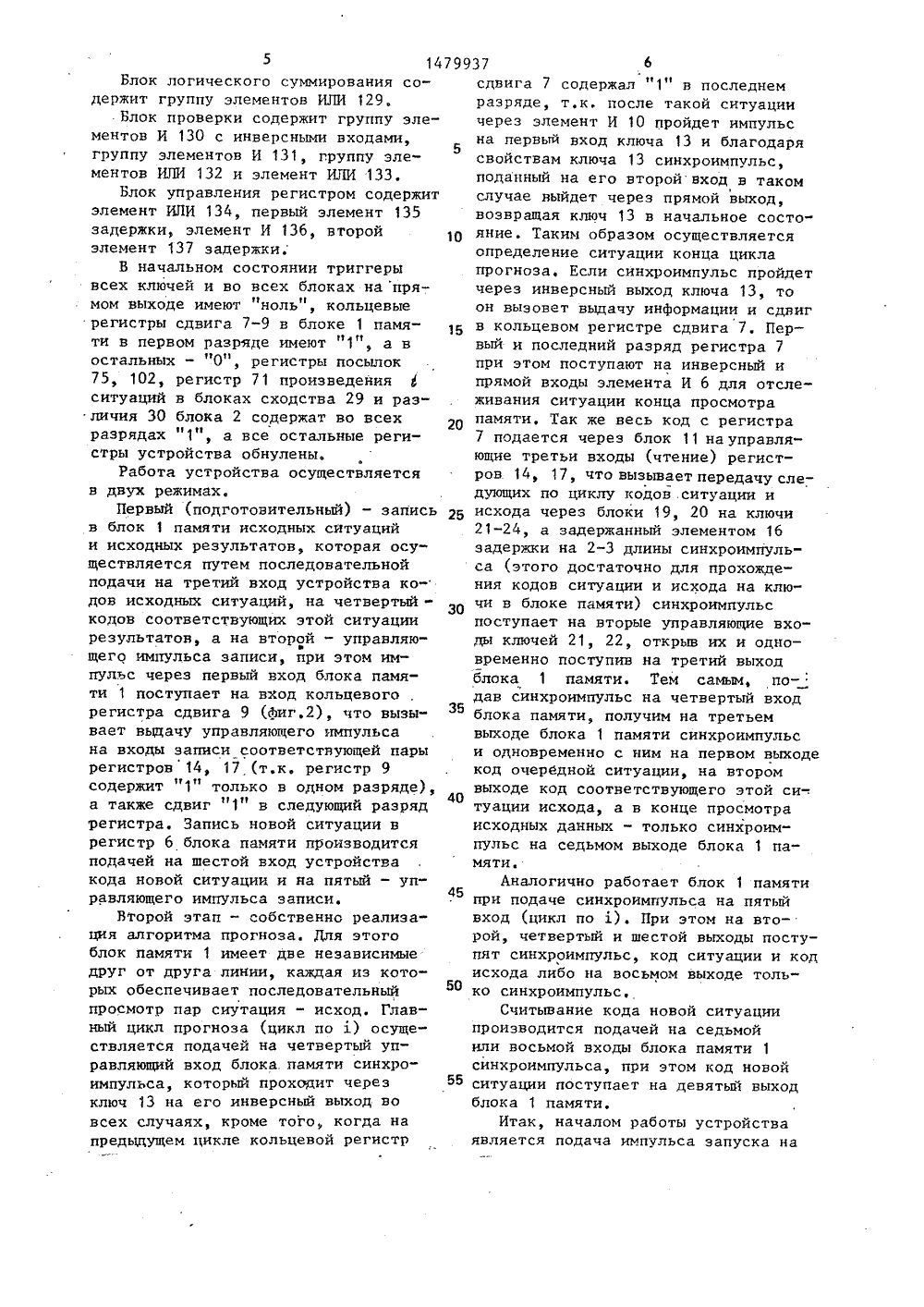

ОЮЗ СОВЕТСКИХ ОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 9) (И 937 А 1)4 С 06 с 18 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИ етевозся т бло нца ИЛИ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Экономический патент ГДР В 236196, кл, С 06 Г 15/18, опублик.1986Авторское свидетельство СССР )19 1013961, кл С 06 Г 15/18, 1981. (54) УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО ПРОГНОЗИРОВАНИЯ СОБЫТИЙ(57) Изобретение относится к области вычислительной техники и lредназначено для прогноза событий илисвойств объектов при использованиндуктивных методов логики искусственного интеллекта. Цель изобрния - расширение Аункциональныхможностей устройства - достигаеттем, что оно содержит блок 1 памблок 2 вычислений, блок 3 выдачизультата и блок 4 синхронизации,причем блок вычислений содержитаналогии, блок выбора данных,блосходства, блок различия, блок коцикла, три элемента И и элемент1 з.п. А-лы, 20 ил,(фиг.17) реализует поразрядное произведение первого кода (с прямоговхода) на инвертированный второйкод (с инверсного входа).Блок логического суммирования(фиг.18) производит поразрядное сложение кодов.Блок проверки (фиг.19) сравнивает на совпадение два кода, поданных на два входа этой схемы.Блок управления регистром (фиг.20)по приходу сигнала на его первыйвход выдает последовательно с за-,держками, обусловленными элементами задержки 135, 137 три.импульсана свои три выхода, интерпретируемыекак считывание, обнуление и записьрегистра.Формула изобретения1. Устройство для логического прогнозирования событий, о т л и - ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей, оно содержит блок памяти, блок вычислений, блок выдачи результата и блок сихронизации, первый вход которого является входом запуска устройства, второй вход блока синхронизации соединен с шестым выходом блока вычислений, первый выход которого соединен с четвертым входом блока выдачи результата, первый выход которого соединен с первым входом блока вычислений и седьмым вкодом блока памяти, первый, второй и третий входы которого являются соответственно входами синхроимпульса записи информации, исходной ситуации и результата устройства, чет" вертый вход блока памяти соединен с выходом блока синхронизации, третий вход которого соединен с третьим выходом блока вычислений, второй выход которого является третьим информационным выходом устройства, четвертый выход блока вычислений соединен с восьмым входом блока памяти, пятый вход которого соединен с десятым выходом вычислительного блока, пятый выход которого является четвертым информационным выходом устройства, шестой и девятый входы блока памяти являются соответственно входами79937 18 синхроимпульса новой ситуации и кодановой ситуации устройства, первый,второй, третий, четвертьп, пятый,шестой, восьмой, седьмой и девятый5выходы блока памяти соединены гответственно с вторым, третьим, четвертым, девятым, седьмым, восьмым, шес-,тым входами блока вычислений и с третьим и пятым входами блока выдачирезультата, второй и третий выходыкоторого соединены соответственно сдесятым и одиннадцатым входами блока вычислений, пятый вход которогосоединен с девятым выходом блока памяти, седьмой, восьмой и девятый выходы блока вычислений являются соответственно шестым, пятым и вторыминформационными выходами устройства,седьмой и восьмой выходы блока вычислений соединены соответственно свторым и первым входами блока выдачи результата, четвертый и пятыйвыходы которого являются седьмым и2 б первым информационными выходами устройства,2, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок вычислений содержит блок аналогии, блокЗО выбора данных, блок сходства, блокразличия, блок коммутации, с первого по третий элементы И, элементИЛИ, первый вход которого соединенс выходом третьего элемента И, первый вход которого соединен с первымвыходом блока коммутации, выходы которого с второго по четвертый являются соответственно четвертым,седьмым и восьмым выходами блока вычислений, первый и второй входы ко-,40торого соединены соответственно свторым и третьим выходами блокасходства, первый и четвертый выходы которого являются соответственнопервым и вторым выходами блока вычислений, четвертый вход блока сходства является первым входом блокавычислений, с первого по четвертыйвходы блока выбора данных являютсясоответственно с второго по пятый5 О входами блока вычислений, третийвход блока конца цикла является шестым входом блока вычислений, первый, пятый, седьмой и восьмой входы блока различия являются соответственно с седьмого по девятый входами блока вычислений, первый, второй и шестой выходы блока выбора данных соединены соответственно с вторым,третьим и четвертым входами блокаразличия, первый и второй выходы ко.торого являются соответственно девятым и десятым выходами блока вычислений, седьмой выход, второй итретий входы и пятыйвыход блокавыбора данных соединены соответственно с первого по четвертый входами блока аналогии, первый и второйвыходы которого соединены соответственно с пятым выходом блока вычислений и вторым входом третьего элемента И, пятый вход блока аналогииявляется одиннадцатым входом блокавычислений, с первого по третийвходы блока сходства соединены соответственно с шестым и первым выходами блока ввода данных и выходом 1479937 20первого элемента И, инверсный входкоторого соединен с третьим выходом блока конца цикла, четвертый5выход которого соединен с инверсным входом второго элемента И, выходкоторого соединен с шестым входомблока различия, третий выход которого соединен с четвертым входом блокаконца цикла, третий выход блока выбора данных соединен с прямыми входами первого и второго элементов И,четвертый выход блока выбора данных соединен с вторым входом элемента ИЛИ, выход которого являетсятретъим выходом блока вычислений, пятый выход блока выбора данных является четвертым выходом блока вычислений,479937 АР УЮ Составитель О.Гречухина Редактор М.Циткина Техред А.Кравчук Корректор О.Кравцовароизводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина Заказ 2544/47 Тираж 669 ВНИИПИ Государственного комитета по иэоб 113035, Москва, Ж, РаПодписноеетениям и открытиям при ГКНТ ССС шская наб., д. 4/5Изобретение относится к вычислительной технике и предназначено для прогноза событий или свойств объектов при использовании индуктивных методов логики искусственного интеллекта.Целью изобретения является расширение функциональных возможностей устройства, 10Сущность изобретения состоит в реализации в виде логического индукционного устройства математического алгоритма, построенного на базе методов Милля, 15Имеется опыт, т,е, Ь известных ситуаций, представленных набором про-. исшедших элементарных ситуаций (если имеется И элементарных ситуаций для представления всех ситуаций, то 20 каждая ситуация есть вектор из И булевых элементов, где единицами отмечены происшедшие элементарные ситуации), и Ь соответствующих этим ситуациям исходов, состоящих из не которого набора элементарных ис- . ходов, аналогичным образом представ" ляемых в виде одномерных булевых векторов с К элементами.Также имеется новая ситуация, 30 представленная в виде булевого вектора (разложенная на элементарные ситуации), не совпадающая ни с одной из имеющихся "проверенных" ситуаций.Задача: выдать рекомендацию-про 35 гноз для новой ситуации на базе опыта при помощи трех индуктивных методов логики - методов сходства, различия и аналогии.40Данные методы и их алгоритмы имеют экспоненциальную или полиномиальную сложность вычисления, в ходе реализации которых происходит получение всех не только конечных, но и промежуточных (на базе части имею 45 щихся данных, а не всего накопленного опыта) рекомендаций-прогнозов, Но для непосредственного использования, как правило, имеют ценность лишь те рекомендации-прогнозы, которые 50 получены на базе всего накопленного опыта, а промежуточные прогнозы необходимы для качественной оценки имеющихся данных (накопленного опыта), т,е. для процесса самообучения, 55В устройство заложены алгоритмы трех методов Милля для получения рекомендаций-прогнозов на базе всех имеющихся данных. Они имеют линейную и квадратичную сложность.Алгоритм реализации метода различия.Организуется цикл по 1. Для всех 1 = 1 ВЬ таких, что У 1 = 1, И (Я Л . Л ЬА, .(=)О это условие означает, что вектор А содержит вектор Я), вычисляется Б; = А;О Я,где Б новая ситуапеия, А; - 1-я известная ситуация, (А, О 3) С= (У = 1,ЯА;Л Л (1 Б, Для каждого х, для которого получен Б(, организуется цикл по 1 = 1,Ь, где для всех трех индексов 1, для которых А(=) Я;, т.е,1,Д, А, = Б , вычисляются 3, = В; Я В , которые В; содержат Вр. Все полученные В, перемножаются поразрядно в смысле булевой алгебры, т.е. (А О В) (=1 ( У 1 = 1,К АЛ В).Если это произведение было получено,т.е. быпо вычислено хотя был одно В, и произведение всех В, не равно ноль-вектору, то рекомендация-прогноз получена и равнапроизведению ВЕсли произведение В, равно ноль-вектору, то при прогнозе методом различия возникло противоречие, т,е. исходные данные противоречивы,.Алгоритм реализации метода сходства.Вычисляется произведение всех А; (исходных ситуаций), содержащих Я, и соответствующих им В, . Если+ДА,(=Б, то П В; есть рекомендация-прогноз методом сходства, если она не равна ноль-вектору, Если ,П В= О, то возникло противоречие при прогнозе методом сходства.Алгоритм реализации метода аналогии.Вычисляется 6 В гдет, Е Ц,1=9А; содержится в Б н А; Ф 0) и (А О В)(=) ( У 1 = 1,КА Ч В), ЕслиЭВ; получена, то , О- В; есть аа 1 Е тяпрогноз методом аналогии,На фиг, 1 представлена функциональная схема устройства; на фиге 2 - схема блока памяти; на фиг.З - схема Р блока вычислений; на фиг,4 - схема блока выдачи результата; на фиг,5, - схема блока синхронизации;на фиг,б - схема блока выбора данных; на фиг,7 -схема блока аналогии;на фиг,8 - схема блока сходства; на фиг.9 - схемаблока различия; на фиг, 10 - схемаблока конца цикла; на фиг,11 - схема ключа первого типа; на фиг,12схема ключа второго типа; на фиг.13 -схема ключа третьего типа;на Лиг.14схема блока сравнения;на Лиг.15 -схема блока сравнения с инверснымвходом; на фиг.16 - схема блока логического умножения; на фиг.17 - схема блока логического вычитания; на.фиг,18 - схема блока логического суммирования; на фиг,19 - схема блокапроверки; на фиг,20 - схема блока управления регистром,Устройство содержит блок 1 памяти, блок 2 вычислений, блок 3 выдачи результата и блок 4 синхронизации. 20Блок 1 памяти содержит элементИЛИ 5, регистр 6, первый 7, второй8, третий 9 кольцевые сдвиговыерегистры, элемент И 10, блок 11 логического суммирования, элемент И12, первый ключ 13 третьего типа,первую группу регистров 14, второйключ 15 третьего типа, первый элемент16 задержки, вторую группу регистров 17, второй элемент задержки 18,второй 19 и третий 20 блоки логического суммирования, первый 21, второй 22, третий 23, четвертый 24 ключи первого типа.Блок 2 вычислений содержит блок25 аналогии, блок 26 выбора данных,первый 27 и второй 28 элементы И,блок 29 сходства, блок 30 различия,блок 31 конца цикла, элемент И 32и элемент ИЛИ 33.Г 40Блок 3 выдачи результата содержит 40триггер 34, первый 35, второй 36 эле-менты И, блок 37 проверки, элемент И38, элемент 39 задержки.Блок 4 синхронизации содержитэлемент И 40, триггер 41, элемент 4542 задержки, ждущий мультивибратор43, элемент 44 задержки,Блок 26 выбора данных содержит .первый регистр 45, первый 46, второй 47 элементы ИЛИ, первый элемент 5048 задержки, элемент И 49, второйрегистр 50, первый ключ 51 второготипа, блок 52 сравнения, второй элемент 53 задержки, второй ключ 54 второго типа, третий элемент ИЛИ 55,первый 5556 и второй 57 ключи первого типа.11Блок 25 аналогии содержит блок58 сравнения с инверсным входам, элемент 59 задержки, ключ 60 второго типа, первый ключ 61 первого типа, блок.62 управления регистрам, регистр 63, блок 64 логического суммирования, второй ключ 65 первого типа.Блок 29 сходства содержит первый 66 и второй 67 элементы задержки, первый 68, второй 69 ключи первого типа, первый блок 70 управления регистрам, первый регистр 71, блок 72 логического умножения, третий ключ 73 первого типа, второй блок 74 управления регистром, второй регистр 75, блок 76 сравнения, ключ 77 второго типа и четвертый ключ 78 первого типа.Блок 30 различия содержит блок 79 логического вычитания, первый 80 и второй 81 регистры, первый элемент задержки 82,блок 83 проверки, первый ключ 84 второго типа, элемент 85 задержки, первый ключ 86 третьего типа, второй элемент 87 задержки, первый ключ 88 первого типа, второй элемент ИЛИ 89, блок 90 логического вычитания, блок 91 сравнения с инверсным входом, третий элемент задержки 92, второй ключ 93 первого типа, второй ключ 94 второго типа, блок 95 управления регистрам, блок 96 сравнения, четвертый элемент 97 задержки, третий ключ 98 первого типа, третий ключ 99 второго типа, третий элемент ИПИ 100, пятый элемент 101 задержки, третий регистр 102.Блок 31 конца цикла содержит с первого па четвертый триггеры 103 106, первый элемент И 107, первый 108 и второй 109 элементы ИЛИ, второй элемент И 110, элемент 111 задержки.ГКлюч первого типа содержит группу триггеров 112, элемент ИЛИ 11:,элемент 114 задержки, группу элементов И 115,Ключ второго типа содержит элемент 16 задержки, триггер 117, группу элементов И 118,Ключ третьего типа содержит элемент задержки 119, триггер 120, первый 121 и второй 122 элементы И.Блок сравнения содержит группуэлементов И 123 и элемент ИЛИ 124.Блок сравнения с инверсным входомсодержит группу элементов И 125 с.инверсным входом и элемент ИЛИ 126,Блок логическага умножения содержит группу элементов И 127.Блок логического вычитания содержит группу элементов И 128 с. инверсным входом, 5 14Блок логического суммирования содержит группу элементов ИЛИ 129,Блок проверки содержит группу элементов И 130 с инверсными входами, группу элементов И 131, группу элементов ИЛИ 132 и элемент ИЛИ 133,Блок управления регистром содержит элемент ИЛИ 134, первый элемент 135 задержки, элемент И 13 б, второй элемент 137 задержки.В начальном состоянии триггеры всех ключей и во всех блоках на прямом выходе имеют "ноль", кольцевые регистры сдвига 7-9 в блоке 1 памяти в первом разряде имеют "1", а в остальных - "0", регистры посылок 75, 102, регистр 7 1 произведения ситуаций в блоках сходства 29 и раз" личия 30 блока 2 содержат во всех разрядах "1", а все остальные регистры устройства обнулены.Работа устройства осуществляется в двух режимах.Первый (подготовительный) - запись в блок 1 памяти исходных ситуаций и исходных результатов, которая осуществляется путем последовательной подачи на третий вход устройства ко- дов исходных ситуаций, на четвертый- кодов соответствующих этой ситуации результатов, а на второй - управляющего импульса записи, при этом импульс через первый вход блока памяти 1 поступает на вход кольцевого регистра сдвига 9 (фиг.2), что вызывает выдачу управляющего импульса на входы записи соответствующей пары регистров 14, 17 т,к. регистр 9 содержит "1" только в одном разряде), а также сдвиг "1" в следующий разряд регистра. Запись новой ситуации в регистр б блока памяти производится подачей на шестой вход устройства кода новой ситуации и на пятый - управляющего импульса записи.Второй этап - собственно реализация алгоритма прогноза. Для этого блок памяти 1 имеет две независимые друг от друга линии, каждая иэ которых обеспечивает последовательный просмотр пар сиутация - исход. Главный цикл прогноза (цикл по 1) осуществляется подачей на четвертыи управляющий вход блока памяти синхроимпульса, который проходит через ключ 13 на его инверсный выход во всех случаях, кроме того, когда на предыдущем цикле кольцевой регистр 79937 6сдвига 7 содержал "1" в последнемразряде, т,к, после такой ситуациичерез элемент И 10 пройдет импульс5на первый вход ключа 13 и благодарясвойствам ключа 13 синхроимпульс,поданный на его второй вход в такомслучае выйдет через прямой выход,возвращая ключ 13 в начальное состо"10 яние. Таким образом осуществляетсяопределение ситуации конца циклапрогноза. Если синхроимпульс пройдетчерез инверсный выход ключа 13, тоон вызовет выдачу информации и сдвигв кольцевом регистре сдвига 7, Первый и последний разряд регистра 7при этом поступают на инверсный ипрямой входы элемента И 6 для отслеживания ситуации конца просмотрапамяти. Так же весь код с регистра7 подается через блок 11 на управляющие третьи входы (чтение) регистров 14, 17, что вызывает передачу следующих по циклу кодов .ситуации и2 В исхода через блоки 19, 20 на ключи21-24, а задержанный элементом 1 бзадержки на 2-3 длины синхроимпульса (этого достаточно для прохождения кодов ситуации и исхода на ключи в блоке памяти) синхроимпульспоступает на вторые управляющие входы ключей 21, 22, открыв их и одновременно поступив на третий выходблока 1 памяти. Тем самым, подав синхроимпульс на четвертый входблока памяти, получим на третьемвыходе блока 1 памяти синхроимпульси одновременно с ним на первом выходекод очередной ситуации, на второмвыходе код соответствующего этой си-.40туации исхода, а в конце просмотраисходных данных " только синхроимпульс на седьмом выходе блока 1 памяти,Аналогично работает блок 1 памятинри подаче синхроимпульса на пятыйвход (цикл по ). При этом на второй, четвертый и шестой выходы поступят синхроимпульс, код ситуации и кодисхода либо на восьмом выходе тольВо ко синхроимпульсСчитывание кода новой ситуациипроизводится подачей на седьмойили восьмой входы блока памяти 1синхроимпульса, при этом код новойситуации поступает на девятый выходблока 1 памяти,Итак, началом работы устройстваявляется подача импульса запуска на40 его первый вход, который поступит вблок 4 синхронизации, запомнится натриггере 41, запустит ждущий мультивибратор 43 и через элемент 42 за.5держки вернет триггер 41 в исходное состояние. Элемент задержки 42выбран так, чтобы мультивибратор 43сформировал ровно один синхроимпульс, который поступит на четвертый вход блока памяти 1, С третьего, первого и пятого выходов блока1 памяти на входы блока 2 поступят.синхроимпульсы, которые включат блок2, код ситуации и код исхода. В процессе своей работы .блок 2 организует цикл просмотра по 1 исходных данных, подавая импульсы на пятый входблока 1 памяти, считывает код новой ситуации, подавая импульс на 20восьмой вход блока 1 памяти, и потомвыдает импульс конца шага цикла через шестой выход блока 2 и блока 4синхронизации либо, отвергнув данную исходную ситуацию и исход как 25негодные для прогноза, выдает импульс через третий выход на блок 4синхронизации. Любой из этих импульсов, поданных на второй или третий вход блока синхронизации 4, 30вызовет те же действия, что и импульсзапуска. По концу цикла по 1 синхроимпульс с седьмого выхода блока 1памяти включит блок 3 выдачи результата, поступив на его третийвход. Последний, подав постоянную"1" на седьмой вход блока 1 памяти,получит кодновой ситуации на своемпятом выходе, подав постоянную "1"на первый, десятый и одиннадцатыйвходы блока 7, если не возникло противоречие в исходных данных при прогнозе соответствующими методами,получит на четвертом входе произведения ситуаций из регистра 71 в блоке сходства, и на выходе четыре,три и два устройства с выходов пять,два и девять блока 2 поступят кодыпрогноза методами аналогии, сходства и различия, Блокировка выдачикода прогноза методов сходства и/или 50различия при противоречии в данных реализуется подачей постоянной"1" на третий и второй соответственно входы блока 3 выдачи результата,при этом признаки возникновенияпротиворечия также поступят на выходы шесть и пять устройства. Блоквыдачи результата, если нет противорачеия при прогнозе, методом сходства сравнит код новой ситуации с кодом произведения ситуации и,если они равны, выдаст н. седьмой вход устройства "1", Концом работы устройства в режиме прогноза следует считать появление постоянной "1" на первом выходе устройства с пятого выхода блока 3 выдачи результата, Блок 2 реализует один цикл прогноза параллельно тремя методами. Код ситуации А, исхода В; и синхроимпульс включения поступают с второго, третьего, четвертого входов напервый, второй, третий входы блока 26 выбора данных и код В, также на второй вход блока 25 аналогии. Если А, = О или В, = О, то блок 26 выбора данных выдаст синхроимпульс со своего четвертого выхода, который пройдет через элемент ИЛИ 33, через третий выход вычислительного блока поступит на блок синхронизации как запрос на организацию следующего шага цикла по . Если и А и В, отличны от нуля, то код А; поступит на первый вход блока 25 аналогии с седьмого выхода блока 26 выбора данных, а также синхроимпульс, вьппедший с пятого выхода блока 26 выбора данных, включит блок 25 аналогии и попадет через выход четыре вычис-, лительного блока на восьмой вход блока 1 памяти, в результате чего код новой ситуации Я поступит через вход блока 2 на вход четыре блока 26 выбора данных и вход три блока 25 аналогии, В результате блок аналогии отработает и выдаст синхроимпульс на свой второй выход, а блок 26 выбора данных проверит вложение кода Я в код А,. Если вложения нет, то блок 26 выбора данных запретит обработку этой ситуации и исхода, выдав через свой четвертый выход, элемент ИЛИ 33 на вход три блока 2 импульс запроса следующих Аи В;. Если А; содержит Б, то код А;, код Б с первого и второго выходов блока 26 выбора данных поступит на второй и третий входы блока 30 различия и код А на второй вход блока 29 сходства, код В поступит на первый вход блока сходства и четвертый вход блока 30 различия с шестого выхода блока 26 выбора данных. Синхроимпульс включения блоков сходства и различия с третьего выхода блока 26 выбора9 147 данных через элемент И 27 поступит на третий вход блока 29 сходства и через элемент И 28 на шестой вход блока 30 различия, если прогноз по этим методам не обрывался противоречием на предыдущих шагах цикла по х. В случае противоречия соответствующие элементы И 27 и/или 28 будут заперты "единицей"/"единицами", подаваемыми на их инверсные входы из блока 31 конца цикла. По концу шага блок 29 сходства выдает синхроимпульс на третий выход, если прогноз можно про" должить, и на второй выход, если возникло противоречие, который поступит на второй или первый входы блока 31 конца цикла, где будет задержан до прихода сигнала о конце шага в блоке 30 различия, если в нем еще не возникло противоречие, иначе блок 31 конца цикла сформирует импульс запроса следующего шага, выдав его через свой второй выход и шестой выход блока 2 на блок 4 синхронизации. По приходу синхроимпульса включения блок 30 различия вычислит Б и организует цикл просмотра данных по 1 через девятый выход блока 2 и седьмой, восьмой, девятый входы того же блока, По концу просмотра данных цикл 1 блок 1 цамяти выдаст импульс конца, который через шестой вход блока 2 поступит на третий вход блока 31 конца цикла, либо до этого блок 30 различия с третьего выхода импульса сообщит о возникновении противоречия, подав его на четвертый вход блока 31 конца цикла. Блок 31 конца цикла либо дожидается импульсов конца шага цикла поиз блока сходства и из блока 1 памяти конца циклов по 1 и по приходу последнего из них формирует запрос на очеред ной шаг цикла по х, либо при противоречии на одном из этих блоков ожидает импульс конца шага с другого и по нему формирует импульс запроса следующего шага, либо при возникновении противоречия и по сходству, и по различию открывает элемент И 32 для .прохождения импульса конца шага по аналогии в конечном счете на блок 4 синхронизации как импульса запроса нового шага цикла по д.Блок 3 выдачи результата включа. ется подачей на его третий вход "1",1 импульс "запоминается" на триггере 34 и "1" с прямого выхода триггера 9937 О34 подается на третий выход, первыйвыход, если не возникло противоречия по сходству, второй выход, еслине возникло противоречия по различию, пятый выход через элемент 39задержки блока 3 выдачи результата,Если на первый выход блока выдачирезультата была подана "1", то через некоторое время, обусловленноезадержкой на считывание нужной информации, на четвертый и пятый входы блока выдачи результата поступяткоды произведения исходных ситуацийиз регистра 7 1 блока 29 сходства иновой ситуации из регистра 6 блока1 памяти. Эти коды проверяются насовпадение в блоке 37 проверки и вслучае, если коды совпадут, блок37 проверки формирует импульс, который пройдет через элемент И 38 начетвертый выход блока выдачи результата, сигнализируя о достижении прогноза методом сходства. Элемент 39задержки выбран так, чтобы появление "1" на пятом выходе блока выдачи результата совпало с началом возможного импульса на четвертом выходетого же блока.Блок 26 выбора данных включается синхроимпульсом, подаваемым наего третий вход, где параллельно сним на первый и второй вход этогоблока подаются соответственно кодыА, и В которые запоминаются в З 5 регистрах 45, 50, а также, пройдячерез элементы ИЛИ 46, 47 и элементИ 49, на выходе последнего формирует импульс, если коды А; и В, неравны нулю. Параллельно с этим синхроимпульс, задержанный элементом48 задержки на время, большее, чемработа цепи элементов 46, 47 и 49,будет подан на второй вход ключа57. Если на первый вход ключа 57 был 45 подан импульс, то синхроимпульс выйдет через прямой выход ключа 51,иначе - через элемент .ИЛИ 55 начетвертый выход блока 26 выбора данных в качестве запроса на началоследующего шага цикла 26 по . Еслисинхроимпульс вьппел с прямого выходаключа 51, при этом сам ключ черезвремя задержки не менее длительности синхроимпульса, обеспеченной эле ментом 116 задержки, вернет ключ висходное состояние ("обнулит триггер 117), то синхроимпульсы считаюткод А, из регистра 45 и через пятый79937 12 55 11 14 выход блока 26 выбора данных код Б из регистра 6 блока 1 памяти. Затем код А, и синхроимпульс, с одной стороны, через седьмой и пятый выходы блока 26 выбора данных поступят в блок 25 аналогии, с другой стороны, код А, совместно с кодом Б, который также поступает в блок 26 аналогии, поступят на блок 52 сравнения с инверсным входом, который выдаст импульс, если код А, не содержит код Б, на первый вход ключа 54, а синхроимпульс задержанный элементом 53 задержки на время не меньше, чем время срабатывания блока 52, пройдет через ключ 54 на его прямой выход как забраковаВший" данные и поступит через элемент ИЛИ 55 на четвертый выход блока 26 выбора данных, Если код А; содержит код Б, то синхроимпульс выйдет с инверсного выхода ключа 54, откроет ключи 56, 57 и вызовет считывание кода В из регистра 50, что вызовет одновременное появление синхроимпульса на третьем выходе кодов А Б, В; соответственно на первом,втором и шестом выходах блока 26 выбора данных.Блок 25 аналогии включается синхроимпульсом, поступающим на четвертый вход блока аналогии. До появления синхроимпульса на второй вход блока 25 аналогии бып подан код В;, который запомнился на ключе 61. Практически одновременно с синхроимпульсом на первый и третий входы блока 25 аналогии поступают коды А1 и Б, которые попадают на входы блока 58 сравнения с инверсным входом, который, если код Б не содержит код А , выдаст на свой выход импульс, который заблокирует прохождение синхроимпульса, задержанного элементом 59 задержки до времени завершения работы блока 58, на инверсный выход ключа 60, Если код Б содержит код А, то синхроимпульс с инвесрного вйхода ключа 60, поступив на первый вход блока 62 управления регистром, вызовет считывание содержимого регистра 63 и, поступив на второй вход ключа 61, откроет его. В результате коды В, с ключа 61 и В, из регистра 63 одновременно поступают на блок 64, который осуществляет их побитовое спожение в смысле булевой алгебры, После этого новый код Взапоминается на ключе 65. Парал 5 10 15 20 25 30 35 40 45 50 лельно с этим блок управления регист.ром 63 после завершения операциисчитывания из регистра 63 обнулитрегистр 63 и после завершения обнуле 1 ния одновременно выдаст импульс записи в регистр 63 и откроет ключ65, в результате чего в регистре 63запомнится новый код ,ЕВ . Для случая,если по методам сходства и различиявозникло противоречие, синхроимпульспосле элемента 59 задержки поступитна второй выход блока 25 аналогии,где может использоваться как признак конца работы блока 25 аналогии,т,к.-задержка в блоке 4 синхронизации в элементе 44 задержки достаточна для атактического завершенияработы блока 25 аналогии. Пятый входблока 25 аналогии используется блоком выдачи результата. При подаче" 1" на этот выход "1" поступает навторой вход блока 62 управления регистром и проходит только черезпервый выход блока 62 на третий (чтение) вход регистра 63, что вызываетпостоянную выцачу содержимого регистра на первыи выход блока 25 аналогии, причем этот же код, поступив через блок 64 на ключ 63, будет постоянно заблокирован, т.е, не пропущендалее, Блок 29 сходства включается подачей на его третий вход синхроимпульса, Одновременно с этим напервый и второй входы блока 29 сходства поступают коды В и А соответ 1 1ственно и запоминаются на ключах68, 69,Синхроимпульс, поступая на первыйвход блока 70 управления регистроми второй вход ключа 69, вызывает подачу кодов А и РАна входы блока172 логического умножения, где онипоразрядно умножаются и новый кодРА; запоминается на ключе 73, откудапод управлением блока 70 последнийзаписывается в ранее обнуленный регистр 1 произведения ситуаций. Синхроимпульс, задержанный элементомбб задержки, откроет ключ 68 и, поступив на первый вход блока 74 управления регистром, вызовет чтение кодаРВ, из регистра 75, в результатечего коды РВ, и В; одновременно поступят на два входа блока 76 сравнения, С второго, выхода схемы 76сравнения после этого код нового РВ; запомнится на ключе 78, откуда под управлением блока 74 он запомнитсяв предварительно обнуленном регист-ре 75 посылок, С первого выхода бло ка 76 сравнения на первый вход ключа 77 поступит импульс (если новый1 код РВ, отличен от нуля), иначе синхроимпульс, задержанный до времени возможного прихода импульса на первый ключ 77, поступив на второй вход ключа 77, выйдет через инверсный выход этого ключа на второй выход блока 29 сходства и будет интерпретирован как сигнал о возникновении противоречия по месту сходства, Если блок 76 сравнения . выдаст импульс на первый вход ключа 77, а это будет, если новый код РВ отличен от О, то синхроимпульс выйдет с прямого выхода ключа 77, вернув ключ 77 в исходное .состояние,на третий выход блока 29 сходства, указывая на конец шага прогнозаметодом сходства.Четвертый вход блока 29 сходства используется блоком 3 выдачи результата. При подаче постоянной "1" на четвертый вход блока 29 сходства через вторые входы блоков 70 управления регистра первые выходы этих бло ков и третьи входы (чтения) регистра 71 произведений ситуаций и регистра 75 посылок постоянно выдается содержимое регистра 71, 4 на первый и, соответственно, четвертый выходы блока 29 сходства.Блок 30 различия включается синхроимпульсом, поступающим на его шестой вход. Одновременно с ним на второй, третий, четвертый входы блока 30 различия поступают соответственно коды А и Б, при этом в блоке 79 логического вычитания вычисляется Ь, = А; О Б, который запоминается в регистре 80, а код В;запоминается в регистре 81, т.к, на вторые входы (запись с предварительной чисткой) регистров 80, 81 подается синхроимпульс, который также через элемент ИЛИ 85 элемент 100 ИЛИ и элемент 101 задержки поступает на второй выход блока 30 различия, Этот импульс интерпретируется как запрос на организацию шага по 1 просмотра памяти. После попадания этого импульса на пятый вход блока памяти 1 коды очередных А, В и импульса,их сопровождающего поступят на первый, пятый и соответственно седьмой входы блока 30 различия. Код В запоминается временно на ключе 88,а код А совместно с только чтосчитанным кодом Ь из регистра 80поступае; на блок 83 проверки, который в случае совпадения этих кодоввыдает импульс на первый вход ключа84. Синхроимпульс с седьмого входа блока 30 различия, помимо считывания регистра 80, также задержанный в элементе 82 задержки до времени срабатывания блока 83, поступит на второй вход ключа 84, выйдет через инверсный выход этого ключа, если коды А и Б; неравны, и через элементы ИЛИ 85, 100 и элемент 101 задержки явится запросом на началом следующего шага цикла по 1, причем, поступив на первый вход ключа 86, он заблокирует собственное прохождение через этот ключ по линии элемента ИЛИ 89 и элемента 92 задержки. Если коды А и Б, совпадут, то синхроимпульс выйдет с прямого выхода клю ча 84, через элемент ИЛИ 89, элемент задержки 92, пройдет через ключ 86 на его инверсный выход и поступит на третий (считывание) вход регистра 81 и второй вход ключа 88, что вызовет одновременное появление кодов В и В на прямом и инверсных входах блока 90 и на инверсном и прямом входах блока 91 сравнения с инверсным входом. В блоке 90 логического вычитания происходит опелрация В; Я В = В;, где Ввременно запоминается на ключе 93, а в блоке 91 сравнения с инверсным входом проверяется правомерность.вычис-.ления Вд, т. е, содержит ли код В, код В, если код В, не содержит код В, то синхроимпульс, задержанный элементом 87 задержки на время срабатывания блока 91, поступив на второй ключ 94, выйдет через прямой выход 45этого ключа и через элементы ИЛИ 85, 100 и задержки 101 поступит на второй выход блока различия как запрос на следующие ходы А и В, иначе синхроимпульс выйдет с инверсного входа ключа 94, открыв ключ 93, и через блок 95 управления регистра считает код РВ; из регистра 102, в результате чего коды В; и РВ, попав в блок 96 сравнения, поразряд но умножаются, новое произведениечерез ключ 98 запишется в обнулен" ный регистр 102 посылок, а также в блоке 96 сравнения новый код РВ5 14799 сравнивается с 0 и если не равен ему, то блок 96 выдаст импульс на первый вход ключа 99, что вызовет появление синхроимпульса, задержанного элементом 97 задержки и поданного на второй вход ключа 99, с прямого выхода ключа 99, который через элемент ИЛИ 100 и элемент 101 задержки поступит на второй выход блока 30 различия н качестве запроса на следующие А и В, иначе синхроимпульс с инверсного выхода ключа 99 поступит на третий выход блока 30 различия как сигнал о возникновении противоречия по методу различия. Конец цикла по 1 определяет блок 1 памятиВосьмой вход блока 30 различия используется блоком 3 выдачи результата. При подаче на этот вход постоянной "1" через второй вход блока 95 управления регистром и первый выход этой схемы и третий (считывание) вход регистра 102 посылок открывает выход регистра 102 и код РВ поступает на первый выход блока 30 различия.Блок 31 конца цикла выдает импульс, свидетельствующий о конце шага цикла прогноза пометодами сходства и различия с второго своего выхода или постоянную "1" с первого своего выхода как свидетельство о противоречии при прогнозе методами и сходства, и различия, Для этого он имеет две линии (одна для сходства, другая для различия), которые запоминают импульсы об окончании шага цикла по 1 соответствующими методами или о возникновении противоречий, Так, триггеры 103, 105 отслеживают приход импульсов конца шага цикла по 1 с блоков 29 сходства и 30 различия. По приходу последнего благодаря элементам ИЛИ 108, 109 и элементу И 110 на выход два блока 3 1 конца цикла поступает импульс, длина которого определяется элементом 111 задержки. Если.возникло противоречие по сходству, то с прямого выхода триггера 104 на третий ныход блока конца цикла постоянно подается "1", которая также воспринимается как факт того, что шаг цикла пов блоке 29 сходства постоянно завершен благодаря передаче этой же "1" через элемент ИЛИ 108 на первый вход элемента И 10253035аоа 55055 37 6110. Аналогично обрабатывается ситуация противоречие по различиютриггером 106 с выдачей " 1" на чет-вертый выход блока 31 конца цикла ичерез элемент ИЛИ 09 на,второй входэлемента И 11 О. Таким образом, еслипротиворечие возникло при работе либо блока 29 сходства, либо блока30 различия, то импульс конца шагацикла поблок 31 конца цикла формирует по сигналу о конце шага цикла по 1 блока, в котором противоречия не возниклоЕсли противоречиевозникло в обоих блоках 29, 30, тоблок-.31 конца цикла выдает постоян 1но 1 с первого, третьего и четвертого своих выходов, чем блокируетимпульсы на свои входы.Ключ первого типа (фиг.11) содержит группу триггеров112, на которой запоминается код, поданный напервый вход этого ключа на время продолжительностью 4 длины синхроимпульса благодаря элементу ИЛИ 113 иэлементу 114 задержки. После истечения этого времени с момента подачикода на первый вход ключа триггерыобнуляются, Считывание информацииосуществляется подачей импульса навторой вход ключа, который пройдетчерез те же элементы И 115,на которые с триггеров 112 подавались "1",Ключи второго и третьего типов,(фиг,12, 13) служат для пропусканиясинхроимпульсов по двум различнымнаправлениям н зависимости от условия, причем после прохождениясинхроимпульсов он всегда подаетсяна вторые входы этих ключей, а импульс условия - на первые триггеры 117, 120, всегда возвращаются всостояние, когда "1" считынаетсяс их инверсных выходов,Блок сравнения (фиг. 14) производит поразрядное (в смысле булевой алгебры) умножение двух кодовс выдачей результата произведенияна второй выход схемы сравнения, исравнение полученного кода произведения с 0 так, что если код не равен О, то с первого выхода схемысравнения снимается "1".Блок сравнения с инверсным выходом (фиг, 15) организует побитовуюобработку двух кодов,Блок логического умножения

СмотретьЗаявка

4247116, 18.05.1987

ВОЙСКОВАЯ ЧАСТЬ 11284

СОХА ВАДИМ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 15/18

Метки: логического, прогнозирования, событий

Опубликовано: 15.05.1989

Код ссылки

<a href="https://patents.su/18-1479937-ustrojjstvo-dlya-logicheskogo-prognozirovaniya-sobytijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для логического прогнозирования событий</a>

Предыдущий патент: Способ обнаружения столкновений в линии цифровой связи с коллективным доступом и адаптер для его осуществления

Следующий патент: Устройство для моделирования систем массового обслуживания

Случайный патент: Погрузочно-транспортная машина