Преобразователь двоичного кода смешанных чисел в двоично десятичный код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 714391

Автор: Розов

Текст

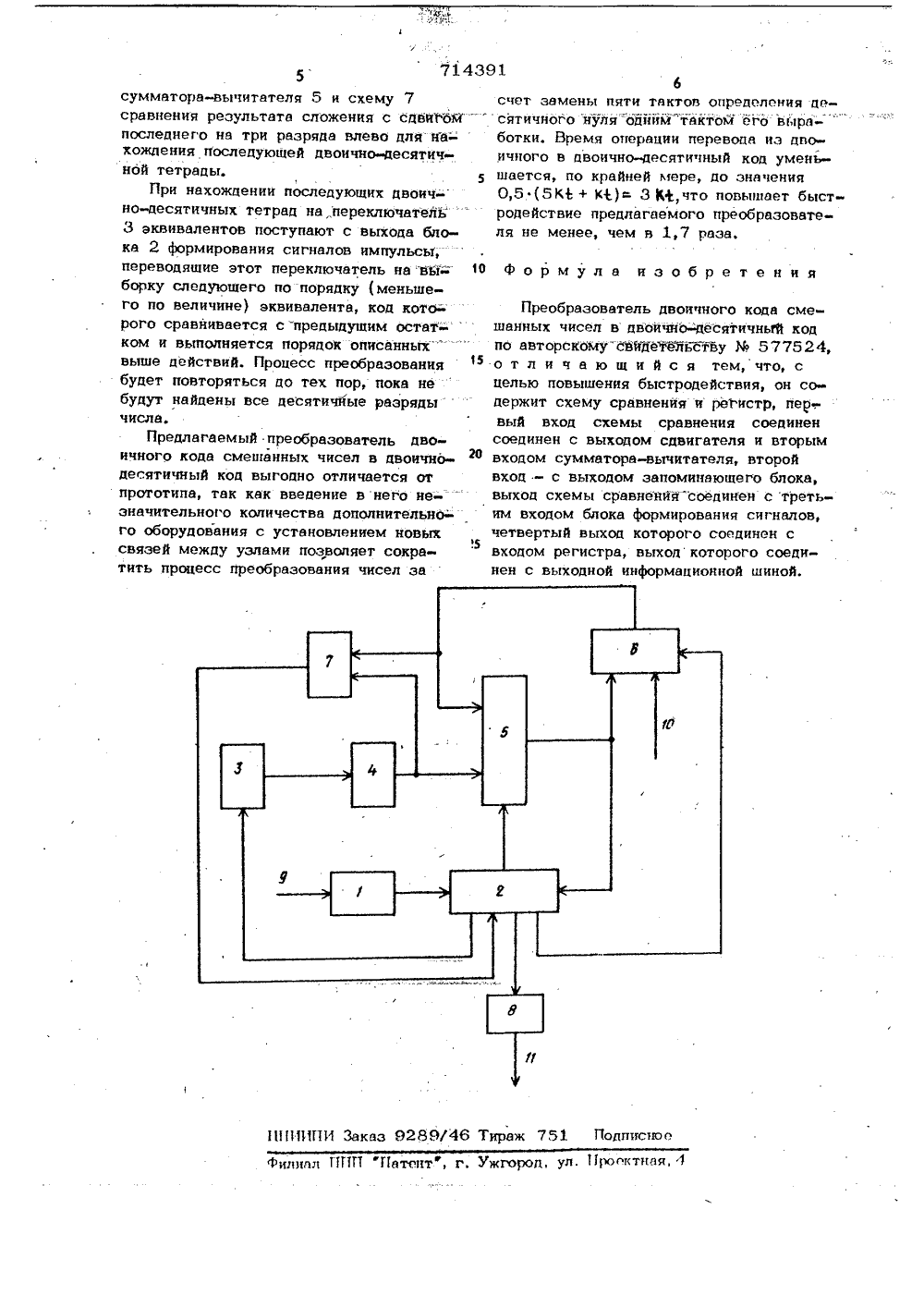

"5 И.; Т Е Й"ИЯ,СВИДЕТЕЛЬСТВУ 71439 Союэ СоветскихСоциалистическихРеспублик ОП ИЗО н еткрытвй АВТОР У(088.8) юллетек Дата писания 08 Авторобретен В. Н. Розо) Заявител ПРЕОБРАОВАТЕ СМЕШАННЫХ ЧДЕСЯТИЧ ЛЬ ДВОИЧНОЮ КОДАСЕЛ В ДВОИЧНО 1 Й КОД му коду, Поэтдесятичной тетбом как и осттак как пониж рройства.Недостатком преобразователя является низкое быстродействие.Целью изобретения является повышение быстродействия,Цель изобретения достигается тем,что преобразователь содержит схему сравпения и регистр, первый вход схемы сравнения соединен с выходом сдвигателя ивторым входом сумматора - вычитателя,второй вход - с выходом запоминающегоблока, выход схемы сравнения соединенс третьим входом блока формированиясигналов, четвертый выход которого соединен с входом регистра, выход которогосоединен с выходной информационной шиной. Изобретение относится к области вычислительной техникн и автоматики и может быть использовано в специализирован ных арифметических и логических устройствах, оперирующих в двоичной системе счисления и выдающих результат обработки информации для восприятия в десятичной системе.Известен преобразователь двоичного кода. смешанных чисел, в двоично-деся тичный код по авт. св. % 577524. Операция перевода из двоичного кода в двоично-десятичный может быть осуществлена в этом преобразователе за время 5 КФ и состоит из четырех основных и одного , дополнительного такта при нахождении каждой десятичной цифры, При этом для выдачи двоично-десятичной тетрады десятичного нуля требуется такое же коли чество тактов. Для восприятия же Выходной информации в конкретном щеобразователе используется определенное количество десятичных разрядов, соответствующее максимальному обрабатываемоВому формирование двоичнорады нуля таким же спосоальных цифр нерационально, ается быст одействие устНа чертеже представлена структурнаяема преобразователя двоичного каца37143смешанных чисел в двоично-десятичныйкод.Преобразователь двоичного кода смешанных чисел в двоично-десятичный кодсодержит блок 1 управления, блок 2 фор 5мирования сигналов, переключатель 3эквивалентов, запоминающий блок 4, сумматор-вычитатель 5, сдвигатель 6, схе му 7 сравнения, регистр 8, вход 9, накоторый подается управляюший импульс, 10вход 10, на который подается двоичныйкод и выходная информационная шина 11,Работает преобразователь следующимобразом.Управляющий импульс поступает на 15вход 9 блока 1 управления,который выФрабатывает импульсы, необходимые для ,.автономного функционирования преобразователя. Запоминающий блок 4, содержитдвоичные эквиваленты десятичных чисел 2010 п, 2 ,1 ., где п =1, 2, 3(К), К: Количество двоичных эквивалентов определяется принятой разряд,ностью десятичных чисел. Преобразованиеосуществляется методом деления переводимого числа (а в дальнейшем остатков)без восстановления остатка на свой двоичный эквивалент при нахождении каждойдвоично-десятичной тетрады, соответствующей десятичной цифре, отличной от .нуля, Если определяемая тетрада соответствует десятичному нулю, то делениена данный эквивалент не производится,Выбор соответствующего эквивалента задается переключателем 3 эквивалентов,которыч управляется блоком 2 формирования сигналов.Управляющие импульсы с выхода бло ка 2 формирования сигналов,пройдячерез переключатель 3 эквивалентов, воз 40буждают в запоминающем блоке 4 шинусоответствующего эквивалента (в началепреобразования - старшего, т. е. М = 1),двоичный параллельный код которого наступает на вход сумматора-вычитателя5, а также с сдвигомна три разрядавправо (за направление фвправо" принятонаправление от старших разрядов к младшим) на вход схемы 7 сравнения. Одновременно на другой вход сумматора-вы- ф 0читателя 5 и схемы 7 сравнения подает-.ся в начале преобразования-через сдвигатель 6 от входа 10 переводимое числобез сдвига двоичного кода, В схеме 7, 55сравнения двоичный код переводимого" чйсла"сг 15 авййвается "с двойчйьй 0 ГкЩбмэквивалента 110 "ф. 25( 13 ., Еслипереводимое число больше значения 91410 ф", 25("-:, то схема 7 сраврпения вырабатывает сигнал, по которому блок 2 формирования сигнала, формирую щий серию управляющих импульсов, .разрешает в первом такте преобразованиявычитание кода эквивалента, который служит делителем, из переводимого числа, являющегося делимым, в сумматоревычитателе 5, откуда на вход сдвигателя 6 поступает код полученного частичного остатка, знаковый разряд которого поступает также в блок 2 формирования сигналов, где формируется код двоичнодесятичной тетрады и определяется необходимость вычитания или сложения в следующем такте преобразования, При этом, если по анализу знакового разряда сумматоре-вычитателя 5 частичный остаток оказался отрицательным, блок 2 формирования сигналов выдает в регистр 8 в виде очередной цифры двоично-десятичной тетрады нуль и подготавливает в сумматоре-вычитателе 5 цепи сложения для следующего такта преобразования, а если частичный остаток получается положительным, то в регистр 8 выдается единица, а в следующем такте производится вычитание делителя из делимого.В качестве делимого в последующих тактах.определения данной двоично-десятичной тетрады берется предыдуший частичный остаток, код которого поступает с сдвигом на один разряд влево ( за направление "влево" принято направление от младших разрядов к старшим) на вход сумматора-вычитателя 5 и схему 7 сравнения от.сдвигателя 6, делитель остается прежним. После нахождения всех цифр двойчно-десятичной тетрады, т. е. выполнения четырех тактов, в пятом такте производится, если частичный остаток оказался отрицательным, восстановление положительного остатка путем прибавления в сумматоре-вычитателе 5 того же делителя к отрицательному остатку под воздействием управляющих импульсов блока 9 формирования сигналов.Если переводимое число меньше значения,10 и . 2(щ " , то. схема 7 сравнения вырабатывает сигнал, по которому блок 2 формирования сигналов выдает параллельным кодом нулевое значение данной тетрады в регистр 8. Одновременно блок 2 формирования сигналов разрешает сложение кода переводимого числа с нулевым кодом в качестве второго слагаемого в сумматоре-вычитателе 5 и подготавливает передачу на вход714391 ИИИПИ За 9289/46 751 Лодписно ПП Патентф, г. Ужгород, ук. 1 Грооктная, 4 5сумматора-вычитателя 5 и схему 7 сравнения результата сложения с сдвигом последнего на три разряда влево для на- хождения последующей двоично-десятичной тетрады.5При нахождении последующих двоич- но-десятичных тетрад напереключатель3 эквивалентов поступают с выхода блока 2 формирования сигналов импульсы, переводящие этот переключатель на вы-" борку следующего по порядку (меньшего по величине) эквивалента, код кото- рого сравнивается с предыдущим остат-"ком и выполняется порядок описанныхвыше действий. Процесс преобразования будет повторяться до тех пор, пока не будут найдены все десятичные Разряды числа.Предлагаемый преобразователь двоичного кода смешанных чисел в цвоично- О десятичный код выгодно отличается от прототипа, так как введение в него не- " значительного количества дополнительнО- го оборудования с установлением новых связей между узлами позволяет сокра 5 тить процесс преобразования чисел за 6счет замены пяти тактов определения десятичного нуля одйймтактомеговыра- " ботки. Время операции перевода из двоичного в двоично-десятичный код уменьшается, по крайней мере, до значения 0,5(5 К 1 + И)3 Щ,что повьпцает быстродействие предлагаемого преобразователя не менее, чем в 1,7 раза,формула изобретения Преобразователь двоичного кода смешанных чисел в двоична-десятичный код по авторскому" сййдетельству Я 577524, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, он со держит схему сравненйя и ре 1.истр, пер-. вый вход схемы сравнения соединен соединен с выходом сдвигателя и вторым входом сумматора-вычитателя, второй вход - с выходом запоминающего блока, выход схемы сравненйя"соединен с третьим входом блока формирования сигналов, четвертый выход которого соединен с входом регистра, выход которого соединен с выходной информационной шиной.

СмотретьЗаявка

2311508, 08.01.1976

ПРЕДПРИЯТИЕ ПЯ А-1178

РОЗОВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоично, двоичного, десятичный, код, кода, смешанных, чисел

Опубликовано: 05.02.1980

Код ссылки

<a href="https://patents.su/3-714391-preobrazovatel-dvoichnogo-koda-smeshannykh-chisel-v-dvoichno-desyatichnyjj-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь двоичного кода смешанных чисел в двоично десятичный код</a>

Предыдущий патент: Устройство для отображения информации

Следующий патент: Преобразователь двоичного кода в позиционный код другого основания с масштабированием

Случайный патент: Устройство для уборки негабарита с откоса уступа