Система контроля логических схем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 710045

Авторы: Киселюс, Мецаев, Стаскявичюс

Текст

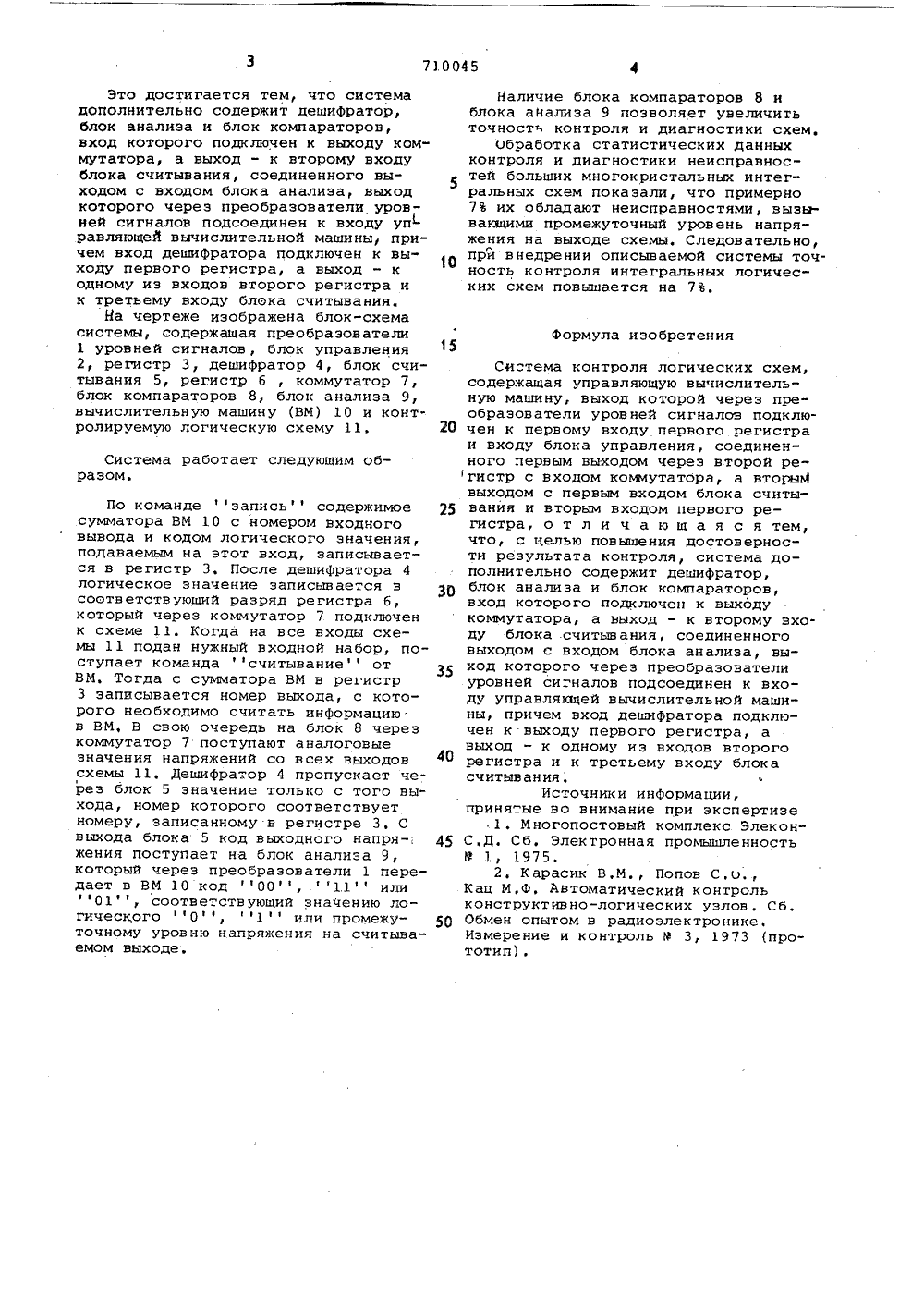

,.д , ,.Г,ъатЬММм 1 те; О П И С А"Я"ИЕ ЙЗОБРЕТЕБИЯ Союз Соеетскик Социалистических Республик(51) М ( 2 с присоединением заявки Мо С 06 Г 15/46 С 05 В 23/00 Государственный комитет СССР по делам изобретений и открытий(088,8) Опубликовано 15.01.80. Бюллетень Ио 2 Дата опубликования описания 18.01.80(71) Заявитель Каунасский политехнический институт им,Антанаса Снечкуса(54) СИСТЕМА КОНТРОЛЯ ЛОГИ 1 ЕСКИХ СХЕМИзобретение относится к контрольно-измерительной технике, в частности к. технике контроля и диагностикилогических схем.Известны промышленные контрольноизмерительные устройства, позволяющие измерять статические и динамические параметры логических схем 111,Одно иэ таких устройств содержит пре-образователи уровней, блок управления, регистр записи, дешифратор, коммутационный регистр и управляется отмини ЭВМ, Команды от ЭВМ через преобразователи уровней поступают наблок. управления, который управляеткоммутационным регистром и обменоминформации между ЭВМ и устройством.Данные иэ ЭВМ поступают в регистрзаписи и через дешифратор записыва ются в коммутационный регистр,Однако контрольно-измерительноеустройство данного типа не приспособлено для диагностики неисправностей в логических схемах иэ-за механических переключателей, через которые подаются напряжения на логические схемы, что в свою очередь непозволяет диагнозировать логическиесхемы с памятью, а кроме того, резко снижает скорость испытаний. Указанные недостатки устранены в специализированных контрольно-диагностических устройствах, имеющих электронные ключи вместо механических анаиболее близким техническим решением к изобретению является система контроля логических схем, содержащая управляющую вычислительную машину, выход которой ч ере э преобразователи уровней сигналов подключен к первому входу первого регистра и входу блока управления, соединенного первым выходом через второй регистр с входом коммутатора, а вторым выходом с первым входом блока считывания и вторым входом первого регистра 1 21, В этой системе не предусмотрена возможность контроля и диагностики логических схем с неисправностями, вызывающими промежуточный уровень напряжения на выходе испытываемой схемы между логическими 0 и 1 ,При наличии таких неисправнос - тей система с вероятностью 0,5 не обнаруживает их, следовательно, результаты контроля и диагностики получаются недостоверными и неточными.Цель изобретения - повышение достоверности результатов контроля.25 ЗО 35 Это достигается тем, что система дополнительно содержит дешифратор, блок анализа и блок компараторов, вход которого подключен к выходу коммутатора, а выход - к второму входу блока считывания, соединенного выходом с входом блока анализа, выход которого через преобразователи уровней сигналов подсоединен к входу уп" равляющей вычислительной машины, причем вход дешифратора подключен к выходу первого регистра, а выход - к одному иэ входов второго регистра и к третьему входу блока считывания.На чертеже изображена блок-схема системы, содержащая преобразователи 1 уровней сигналов, блок управления 2, регистр 3, дешифратор 4, блок считывания 5, регистр б , коммутатор 7, блок компараторов 8, блок анализа 9, вычислительную машину (ВМ) 10 и контролируемую логическую схему 11. Система работает следующим образом. По командезаписьсодержимое сумматора ВМ 10 с номером входного вывода и кодом логического значения, подаваемым на этот вход, записывается в регистр 3. После дешифратора 4 логическое значение записывается в соответствующий разряд регистра б, который через коммутатор 7 подключен к схеме 11. Когда на все входы схемы 11 подан нужный входной набор, поступает команда считывание от ВМ, Тогда с сумматора ВМ в регистр 3 записывается номер выхода, с которого необходимо считать информацию в ВМ, В свою очередь на блок 8 через коммутатор 7 поступают аналоговые значения напряжений со всех выходов схемы 11, Дешифратор 4 пропускает через блок 5 значение только с того выхода, номер которого соответствует номеру, записанному в регистре 3. С выхода блока 5 код выходного напря-: жения поступает на блок анализа 9, который через преобразователи 1 передает в ВМ 10 код фф 00 фф, фф 11 ф или 01 ф, соответствующий значению логического 0, 1 или промежуточному уровню напряжения на считываемом выходе. Наличие блока компараторов 8 и блока анализа 9 позволяет увеличить точност контроля и диагностики схем,обработка статистических данных контроля и диагностики неисправностей больших многокристальных интег" ральных схем показали, что примерно 7 их обладают неисправностями, вызывающими промежуточный уровень напряжения на выходе схемы, Следовательно, прй внедрении описываемой системы точность контроля интегральных логических схем повышается на 7. Формула изобретения Система контроля логических схем, содержащая управляющую вычислительную машину, выход которой через преобразователи уровней сигналов подключен к первому входу первого регистра и входу блока управления, соединенного первым выходом через второй регистр с входом коммутатора, а вторым выходом с первым входом блока считывания и вторым входом первого регистра, о т л и ч а ю щ а я с я тем,что, с целью повышения достоверности результата контроля, система дополнительно содержит дешифратор,блок анализа и блок компараторов,вход которого подключен к выходукоммутатора, а выход - к второму входу блока считывания, соединенноговыходом с входом блока анализа, выход которого через преобразователиуровней сигналов подсоединен к входу управлякщей вычислительной машины, причем вход дешифратора подключен к выходу первого регистра, авыход - к одному из входов второгорегистра и к третьему входу блокасчитывания.ФИсточники информации,принятые во внимание при экспертизе1, Многопостовый комплекс ЭлеконС,Д, Сб, Электронная промышленность Р 1, 1975. 2. Карасик В,М Попов С.о Кац М,Ф, Автоматический контроль конструктивно-логических узлов. Сб, Обмен опытом в радиоэлектронике.Измерение и контроль М 3, 1973 (прототип).Юрчикова Техред О,Андрейко Корректор Г,Назаров Редакт сно лиал ППП Патентф, г.ужгород, ул.Проектная, 4 каз 8761/49ЦНИИПИ Госудпо делам113035, Москва,тиражрственногозобретениж, Рауш 51 По комитета СССР и открытийскан нйб., В.

СмотретьЗаявка

2537117, 26.10.1977

КАУНАССКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. АНТАНАСА СНЕЧКУСА

СТАСКЯВИЧЮС АЛДИВИНАС ИОЗО, МЕЦАЕВ ЕВГЕНИЙ АМУРХАНОВИЧ, КИСЕЛЮС ЭЛИГИЮС ИОНО

МПК / Метки

МПК: G06F 11/00

Метки: логических, схем

Опубликовано: 15.01.1980

Код ссылки

<a href="https://patents.su/3-710045-sistema-kontrolya-logicheskikh-skhem.html" target="_blank" rel="follow" title="База патентов СССР">Система контроля логических схем</a>

Предыдущий патент: Устройство для решения систем алгебраических уравнений

Следующий патент: Счетная линейка

Случайный патент: Устройство для измерения изгибающих сил и моментов, действующих на вращающий вал