Цифровая интегрирующая система для решения линейных дифференциальных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

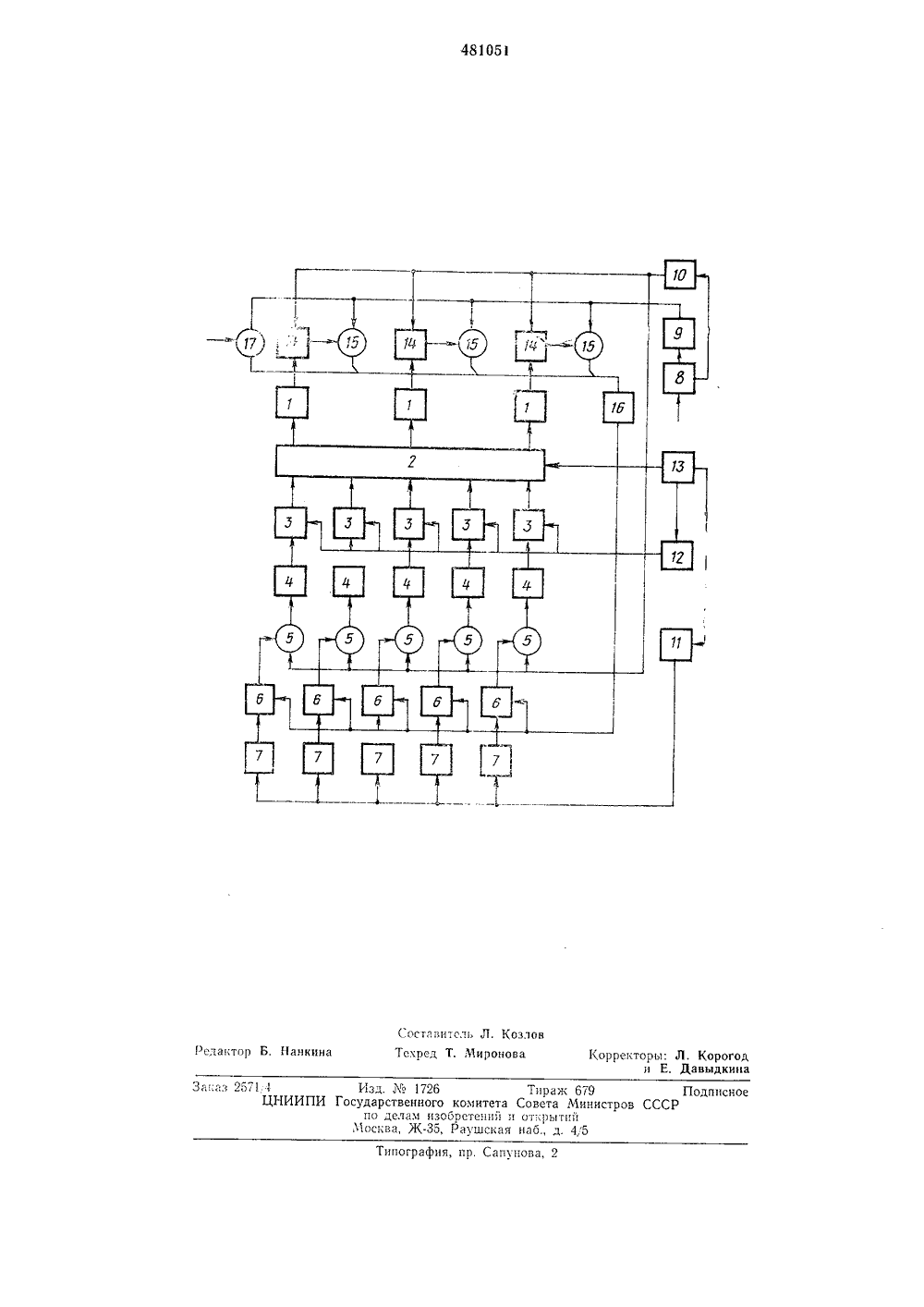

ОП ИСАН И ЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ с) 48 ОЯ Союз Советских Социалистических Республиквт. св ил- ву ополнительное 22) Заявлено 13.03.73 (21) 1893233/18 1) М, Кл. б 061 1/О тЪт заявки Ле рисоединение 23) Приорите осударственный комитет овета Министров СССР) УДК 681.14(088,8 етец М 30 ликовано 15.08.75. делам изобретении писания 29.1 ата опубликован и открыт 2) Авторы изобретени В. П. Боюн и Л. Г. Козлов Ордена Ленина институт кибернетики АН Украинской ССаявител 54) ЦИФРОВАЯ ИНТЕГРИРУЮЩАЯ СИСТЕМА ДЛЯ РЕШЕНИ ЛИНЕЙНЫХ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ2 Изобретение относится к области вычислительнои техники и хтожет быть использовано при построении цифровых интегрирующих машин и устройств для решения систем линейных дисрференциальных уравнений.Известны цифровые интегрирующие системы для решения линейных дифференциальных уравнений, содержащие регистры приращений, устройства умножения, первые входы которых подключены к выходам регистров приращений, коммутатор, информационные входы которого подключены к выходам устроисгв умножения, интеграторы, входы которых подключены к выходам коммутатора, запоминающее устройство коэфсрициенпгов, выход которого соединен со вторыми входамп устроиств умножения, устройство управления, первый выход которого соединен с управляющим входом коммутатора, а второи выход - со входом запоминающего устройства коэффициентов.Известные цифровые интегрирующие системы имеют низкое быстродействие и точность.Целью изобретения является устранение указанных недостатков.Поставленная цель достигается тем, что система содержит счетчик, вход которого подключен к первому входу системы, шифратор, регистры адресов, запоминающее устройство адресов, вход которого подключен к третьему выходу устройства управления, а выход соединен со входом регистров адресов, схемы сравнения адресов, первые входы которых подключены к выходам регистров адресов, а 5 вторые входы - к выходу шифратора, перваягр ппа элементов И, первые входы которых подключены к выходам схем сравнения адресов, а выходы соединены со входами регистров приращений, дешифратор, вход которого) подключен к выходу счетчика, вторая группаэлементов 11, первые входы которы.; подключены к выходу дешпфратора, а выхолы сое;и;нены со входом шисрратора, дополнительный элемент 11, первый вход которого 5 подключен ко второму входу системы, второйвход - к выходу дешифратора, а выход соединен со входом шифратора, схемы сравнения кодов, первые входы которых подключены к ияходам интеграторов, а выходы соединены со вторыми входами элементов И второй группы, и генератор кодов, вход которого подключен к выходу счетчика, а выход соединен со вторыми входами схем сравнения кодов и элементов И первой группы.5 Схема предлагаемой системы изображенапа чертеже и состоит из интеграторов 1, коммутатора 2, устройств умножения 3, регистров приращений 4, элементов И первой группы 5. схем б сравнения адресов, регистров адре- ЗО сов 7, счетчика 8, дешпфратора 9, генераторакодов 10, запопяОнС О; ст)дйсВя 2.ресов 11, за 30 и 32 онего устрдйсБя коэффпц:еп ОБ 12, устройства правленн 5 13, схем 14 сравпеш)я кодов, элементов 11 второй гру:;1 . 10, шифратора 1 б и лополннтель:с о -лс:сита И 17.При помОщи коммутатора 2 ко входам иптеграторов 1 подключается такое количество устрОЙстБ умножения 3, с,Олько пснулсвых коэффициентов содержится в соответствм 0- щем уравнении с стемы, Из за поминаопего устройства коэффнцие тов 12 ня устройс(ва умножения 3 заносятся колы пдс;оя ных коэффициенто 3, 2 на регисты ядресдз 7 из запоминающего устройства адресов 11 в унитарном коде заносятся адреса коэфф;цнен гон, характеризующие связи переменных данного уравнения с переменным остялпьх , )ЯВ:с:ий системы. Генератор колов 10 в.радеть:3 яст последовательно коды в соответствии с прш;ятой системой кодирования, например в случае бп:ярпой системы кодирования генератор колов 10 выдает коды +1 и- 1 последо.32 ельни. В зависимости от кода в счетчике 8. Пя Вход которого поступает Ястота, лешпфрагдр 9 гь- лает последовательно сигналы на первые входы элементов И второй группы 10. Пр:1 сравне:ии кодов, поступающих на первые и вторые входы схем 14 сравнения : одов, открываются соответствуощис элемснп,: И второй группы 15 п шифратор 16 Выдает:а Вторье Входы схем б сряВнени 1 ядгесд 3 кдл номера интегратора 1, импульс перст:олнепия которого соответствует кону, выдаваемому геиератором кодов 10. Этот код заносится ня регистры приращений 4 через элемеш:ы 1".; первои группы О, которые име от связи с соответствующим интегратором 1 для рсиасмо:" системы уряВнениЙ. МякспмальныЙ кд, 13 се. чике 8 соответствует числу инте: ряторов 1, н:) нулевом коде счетчика 8 на вход шифратора 1 б приходит сигнал от дополнительного элемента И 17, на Вход которого поступает приращение независимой переменной, в этом Гл - чае осуществляется ввод прираценни 3. 3, выхода переполений счетчика 8 импульс пд дается на вход генератора кодов 10, который ПЬ.(Г Г.Е.:0:НИ:1 КОЛ. Н 1 ОНЕГС 1 Ы 1:ГЛСд" Г3() 5 ГГ и Г3 "П"3, )1 1 р (Ц:фри:(51 пн.сгрир Ощя Гнете)3 лля;епс: ня л 1;ейных лиффс,)снцияль:1 ых дав:1 еПн, ( ОЛЕР)КЯ На я РЕГИСРЫ ПРИРЯЕ:Пй, МСТирдиства умшжсния первые зхдлы которь хподключены и выходам регистров прирап;е 1 ий, комму-атор, пнформационые Входы котороо подключены и выходам устройств умно)кепи(5,:1:теграто 1 ь:, гхолы которых длключеы к Быхоцям коммутатора, зя;омшаюнсе устронствд коэфф:пентов, выход которо.гд сдс;пиен сд 1 тдрыхп:3 хдля 11 мстр)(с В,ожсння, и устройство уп 1)ялепип, пе)выйВыход которо:д соединен с упрявляюшм вхоЛД)1 100)1)ЛЯТОРЯ, Я БОРО,1 ВЫХОД - СО БХДлом зя:о):паюне: о уст)ойспа коэффинс:1 ТО 3, ОТЛИЧЯ ОН 2 ЯСЯ ТЕМ, ЧТО, С ЦСЛЬЮувеличс Пя ОСтрдл(йствпя 11:103 ынГния тсчп ости, Оп 1 сдлсржи счс. 11 ВхОд кдтдрд. 0пдлклдчен и первому Входу системы, н.Ифрято), регист)ы адресов, запо);няощсе усгрдй 2( с(во адресов, вход которого подключен итрсьсму ьь;оду ус) ро;"ст Бя управления, авыход Го(.Л:. Псн со вхдлсм рсгпстров адресов,СХЕ:Ь СРЯБ ИЯ Я;. (. ГОБ., П( )1 ЫЕ ВХО:Ь1 ЬРЫХ Н( К " 11 1 ЗЬ 1 Д ЧЯРС 1.ГТ(3 013 (ЛРС 3.) соп а втдрь:е зхолы и 131 хдл) и:1 фр;0 ра,первая руп;я эгсмен) св 1, 1:Грвые ВходыКО" О Ь Х ,1(ЛКЛ 10 Р.1 Е ВЫХОДЯ М СХСМ СРЯВПЕНИ 5ЛРССДБ 2 ВЫХОЛЬ СДЕЛИ 1 Е СО БХС 2 Иреп;ст,)св;рнранснпй, лешнфрятд), Бхол ко 5 тордго подключен к выходу Счет н:кя втораягруп:а злеме;тов И, первые вхдлы которыхполилоче:Ь и Быхо;у Лсшифра;ора, . Вь.ходьсоедине;ь: сд входом шнф зато)а лопол:нСль:Б:" элемент И, первй Вхол котсрого4пдд 0110 чс; кд 3(д дмм 3 хдд Гпс:сБ. 13 т 0130.ьхо, и в:холу ленфраторя, а вь;хол сссДнн( ГД ВХДЛОЪ Ыи.ЯТ;),)1, СХЕМЬ С)ЯБ:Е".Якол(з, псршяе Бхолы кого",ьх пдлключс:ы ивыхдла 11:1;тегря гор(53 2 зыхсдь; сосдепы со45 Вт 01)1."1: Бхд;ям 1: э;с.с:тд 3 И: 3 тсрдй 1 р,и.ПЯ Я( СП; ДР :,Д дв ) ДКД) ДПДГД)Л.;ЛДЯ:ЫХД ( СОСИНЕПВ 10 РЬМН .3.;( ",Я.1: Г1 С)ЯВ:1 Е 1151 130,Ов И Э(1(.- .;(.н:д: 1 пс)1;О;"1 .): П 1,481051 Составитспв ЛКОзлОВ едактор Б. Нанкина Текред Т. Миронова Корректоры: Л. Корогод и Е, ДавыдкинаИзд. М 1726дарственного комитета по дедам изооретений осква, Ж, Раушска ПодписноеССР Тираж 679Совета Министрои открытийя наб., д. 475 аказ 2571,1ЦН ПИ Г биография, пр. Сапунова

СмотретьЗаявка

1893233, 13.03.1973

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРАИНСКОЙ ССР

БОЮН ВИТАЛИЙ ПЕТРОВИЧ, КОЗЛОВ ЛЕОНИД ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06J 1/02

Метки: дифференциальных, интегрирующая, линейных, решения, уравнений, цифровая

Опубликовано: 15.08.1975

Код ссылки

<a href="https://patents.su/3-481051-cifrovaya-integriruyushhaya-sistema-dlya-resheniya-linejjnykh-differencialnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Цифровая интегрирующая система для решения линейных дифференциальных уравнений</a>

Предыдущий патент: Вычислительное устройство для индикатора истинного движения судовой радиолокационной станции

Следующий патент: Устройство для интерполяции знакопеременных функций

Случайный патент: Всесоюзная м1тт-1ш: щгл;: г, л1-; л-: т-; . -а i