Сумматор по модулю пять

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1803911

Авторы: Дорожинский, Супрун

Текст

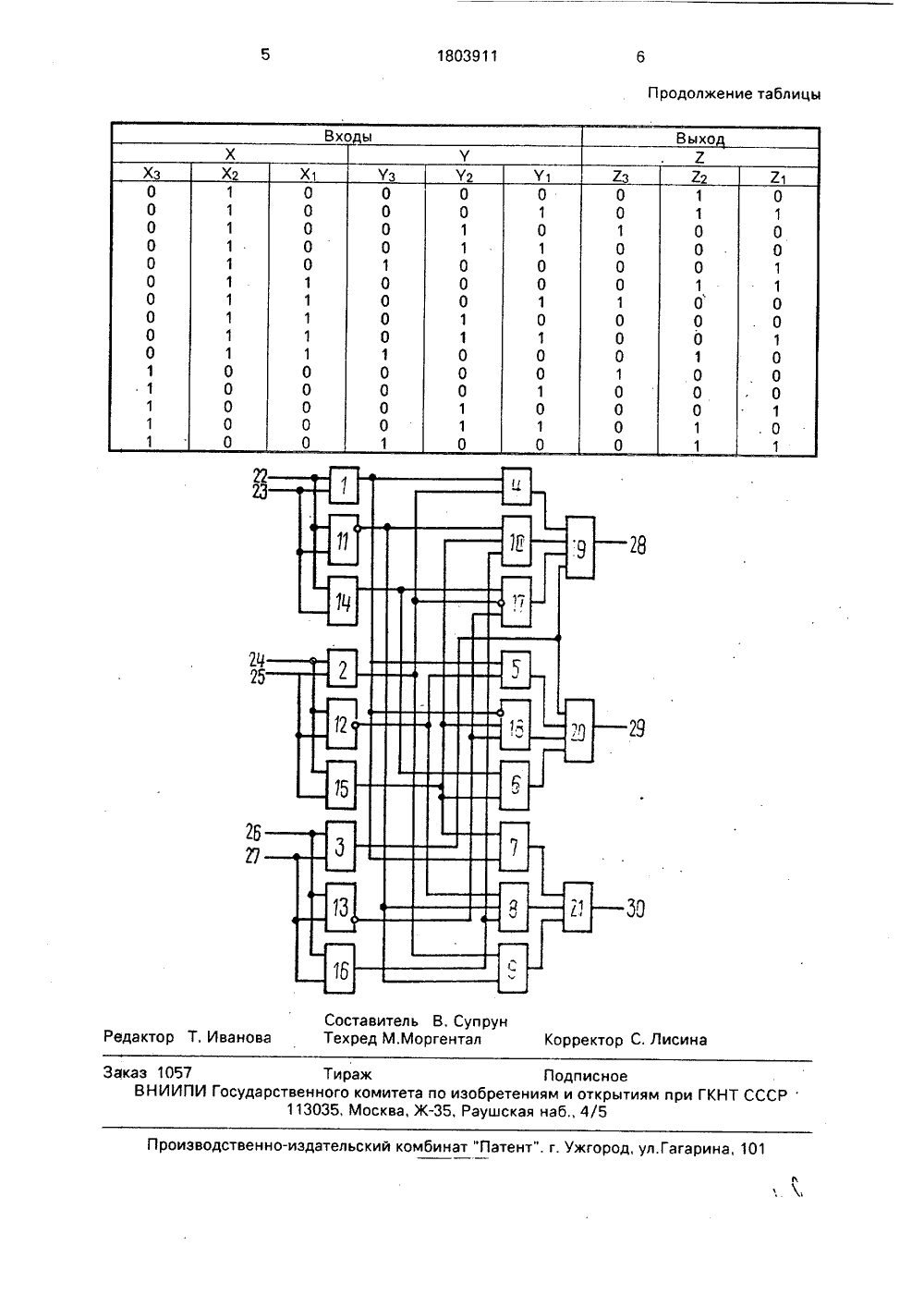

) СУММАТОР ПО МО ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(ГбСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБР АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(21 4917216/24 (22 05.02.91 (46 23,03,93, Бюл, 1 ч. 11 (71 Белорусский государственный универ ситет им. В,И,Ленина (72 В,П,Супрун и А,Л.Дорожинский (56 Авторское свидетельство СССР М 388850, кл, 6 06 Р 7/49, 1986,, Авторское свидетельство СССР М 1566342, кл. 8 06 Р 7/49, 1988. Изобретение, относится к области вычислительной техники и автоматики и можетбыт использовано для построения системпередачи и переработки дискретной информации.Цель изобретения - повышение быстродействия сумматора по модулю пять.На чертеже представлена схема сумматор по модулю пять,Сумматор по модулю пять содержитдесйть элементов И 110, три элементаИЛИ, - НЕ 11, 12 и 13, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, 15 и 16, два элемента ЗАПРЕТА 17 и 18, три элемента ИЛИ 19, 20 и 21,шесть входов 2227 и три выхода 28, 29 и 30.Сумматор работает следующим образом.Суммируемые операнды Х и У задаютсятреХразрядными двоичными кодами Х =+2 У 2+ 4 Уз,(57) Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения систем передачи и переработки дискретной информации, Цель изобретения - повышение быстродействия сумматора, Сумматор по модулю пять содержит десять элементов И 1.10, три элемента ИЛИ-НЕ 11, 12, 13, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, 15, 16, два элемента ЗАПРЕТ 17, 18 и триэлемента ИЛИ 19, 20, 21, соединенные между собой функционально. 1 ил, 1 табл,В соответствии с выбранным модулем Р = 5 каждый операнд может принимать значения 0(000), 1(001), 2010), 3(100) и 4(1 00). Результатом работы сумматора по модулю пять является операнд 2, заданный трехразрядным кодом 2 =2 з 2221, где 2 =21+ 222+ 42 з.На входы 22, 23 подаются значения младших разрядов Х 1, У 1 операндов Х и У соответственно; на входы 24, 25 - значения средних разрядов Х 2, У 2 операндов Х и У соответственно; на входы 26, 27 - значения старших разрядов Хз, Уз операндов Х и У соответственно; на выходе 28 реализуется младший разряд 21, на выходе 29 - средний разряд 22, а на выходе 30 - старший разряд 2 з операнда 2, где 2 = Х+ У (п 1 об 5),Логические функции 21, 22 и 2 з, значения которых представлены в таблице, реализуются сумматором согласно следующим аналитическим выражениям; 21 = А 1 А 2 Ч В 1 С 2 СЗ Ч С 1 А 2 Вз Ч Аз22 = А 1 В 1 Ч А 1 С 2 вз Ч С 1 С 2 Ч Аз,23 = А 1 С 2 Ч В 1 В 2 Сз Ч В 1 А 2, 1803911= 1, 2, 3.Достоинством сумматора по модулюпять является высокое быстродействие. Так,его быстродействие, определяемое глубиной схемы, равное Зт, где т - задержка навентиль, В то время, как быстродействиеустройства-прототипа равно 5 т, Также отметим, что сложность сумматора по числувходов логических элементов меньше, чемсложность устройства-прототипа, и равна51 (сложность прототипа равна 65).Ниже приведена таблица истинностилогических функций 21, 22 и 2 з, реализуемыхсумматором по модулю пять,15 Формула изобретенияСумматор по модулю пять, содержащий десять элементов И, три элемента ИЛИ-НЕ, три элемента ИЛИ и первый элемент ЗА ПРЕТ, причем входы первого, второго и третьего разрядов первого слагаемого сумматора соединены соответственно с первыми входами первого, второго и третьего элементов И, вторые входы которых соединены соответственно с входами первого, второго и третьего разрядов второго слагаемого сумматора, выходы первого и второго элементов ИЛИ - НЕ соединены соответственно с первыми входами четвертого и пя того элементов И, выход четвертого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента ЗАПРЕТ, а выход первого элемента ИЛИ явля ется первым разрядным выходом сумматора, выходы пятого и шестого элементов И соединены с первым и вторым входами второго элемента ИЛИ, выход которого является вторым разрядным выхо дом сумматора, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, в него введены первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и второй эле 5 второго и третьего разрядов первого слагаемого сумматора соединены соответственно с первыми входами первого, второго и третьего элементов ИЛИ - НЕ и с первыми входами первого, второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены соответственно с входами первого, второго и третьего разрядов второго слагаемого сумматора, выход первого элемента И соединен с первым входом десятого элемента И, вторым входом пятого элемента И, входом управления второго элемента ЗАПРЕТ и первым входом седьмого элемента И, выход первого элемента ИЛИ - НЕ соединен с первыми входами восьмого и девятого элементов И, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым информационным входом первого элемента ЗАПРЕТ и первым входом шестого элемента И, выход второго элемента И - с вторыми входами девятого и десятого элементов И и управляющим входом первого элемента ЗАПРЕТ, выход второго элемента ИЛИ - НЕ - с вторым входом восьмого элемента И, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ - с вторыми входами четвертого, шестого и седьмого элементов И и первым информационным входом второго элемента ЗАПРЕТ, выход третьего элемента И соединен с третьими входами первого и второго элементов ИЛИ, выход третьего элемента ИЛИ - НЕ - с вторыми информационными входами первого и второго элементов ЗАПРЕТ, выходтретьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ - с третьими входами четвертого и восьмого элементов И, выход десятого элемента И соединен с четвертым входом первого элемента ИЛИ, выход второго элемента ЗАПРЕТ - с четвертым входом второго элемента ИЛИ, а выходы седьмого, восьмого и девятого элементов И - с первым, вторым и третьим входами третьего элемента ИЛИ, выход которого является третьим разрядным выходом сумматора.1803911 Продолжение таблицы 8 Составитель В, СупрунТехред М,Моргентал ктор Т, Иванов ректор С, Лисин Заказ 1057 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4917216, 05.02.1991

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. ЛЕНИНА

СУПРУН ВАЛЕРИЙ ПАВЛОВИЧ, ДОРОЖИНСКИЙ АЛЕКСАНДР ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/49

Опубликовано: 23.03.1993

Код ссылки

<a href="https://patents.su/3-1803911-summator-po-modulyu-pyat.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор по модулю пять</a>

Предыдущий патент: Устройство отождествления

Следующий патент: Суммирующее устройство

Случайный патент: Устройство для контроля метчика