Цифровой синтезатор синусоидальных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1774462

Автор: Старков

Текст

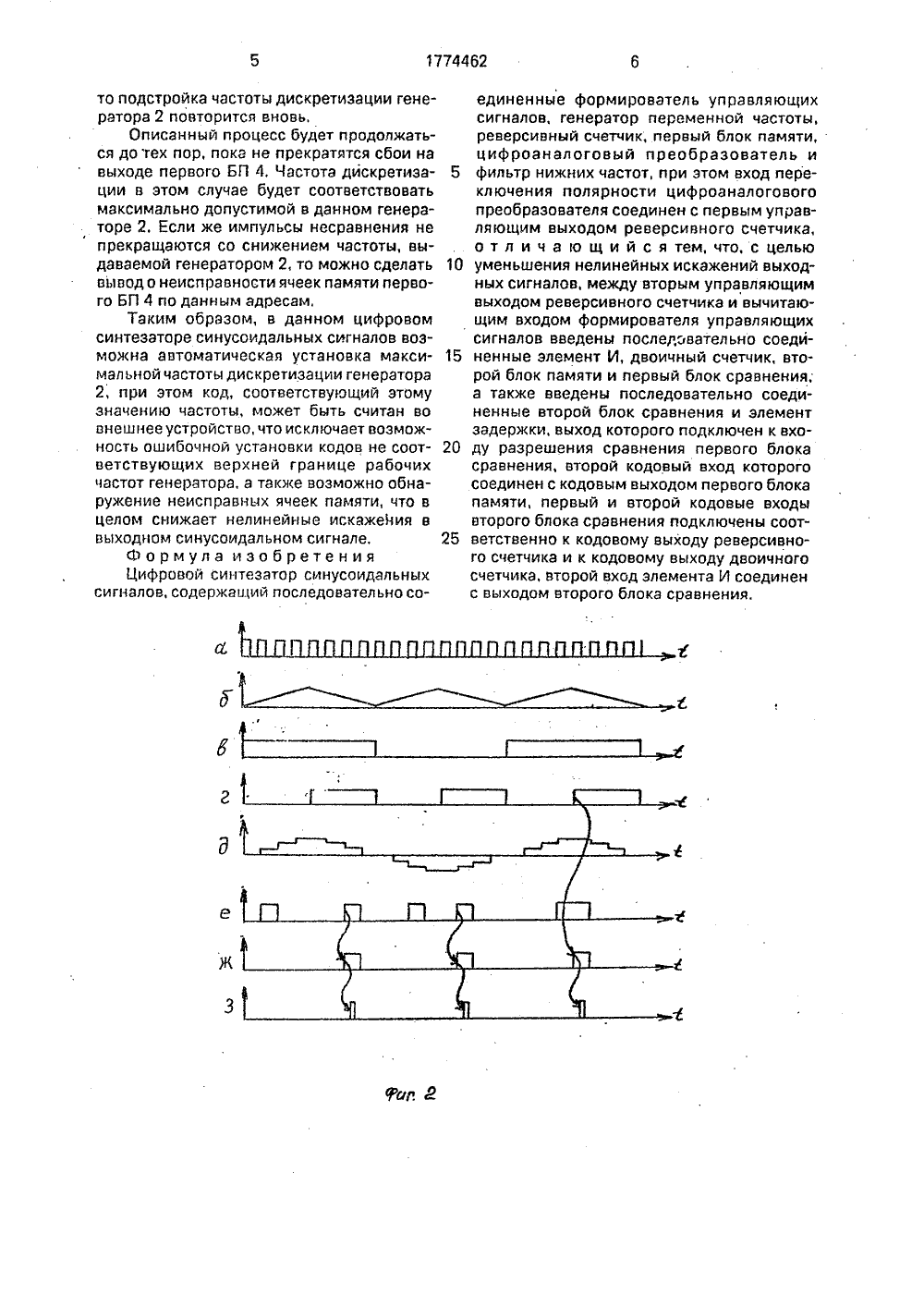

(56) Патенткл. Н 03 1.7/Патент Вкл. НОЗ В 19 Бюл. %41следовател ьск институт ав ковФранции М 2326 00, 8 01 Ч 13/00 еликобритании /00 от 24.09.80. 00,от 03,06,77,М 1575629,. ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(54) ЦИФРОВОЙ СИНТЕЗАТОР СИНУСОИДАЛ Ь Н ЫХ СИГНАЛ О В(57) Изобретение относится к области ради-, отехники. Цель изобретения - уменьшение нелинейных искажений выходных сигналов, Цифровой синтезатор синусоидальных сигналов содержит формирователь 1 управляощих сигналов, генератор 2 переменной частоты, реверсивный счетчик 3, первый блок памяти (БП) 4, цифроаналоговый пре 2образователь (ЦАП) 5, фильтр 6 нижних частот, элемент И 7, двоичный счетчик 8, элемент задержки 9, второй БП 10, первый блок сравнения 11, второй блок сравнения 12, Формирователь 1 управляет тактовой частотой генератора 2, Второи блок сравнения 12 сравнивает коды с выходов реверсивного счетчика 3 и двоичного счетчика 8, а первый блок сравнения 11 сравнивает коды с соответствующих выходов первого и второго БП 4, 10. Поставленная цель достигается тем, что в случае неравенства кодов импульс с выхода первого блока сравнения 11 поступает на вычитающий вход формирователя 1 и уменьшается частота генератора 2. Импульсы несовпадения кодов будут поступать на вход формирователя 1 до тех пор, пока частота дискритизации будет превышать максимально допустимую частоту и имеют место сбои при выборке кодов из первого БП 4. 2 ил.Изобретение относится к области радиотехники и может быть использовано о приемопередающей и радиоизмерительнойаппаратуре.Целью изобретения является уменьшение нелинейных искажений выходных сигналов.Нд фиг. 1 представлена электрическаяструктурная схема цифрового синтезаторасинусаидальных сигналов; на фиг. 2 - временные диаграммы его работы.Цифровой синтезатор синусоиддльныхсигналов содержит формирователь 1 управляющих сигналов, генератор 2 переменнойчастоты, реверсивный счетчик 3, первыйблок памяти ь,БП) 4, цифроаналоговый преобразователь ь,ЦАП) 5, фильтр 6 нижних частот, элемент И 7, двоичный счетчик 8,элемент задержки 9, второй БП 10, первыйблок сравнения 11, отарой блок сравнения12,Цифровой синтезатор синусоиддльныхсигналов работает следующим образом.В формирователь 1, который можетбыть выполнен, например, о виде вычитаьощего двоичного счетчика с параллельнымзаносом информации, заносится код частоты дискретизации тактового генератора 2,Генератор 2 принимает этот код и выдаетимпульсную последовательность соответствующей частоты. Генератор 2 может бытьвыполнен например, в виде последовательно соединенных ЦАП и генератора, управляемого напряжением (ГУН) (ььа фиг. 1 непоказано), и может менять выходную частоту, о зависимости от входного кода, в широком диапазоне, Импульсы с выходагенератора (фиг. 2 а)поступают ца счетныйвход реверсивного счетчика 3 поступает цаадресные входы первого БП 4, в памятикоторого содержатся двоичные кодовыекомбинации, соотоетствующие дискретнымзцаченлям функции синус в первом квадранте, т.е. между фазопььми углами от 01.=.= О до Оь = 90 О, В соответствии с паступаюьдими адресами первый БП 4 в первой итретьей четвертях периода выдает на ЦАП 5двоичные коды значений функции синус отО.= О до Щ = 90, а во второй и четвертойчетвертях периода от О =- 90 до О =- О )фиг, 26) таким образом, ЦАП 5 формируетсинусаидальный сигнал (фиг. 2 д), перекльочение полярности которого осуществляетсяпервым упраоляьощим выходом реверсивного счетчика 3 каждые полпериода о моменты прохождения функции синус через О(фиг, 2 г), Фильтр 6 устраняет нежелательные переходные помехи выходного синусоиддльного сигнала. Одновременно с этим5 10 15 оыходной код реверсивного счетчика 3 поступает на входы первой группы сравнения первого блока сравнения 11, входы второй группы сравнения которой подключены к выходам двоичного счетчика 8. Первый блок сравнения 11 при совпадении кодов на ее входах формирует импугььс равенства (рис.2 з) который поступает на вход элемента задержки 9 и второй вход элемента И 7. Постоянная времени задержки элемента задержки 9 должна быть равна времени задержки выборки кодов из первого БП 4. Коды с выходов которого рис,2 е) сравниваются с кодами на оььходе отораго БП 10, о памяти которой содержатся те же значения функции, пероыи блокам среднеия 11 о момент прихода импульса разрешения сравнения, который поступает с выхода элемента задержки 9, Если сигнал разреше ния сравненля отсутствует или коды, паступающие с выходов первого и второго БП 4 и 10 раоны, то цд выходе первого блока срав-.нения 11 присутствует низкий потенциал, если кодьь не равны, то высокий. Двоичный 25 счетчик 8 при этом находится в статическомсостоянии, Управление его счетом осущестоляетэлемецт И 7, ца первый вход которого . поступает импульс разрешения счета со второго управляющего выхода реверсивно го счетчика 3 при его работе в оычитающемрежиме. Переключение двоичного счетчика 8 происходит по заднему фронту импульса равенства, поступающего с выхода второго блока сравнения 12. Таким образом, если на 35 выходе первого элемент сравнения 11 присутствует нулевой потенциал, то коды, считываемые с первого БП 4 имеют верные значения, если же ца выходе пероого элемента сравнения 11 присутствуют импульсы 40 несраоцеция, то это значит, что или периоддискретизации выбран неверно и период импульсов дискретизации генератора 2 меньше времени выборки кодов из первого БП 4, или па данному адресу в первый БП 4 проис ходит неверное считывание ицформации, Импульсы несравнения, формирующиеся ца выходе первого элемента сравнения 11 поступаьот на вычитающий вход формирователя 1Управляющий код уменьшается на единицу и 50 генератор 2, о соответствии с поступающимкодом, уменьшает частоту дискретизации, По заднему фронту импульса равенства, поступающего с выхода второго элемента сравнения 12 через элемент И 7 двоичный 55 счетчик 8 увеличивает,свае значение на единицу и во время прямого счета рсоерсивнаго. счетчика 3 произойдет сравнение кодовследуьощих ячеек памяти первого и второго 4 и 10. Если коды окажутся снова неравны, 1774462то подстройка частоты дискретизации генератора 2 повторится вновь.Описанный процесс будет продолжаться до тех пор, пока не прекратятся сбои на выходе первого БП 4, Частота дискретизации в этом случае будет соответствовать максимально допустимой в данном генераторе 2. Если же импульсы несравнения не прекращаются со снижением частоты, выдаваемой генератором 2, то можно сделать вывод о неисправности ячеек памяти первого БП 4 по данным адресам,Таким образом, в данном цифровом синтезаторе синусоидальных сигналов возможна автоматическая установка максимальной частоты дискретизации генератора 2, при этом код, соответствующий этому значению частоты, может быть считан во внешнее устройство, что исключает возможность ошибочной установки кодов не соответствующих верхней границе рабочих частот генератора, а также возможно обнаружение неисправных ячеек памяти, что в целом снижает нелинейные искажеНия в выходном синусоидальном сигнале,Формула изобретения Цифровой синтезатор синусоидальных сигналов, содержащий последовательно соединенные формирователь управляющих сигналов, генератор переменной частоты, реверсивный счетчик, первый блок памяти, цифроаналоговый преобразователь и 5 фильтр нижних частот, при этом вход переключения полярности цифроаналогового преобразователя соединен с первым управляющим выходом реверсивного счетчика, о т л и ч а ю щ и й с я тем, что, с целью 10 уменьшения нелинейных искажений выходных сигналов, между вторым управляющим выходом реверсивного счетчика и вычитающим входом формирователя управляющих сигналов введены последовательно соеди ненные элемент И, двоичный счетчик, второй блок памяти и первый блок сравнения; а также введены последовательно соединенные второй блок сравнения и элемент задержки, выход которого подключен к вхо ду разрешения сравнения первого блокасравнения, второй кодовый вход которого соединен с кодовым выходом первого блока памяти, первый и второй кодовые входы второго блока сравнения подключены соот ветственно к кодовому выходу реверсивного счетчика и к кодовому выходу двоичного счетчика, второй вход элемента И соединен с выходом второго блока сравнения.

СмотретьЗаявка

4812115, 05.03.1990

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ АВТОМАТИКИ

СТАРКОВ ВАЛЕРИЙ ГЕННАДЬЕВИЧ

МПК / Метки

МПК: H03B 19/00

Метки: сигналов, синтезатор, синусоидальных, цифровой

Опубликовано: 07.11.1992

Код ссылки

<a href="https://patents.su/3-1774462-cifrovojj-sintezator-sinusoidalnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой синтезатор синусоидальных сигналов</a>

Предыдущий патент: Устройство для подавления остаточных колебаний в резонансной цепи

Следующий патент: Цифровой синтезатор частот

Случайный патент: Горизонтальный отстойник