Устройство для формирования пакетных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1684916

Авторы: Ротенштейн, Цизин

Текст

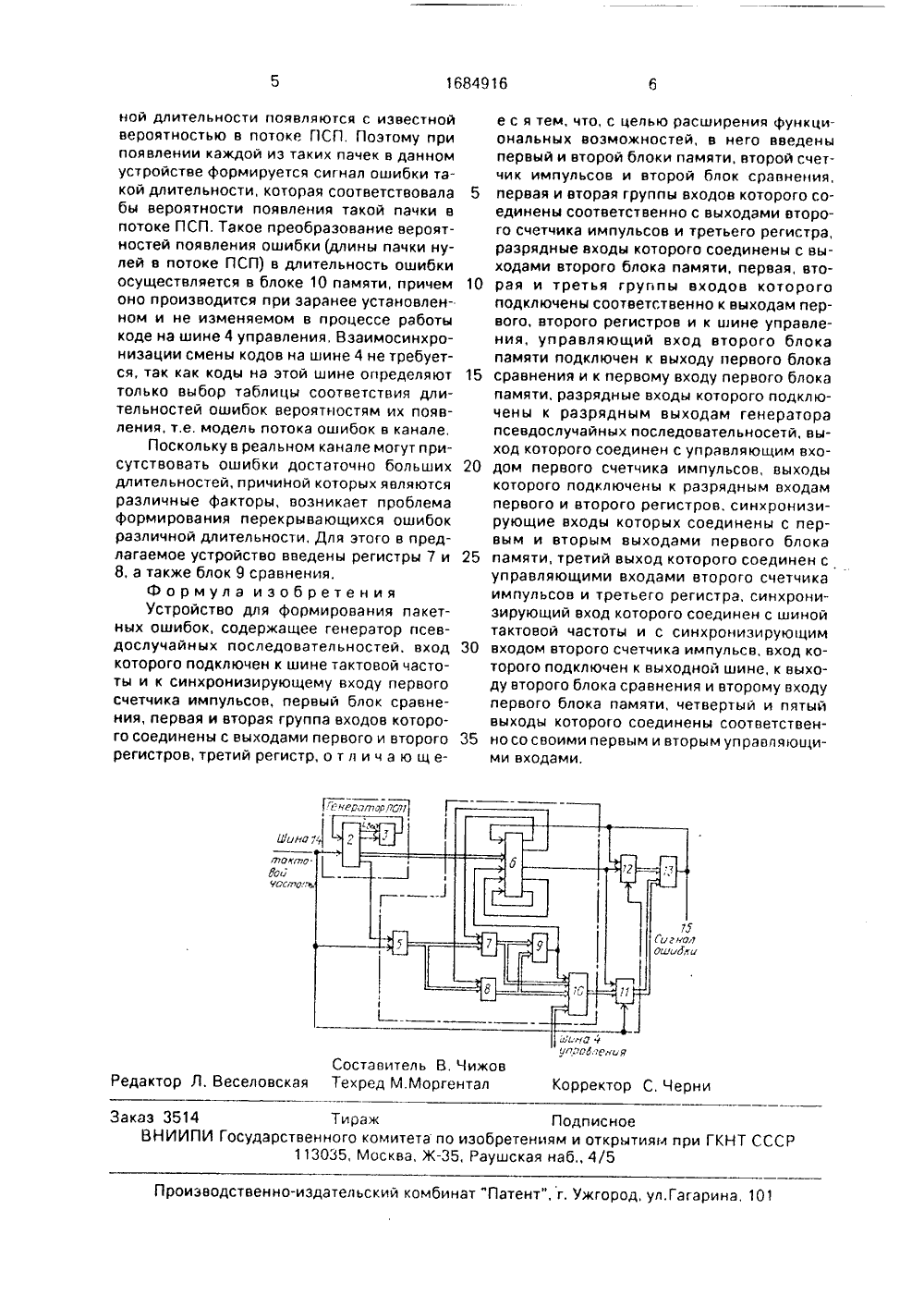

СОК 73 СОВЕСКИХсОциАлистичгских 1684 Ю РГСПУВЛИ 15 Н 03 К 3/84 ОсудАРстВенный кПО ИЗОБРЕТЕНИЯМ ИПРИ ГКНТ СССР ит етКРЫТИЯ ЗОБРЕТЕНИ ОПИ К АВТОРСКО ВИ ЕТЕЛЬСТ следовательскидиовещанияштейн оСС 1984(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯПАКЕТНЫХ ОШИБОК(57) Изобретение может быть использованов стендах контроля и диагностики аппаратуры цифровой обработки информации, в часИзобретение относится к импульсной технике и может быть использовано в стендах контроля и диагностики аппаратуры цифровой обработки информации, в частности для аппаратуры цифровой видеозаписи, а также при моделировании реальных дискретных каналов связи,Цель изобретения - расширение функциональных возможностей за счет формирования потока ошибок с разными длительностями и со своей вероятностью появления.На чертеже представлена блок-схема устройства для формирования пакетных ошибок. я, втор , втор к 13 с выход Устройство для формирования пакетых ошибок содержит генератор 1 псевдолучайных последовательностей (ПСП), ыполненный на регистре 2 сдвига и элэенте ИСКЛЮЧАЮЩЕЕ ИЛИ 3, шину 4 упавления, первый счетчик 5 импульсов,(21) 4685759/21(56) Авторское свидетельстМ 1192121, кл, Н 03 К 3/84 тности для аппаратуры цифровой видеозаписи, и при моделировании дискретных каналов связи, Целью изобретения является расширение функциональных воэможностей за счет формирования потока ошибок с разными длительностями и со своей вероятностью появления. Для достижения цели в устройство для формирования пакетных ошибок введены блоки 6, 10 памяти, регистр 11, счетчик 12 импульсов и блок 13 сравнения, Устройство также содержит генератор 1 псевдослучайных последовательностей, счетчик 5 импульсов, регистры 7, 8 и блок 9 сравнения. Блоки 5-10 выполняют функци о селектора. 1 ил. первый блок 6 памяти, первый 7 и второй 8 регистры, блок 9 сравнени ой блок 10 памяти, третий регистр 11 ой счетчик 12 импульсов, второй бло равнения, шину 14 тактовой частоты, ную шину 0 15 сигнала сшибки, СОВход генератора ПСП 1 подключен к фд, шине 14 к синхронизирующим входам счет- К) чика 5, регистра 11, счетчика 12, выход генератора ПСП 1 подключен к управляющему входу счетчика 5. разрядные выходи генератора ПСП 1 соединены с разрядными входами блока 6 памяти, разрядные выходы счетчика 5 подключены к разрядным входам регистров 7 и 8, синхрониизрующие входы которых соединены с первым и вторым выходами блока 6 памяти, третий выход которого подключен к. управляющим входам счетчика 12 и регистра 11, разрядные входы которого соединены с выходами блока 10 памяти, первая, вторая и третья группы вхо 1684916дов которого соответственно соединены с выходами регистров 7 и 8 и шиной 4, а управляющий вход блока 10 соединен с первым входом блока б и с выходом блока 9 сравнения, первая и вторая группа входов которого соединена с выходами регистров 7 и 8, выходы регистра 11 подключены к первой группе входов блока 13 сравнения, вторая группа входов которого соединена с выходами счетчика 12, вход которого соединен с выходами блока 13 сравнения и с вторым входом блока 6 памяти, четвертый и пятый выходы которого соединены соответственно со своими первым и вторым управляющими входами,Счетчик 5, блок б памяти, регистры 7 и 8, блок 9 сравнения и блок 10 памяти выполняют функцию селектора,Устройство для формирования пакетных ошибок работает следующим образом.Регистр 2 сдвига, имеющий длину гп бит, тактируется с фиксированный частотой 1, поступающей на его синхронизирующий вход по шине 14 тактовой частоты. С выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 нд вход регистра 2 сдвига подается последовательный сигнал, представляющий собой сумму по модулю 2 сигналов и-го разряда регистра 2 сдвига, приходящего на первый вход элемента И СКЛ ЮЧАЮ ЩЕ Е ИЛ И 3, и его последнего (гп-го), разряда, приходящего на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, С выхода регистра 2 сдвига на уп равляющий вход счетчика 5 приходит сигнал псевдослучайной последовательности. Этот же сигнал, но сдвинутый на один, два и три периода тактовой частоты 1 т, поступает с разрядных выходов регистра 2 на входы блока б. Отсутствие сигнала на управляющем входе счетчика 5 соответствует загрузке в счетчик 5 нулей, а его наличие переводит счетчик 5 в режим счетча с тактовой частотой 1, поступающей на его синхронизирующий вход, По окончании счета значение счетчика 5 переписывается в регистр 7 или 8 в зависимости от сигналов, поступающих на синхронизирующие входы этих регистров соответственно с первого или второго выхода блока б памяти. Их временное положение определяется сигналами, поступающими с разрядных выходов генератора ПСП 1 на разрядные входы блока б памяти.Выбор регистра 7 или 8 для записи значения счетчика 5 осуществляется в блоке б памяти по выходному сигналу блока 9 сравнения, поступающему на его первый вход. Этот сигнал определяет большее из значений, установленных на выходах регистров 7 и 8, и в тот регистр, в котором на данный 5 10 15 20 25 30 35 40 45 50 55 момент времени зафиксировано меньшее число, переписывается значение текущего состояния счетчика 5, определяющее дли-у пачки нулей (единиц) в сигнале псевдослучайной последовательности, Сигнал с выхода блока 9 поступает также на управляющий вход блока 10 памяти, в котором г,роизводится преобразование большего из значений, установленных на его первых двух входах, в длительность пакета ошибок, Код соответствия длины пачки нулей (единицц) длительности пакета ошибок поступает го шине 4 управления на третьи входы блока 10 памяти. При поступлении сигнала с выхода блока 9 на вход блока б памяти на его пятом выходе появляется сигнал, приходящий на второй управляющий вход этого блока памяти. Этот сигнал вместе с сигналом с выхода блока 9 однозначно определяет, является ли новое зафиксированное состояние счетчика 5 большим, чем его ранее зафиксированное значение. В этом случае в момент времени, определяемый сигналами с выходов генератора ПСП 1, на третьем выходе блока б памяти формируется сигнал, который поступает на управляющий вход регистра 11, и значение длительности пакета ошибок, установленное на выходе блока 10 памяти, переписывается в регистр 11. Кроме того, под действием сигнала с третьего выхода блока 6, приходящего на управляющий вход счетчика 12, счетчик загружается "нулевым", что гриводит к появлению сигнала ошибок на выходе блока 13 сравнения, Сигнал с выхода блока 13 поступает также на управляющий вход счетчика 12, переводит его в режим счета, осуществляемого с тактовой частотой, и сохраняется в течение всего времени, пока значение на выходе счетчика 12 не совпадает в блоке 13 со значением, зафиксированным на выходе регистра 11. Сигнал ошибки с выходов блока 13 поступает также на вход блока б памяти, При этом в момент окончания сигнала ошибки на четвертом выходе блока 6 появляется сигнал, который поступает на первый управляющий вход этого блока памяти и используется для формирования сигналов, управляющих работой регистров 7 и 8.Таким образом, предлагаемое устройство позволяет сформировать поток ошибок, в котором бы присутствовали ошибки разных длительностей и каждая со своей вероятностью появления, причем определение длительности пачек нулей или единиц в сигнале ПСП осуществляется счетчиком 5, содержимое которого по окончании пачки переписывается в один из двух регистров 7 или 8. Пачки нулей или единиц о ределенЗаказ 3514 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб.,4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина,ной длительности появляются с известной вероятностью в потоке ПСП, Поэтому при появлении каждой из таких пачек в данном устройстве формируется сигнал ошибки такой длительности, которая соответствовала 5 бы вероятности появления такой пачки в потоке ПСП. Такое преобразование вероятностей появления ошибки длины пачки нулей в потоке ПСП) в длительность ошибки осуществляется в блоке 10 памяти, причем 10 оно производится при заранее установленном и не изменяемом в процессе работы коде на шине 4 управления, Взаимосинхрониэации смены кодов на шине 4 не требуется, так как коды на этой шине определяют 15 только выбор таблицы соответствия длительностей ошибок вероятностям их появления, т,е. модель потока ошибок в канале.Поскольку в реальном канале могут присутствовать ошибки достаточно больших 20 длительностей, причиНой которых являются различные факторы, возникает проблема формирования перекрывающихся ошибок различной длительности, Для этого в предлагаемое устройство введены регистры 7 и 25 8, а также блок 9 сравнения.Формула изобретенияУстройство для формирования пакетных ошибок, содержащее генератор псевдослучайных последовательностей, вход 30 которого подключен к шине тактовой частоты и к синхронизирующему входу первого счетчика импульсов, первый блок сравнения, первая и вторая группа входов которого соединены с выходами первого и второго 35 регистров, третий регистр, о т л и ч а ю щ ее с я тем, что, с целью расширения функциональных возможностей, в него введены первый и второй блоки памяти, второй счетчик импульсов и второй блок сравнения, первая и вторая группы входов которого соединены соответственно с выходами второго счетчика импульсов и третьего регистра, разрядные входы которого соединены с выходами второго блока памяти, первая, вторая и третья группы входов которого подключены соответственно к выходам первого, второго регистров и к шине управления, управляющий вход второго блока памяти подключен к выходу первого блока сравнения и к первому входу первого блока памяти. разрядные входы которого подключены к разрядным выходам генератора псевдослучайных последовательносетй, выход которого соединен с управляющим входом первого счетчика импульсов, выходы которого подключены к разрядным входам первого и второго регистров, синхронизирующие входы которых соединены с первым и вторым выходами первого блока памяти, третий выход которого соединен с управляющими входами второго счетчика импульсов и третьего регистра, синхронизирующий вход которого соединен с шиной тактовой частоты и с синхронизирующим входом второго счетчика импульсв, вход которого подключен к выходной шине, к выходу второго блока сравнения и второму входу первого блока памяти, четвертый и пятый выходы которого соединены соответственно со своими первым и вторым управляющими входами,

СмотретьЗаявка

4685759, 03.05.1989

ВСЕСОЮЗНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ТЕЛЕВИДЕНИЯ И РАДИОВЕЩАНИЯ

ЦИЗИН ЛЕОНИД ЕФИМОВИЧ, РОТЕНШТЕЙН АЛЕКСАНДР ДАВИДОВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: ошибок, пакетных, формирования

Опубликовано: 15.10.1991

Код ссылки

<a href="https://patents.su/3-1684916-ustrojjstvo-dlya-formirovaniya-paketnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования пакетных ошибок</a>

Предыдущий патент: Преобразователь случайных сигналов

Следующий патент: Генератор случайного потока импульсов

Случайный патент: Навесное устройство для прямолинейной передвижки конвейера на карьере