Полиномиальный интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

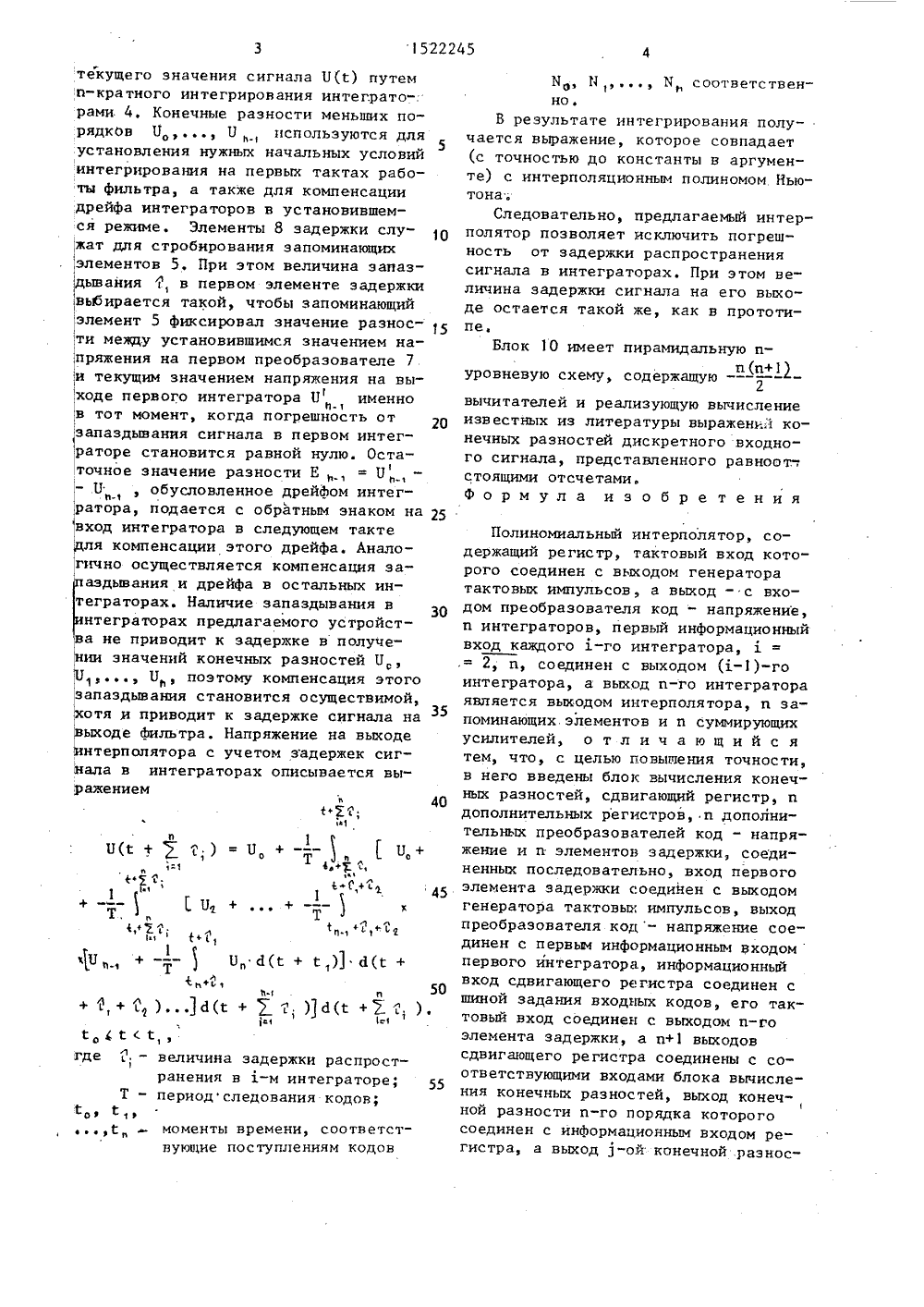

оюз совктсних цидлистичесни 1 Цф 1, 81.1 цц мйя"ь ПИСАНИЕ ИЗОБРЕТЕНИ Р 421 О.П.Пе иш етельство ССС С 7/30, 1979. ельство СССР Н 7/02, 1977. к вычи ыть ис - мерения огоразрядньд каждом такое значение кодаго вместе сэтих10 11 Н. Из игнала блок го порядкавыходах кот нулевого жат для синхразователей 3 запо - мирующие ные препряжение, олнительти регистры упимпульсами от ге пульсов величину лементаи 3 и 7 анными нами 8 задер од - напр ечных раз оз 11 1 т-го поряд образователреобразуют коды коаналоговую формунечная разностьужит для получени и. Пре ение п стей в вычислеигающий о(57) Изобретение относитсялительной технике и можетпользовано в устройствах и Изобретение относится к вычислительной технике и может быть использовано в устройствах измерения и ре-. гулирования.Цель изобретения - повышение точности.На. чертеже представлена схемапредлагаемого интерполятора.Полиномиальный интерполятор содежит генератор 1 тактовых импульсов,регистр 2, преобразователь 3 код -напряжение, интеграторы 4-4минающие элементы 5-5, сумусилители 6-6, дополнительобразователи 7-7код - наэлементы 8,-8 задержки, допные регистры 9,-9, блок 10ния конечных разностей и сдврегистр 11,Устройство раб тает следующим образом. регулирования. Цель изобретения - повьппенле точности, Полиномиальный интерполятор содержит генератор тактовых импульсов, регистр, преобразователь код - напряжение, интеграторы,запоминающие элементы, суммирующиеусилители, дополнительные преобразователи код - напряжение, элементы задержки, дополнительные регистры, блоквычисления конечных разностей, сдвигающий регистр. Интерполятор позволяет исключить погрешность от задержкираспространения сигнала в интеграторах. 1 ил,Последовательныи м сдвигающий регистр 11 те записывает очередн сигнала Б и хранит е предыдущими и кодами (и+1) значений кода с конечнйх разностей имирует на своих (и 1) конечных разностей: о и-го порядка Д- Д.Регистры 2 и 9 слу низации работы преобр 7 код - напряжение. Э равляются тактовыми нератора 1 тактовых иьтекущего значения сигналапутем и-кратного интегрирования интеграто-, рами 4, Конечные разности меньших порядков П У используются для установления нужных начальных условий интегрирования на первых тактах работы фильтра, а также для компенсации дрейфа интеграторов в установившемся режиме. Элементы 8 задержки служат для стробирования запоминающих элементов 5. При этом величина запаздывания 7, в первом элементе задержки выбирается такой, чтобы запоминающий элемент 5 фиксировал значение разнос ти между установившимся значением напряжения на первом преобразователе 7 и текущим значением напряжения на выходе первого интегратора Пименно в тот момент, когда погрешность от запаздывания сигнала в первом интеграторе становится равной нулю. Оста( точное значение разности Е ., = О, - - П обусловленное дрейфом интег ратора, подается с обратным знаком на 25 вход интегратора в следующем такте ,цля компенсации этого дрейфа. Анало 1 гично осуществляется компенсация зааздывания и дрейфа в остальных интеграторах. Наличие запаздывания внтеграторах предлагаемого устройства не приводит к задержке в получении значений конечных разностей П Ц 1 Уь, поэтому компенсация этого ,запаздывания становится осуществимой, хотя и приводит к задержке сигнала на35 выходе фильтра. Напряжение на выходе йнтерпопятора с учетом задержек сиг:нала в интеграторах описывается вы- ражением а)1и(с =ц + - - и,+ъ ал45,4где- величина задержки распространения в 1-м интеграторе; 55Т - периодследования кодов;01, моменты времени, соответствующие поступлениям кодов Ыб, И 1, 9 Мл соответственно,В результате интегрирования получается выражение, которое совпадает(с точностью до константы в аргументе) с интерполяционным полиномом Ньютона,Следовательно, предлагаемый интерполятор позволяет исключить погрешность от задержки распространениясигнала в интеграторах. При этом величина задержки сигнала на его выходе остается такой же, как в прототипе.Блок 1 О имеет пирамидальную пи (и+1уровневую схему, содержащую - -2вычитателей и реализующую вычислениеизвестных из литературы выраженил конечных разностей дискретного входного сигнала, представленного равноот.тстоящими отсчетами.Формула изобретения Полиномиальный интерполятор, содержащий регистр, тактовый вход которого соединен с выходом генератора тактовых импульсов, а выход - с входом преобразователя код - напряжение, и интеграторов, первый информационный вход каждого д-го интегратора, д = 2, и, соединен с выходом (-1)-го интегратора, а выход и-го интегратора является вьмодом интерполятора, и запоминающих. элементов и и суммирующих усилителей, о т л и ч а ю щ и й с я тем, что, с целью повышения точности, в него введены блок вычисления конечных разностей, сдвигающий регистр, и дополнительных регистров, и дополнительных преобразователей код - напряжение и и элементов задержки, соединенных последовательно, вход первого элемента задержки соедийен с вьмодом генератора тактовых импульсов, выход преобразователя код - напряжение соединен с первым информационным входом первого интегратора, информационный вход сдвигающего регистра соединен с шиной задания входных кодов, его тактовый вход соединен с выходом и-го элемента задержки, а и+1 выходов сдвигающего регистра соединены с соответствующими входами блока вычисления конечных разностей, выход конеч-, ной разности и-го порядка которого соединен с информационным входом регистра, а выход 1-ой конечной разнос1522245 а выход - с информационным входом (и)-го запоминающего элемента, выход которого соединен с вторым информационным входом (и)-го интегратора, выход (и)-го элемента задержки соединен с тактовыми входами (п)-х дополнительного регистра и запоминающего элемента. Составитель Г.ОсиповРедактор И.Петрова ,Техред Л.Сердюкова Ксрре. Кабации по иэоб -35, Ра роиэводственно-издательский комбинат "Патент", г.ужго Гагарина, 10 ти, 3 = О, п=1, соединен с информационным входом п)-го дополнительногорегистра, выход которого через соответствующий дополнительный преобразователь код - напряжение соединен спервым входом (и)-го суммирующегоусилителя, второй вход которого соединен с выходом (и)-го интегратора,Заказ 6966/48 , Тираж 668НИИПИ Государственного комите113035, Москва Подписноетениям и открытиям при ГКНТ ССская наб., д. 4/5

СмотретьЗаявка

4411712, 18.04.1988

ПРЕДПРИЯТИЕ ПЯ А-7904

КОНДАКОВ АЛЕКСАНДР ДАСИЕВИЧ, ПЕТРИШИН ЮРИЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор, полиномиальный

Опубликовано: 15.11.1989

Код ссылки

<a href="https://patents.su/3-1522245-polinomialnyjj-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Полиномиальный интерполятор</a>

Предыдущий патент: Логарифмический преобразователь

Следующий патент: Узловой элемент сеточной модели для решения задач тепломассопереноса

Случайный патент: Очиститель головок корнеплодов от ботвы на корню