Регенератор бинарных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1467773

Автор: Недильниченко

Текст

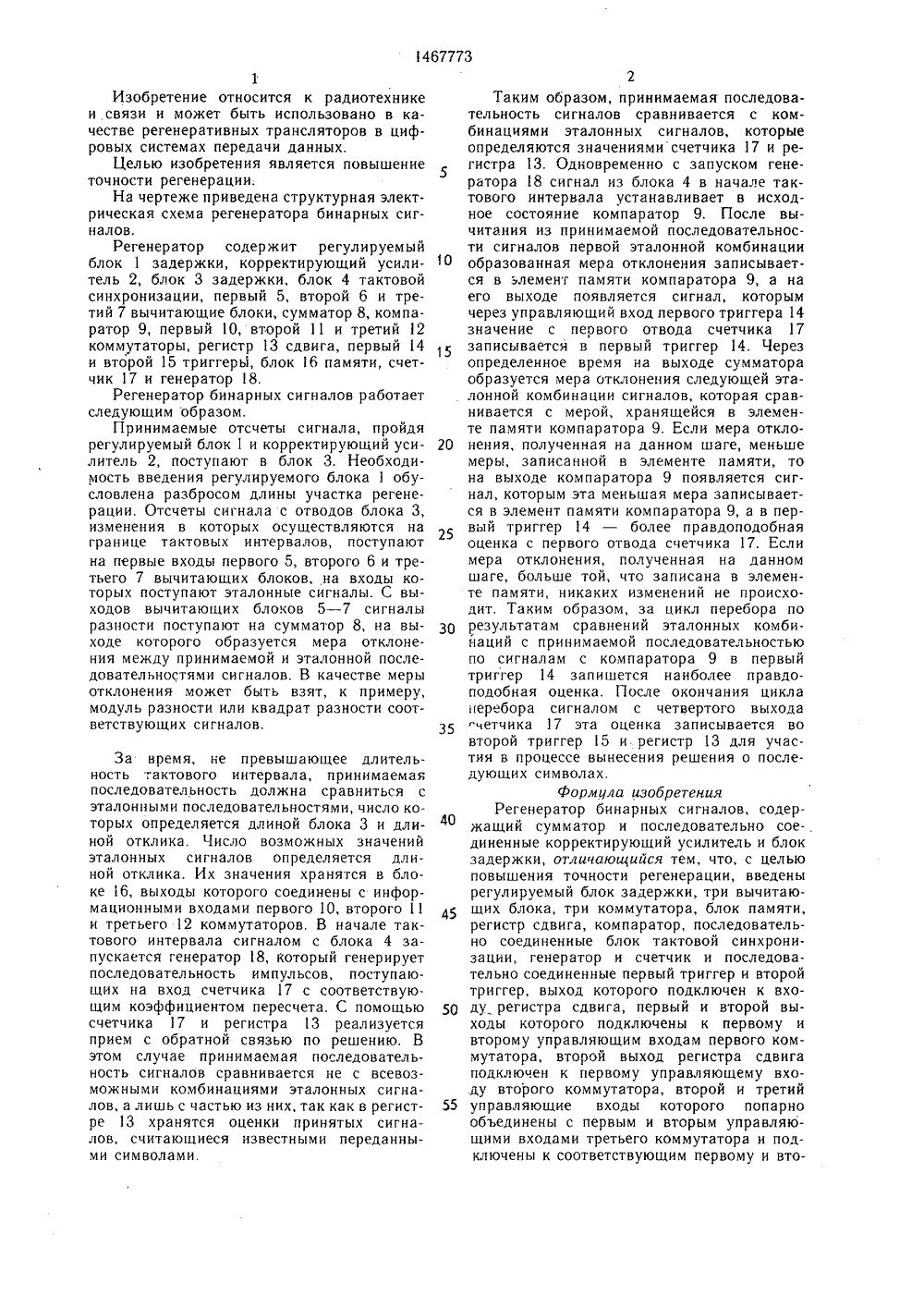

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК146777 04 1 3/08 МИТЕТТКРЫТИЯМ ГОСУДАРСТВЕННЫ ИПО ИЗОБРЕТЕНИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯН А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ синхронизации, вычитаю коммутаторы 10, 11 и 12, триггеры 14 и 15, блок 16 и генератор 18. Необхо регулируемого блока 1 об сом длины участка реге перебора по результатам ных комбинаций с прин вательностью по сигналам в триггер 14 запишется подобная оценка. После перебора сигналом с четве чика 17 эта оценка запи гер 15 и регистр 13 для се вынесения решения о волах.ил. диотех- повы- стиже- лируе- ктовой(71) Одесский электротехническийтут связи им. А. С. Попова(57) Изобретение относится к ранике и связи. Цель изобретенияшение точности регенерации. Для дония цели в регенератор введень 1 регмый блок 1 задержки, блок 4 та шие блоки 5 - 7, регистр 13 сдвига, памяти, счетчик 17 димость введения словлена, разброерации. За цикл сравнений эталонимаемой последос компаратора 9 наиболее правдоокончания цикла ртого выхода счетсывается в тригучастия в процесоследующих сим1Изобретение относится к радиотехнике и связи и может быть использовано в качестве регенеративных трансляторов в цифровых системах передачи данных,Целью изобретения является повышение точности регенерации.На чертеже приведена структурная электрическая схема регенератора бинарных сигналов.Регенератор содержит регулируемый блок 1 задержки, корректирующий усилитель 2, блок 3 задержки, блок 4 тактовой синхронизации, первый 5, второй 6 и третий 7 вычитающие блоки, сумматор 8, компаратор 9, первый 10, второй 11 и третий 12 коммутаторы, регистр 13 сдвига, первый 14 и второй 15 триггеры, блок 16 памяти, счетчик 17 и генератор 18.Регенератор бинарных сигналов работает следующим образом,Принимаемые отсчеты сигнала, пройдя регулируемый блок 1 и корректирующий усилитель 2, поступают в блок 3. Необходимость введения регулируемого блока 1 обусловлена разбросом длины участка регенерации, Отсчеты сигнала с отводов блока 3, изменения в которых осуществляются на границе тактовых интервалов, поступают на первые входы первого 5, второго 6 и третьего 7 вычитающих блоков, на входы которых поступают эталонные сигналы. С выходов вычитающих блоков 5 - 7 сигналы разности поступают на сумматор 8, на выходе которого образуется мера отклонения между принимаемой и эталонной последовательностями сигналов, В качестве меры отклонения может быть взят, к примеру, модуль разности или квадрат разности соответствующих сигналов,За время, не превышающее длительность тактового интервала, принимаемая последовательность должна сравниться с эталонными последовательностями, число которых определяется длиной блока 3 и длиной отклика. Число возможных значений эталонных сигналов определяется длиной отклика. Их значения хранятся в блоке 16, выходы которого соединены с информационными входами первого 10, второго 11 и третьего 12 коммутаторов. В начале тактового интервала сигналом с блока 4 запускается генератор 18, который генерирует последовательность импульсов, поступающих на вход счетчика 17 с соответствующим коэффициентом пересчета. С помощью счетчика 17 и регистра 13 реализуется прием с обратной связью по решению. В этом случае принимаемая последовательность сигналов сравнивается не с всевозможными комбинациями эталонных сигналов, а лишь с частью из них, так как в регистре 13 хранятся оценки принятых сигналов, считающиеся известными переданными символами. 5 10 15 20 25 30 35 40 45 50 55 2Таким образом, принимаемая последовательность сигналов сравнивается с комбинациями эталонных сигналов, которые определяются значениями счетчика 17 и регистра 13. Одновременно с запуском генератора 18 сигнал из блока 4 в начале тактового интервала устанавливает в исходное состояние компаратор 9. После вычитания из принимаемой последовательности сигналов первой эталонной комбинации образованная мера отклонения записывается в элемент памяти компаратора 9, а на его выходе появляется сигнал, которым через управляющий вход первого триггера 14 значение с пеового отвода счетчика 17 записывается в первый триггер 14, Через определенное время на выходе сумматора образуется мера отклонения следующей эталонной комбинации сигналов, которая сравнивается с мерой, хранящейся в элементе памяти компаратора 9. Если мера отклонения, полученная на данном шаге, меньше меры, записанной в элементе памяти, то на выходе компаратора 9 появляется сигнал, которым эта меньшая мера записывается в элемент памяти компаратора 9, а в первый триггер 14 - более правдоподобная оценка с первого отвода счетчика 17. Если мера отклонения, полученная на данном шаге, больше той, что записана в элементе памяти, никаких изменений не происходит. Таким образом, за цикл перебора по результатам сравнений эталонных комбийаций с принимаемой последовательностью по сигналам с компаратора 9 в первый триггер 14 запишется наиболее правдоподобная оценка. После окончания цикла перебора сигналом с четвертого выхода четчика 17 эта оценка записывается во второй триггер 15 и регистр 13 для участия в процессе вынесения решения о последующих символах,Формила изобретенияРегенератор бинарных сигналов, содержащий сумматор и последовательно соединенные корректирующий усилитель и блок задержки, отличающийся тем, что, с целью повышения точности регенерации, введены регулируемый блок задержки, три вычитающих блока, три коммутатора, блок памяти, регистр сдвига, компаратор, последовательно соединенные блок тактовой синхронизации, генератор и счетчик и последовательно соединенные первый триггер и второй триггер, выход которого подключен к входу регистра сдвига, первый и второй выходы которого подключены к первому и второму управляющим входам первого коммутатора, второй выход регистра сдвига подключен к первому управляющему входу второго коммутатора, второй и третий управляющие входы которого попарно объединены с первым и вторым управляющими входами третьего коммутатора и подключены к соответствующим первому и вто14 б 7773 Составитель В. Шевцов Редактор И. Шмакова Техред И. Верес Корректор Л. Г 1 илипенко Заказ 1215/56 Тираж 627 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж - 35, Рау шская наб., д. 4/5 Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101рому выходам счетчика, первый выход которого подключен к первому входу первого триггера и третьему управляющему входу первого коммутатора, третий выход счетчика подключен к однолинейному управляющему входу третьего коммутатора, а четвертый выход счетчика соединен с вторым входом второго триггера, одноименныеинформационные входы первого, второго и третьего коммутаторов объединены и подключены к соответствующим выходам блока памяти, выходы первого, второго и третьего коммутаторов подключены к первым входам соответствующих первого, второго и третьего вычитающих блоков, вторые входы которых подключены к соответствующим первому, второму и третьему выходам блока задержки, четвертый выход которого соединен с входом блока тактовой синхронизации, выход которого подключен к первому входу компаратора, второй вход которого соединен с выходом сумматора, первый, второй и третий входы которого подключены к выходам соответствующих первого, второго и третьего вычитающих блоков, причем выход компаратора подключен к второму входу первого триггера, а выход регулируемого блока задержки подключен к входу корректирующего усилителя, выход которого соединен с управляющим входом регулируемого блока задержки.

СмотретьЗаявка

4255181, 02.06.1987

ОДЕССКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. А. С. ПОПОВА

НЕДИЛЬНИЧЕНКО ВЛАДИМИР ДМИТРИЕВИЧ

МПК / Метки

МПК: H04J 3/08

Метки: бинарных, регенератор, сигналов

Опубликовано: 23.03.1989

Код ссылки

<a href="https://patents.su/3-1467773-regenerator-binarnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Регенератор бинарных сигналов</a>

Предыдущий патент: Модулятор стереофонического сигнала

Следующий патент: Устройство для ответвления цифровых сигналов

Случайный патент: Электрический соединитель