Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1438007

Авторы: Ковнир, Цодыковский

Текст

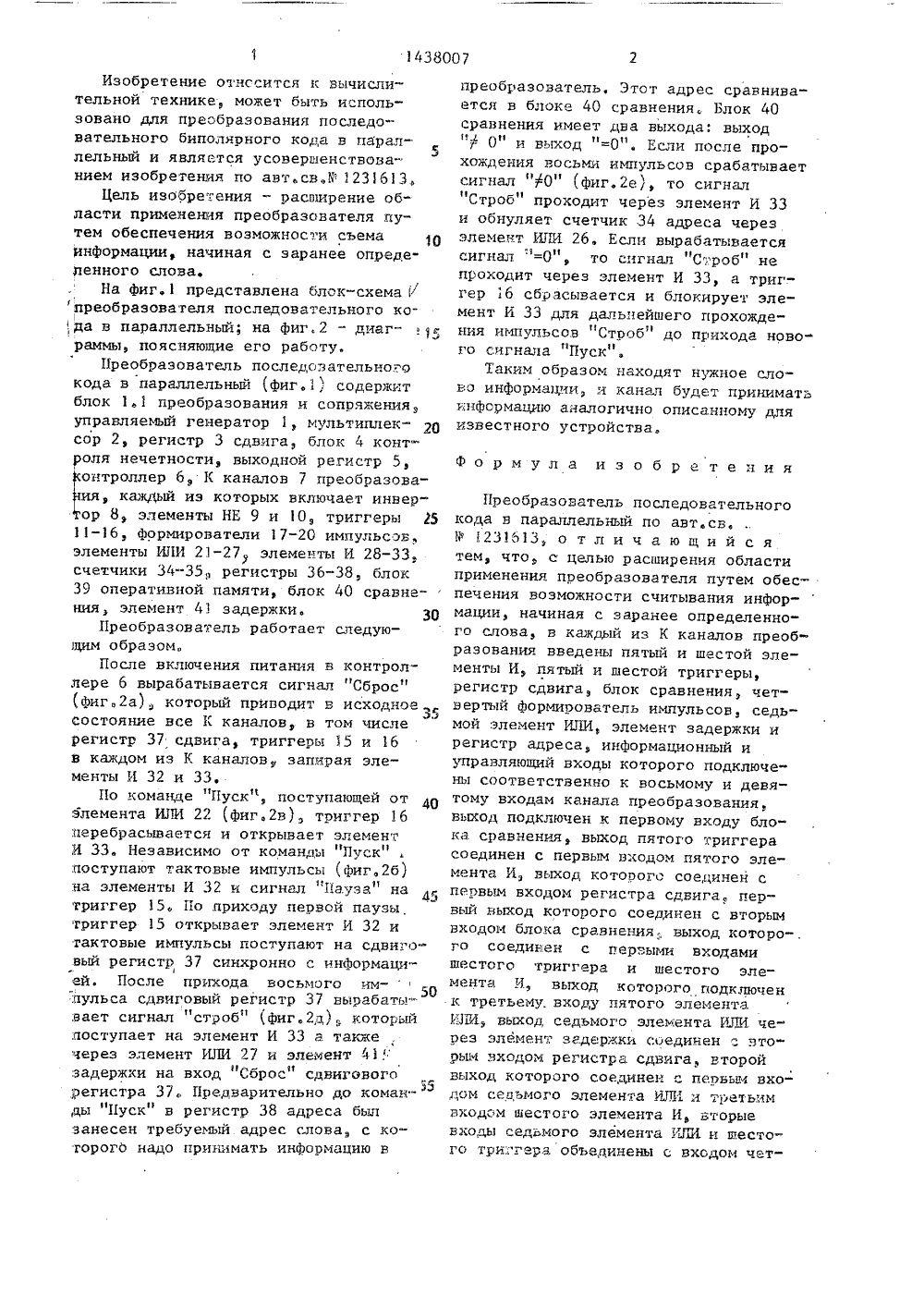

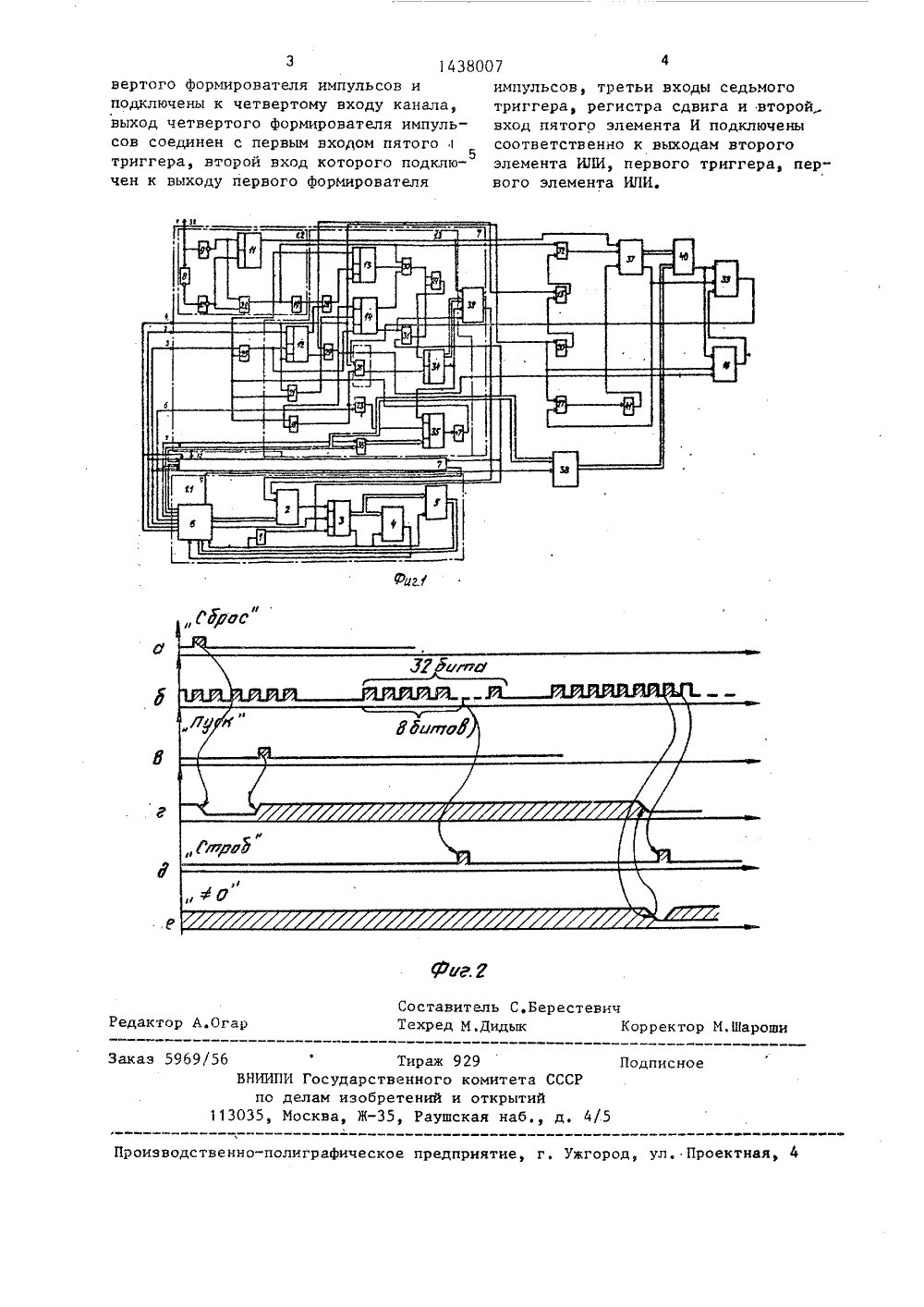

Изобретение отнссится к вычислительной технике, может быть использовано для преобразования последовательного биполярного кода в параплельный и является усовершенствова" нием изобретения по авт.св.Р 1231613,Цель изобретения - расширение области применения преобразователя путем обеспечения возможности съема информации, начиная с заранее опредеЛенного слова.На фиг.1 представлена блок-схема 1 преобразователя последовательного кода в параллельный; на фиг.2 - диаграммы, пояс:няющие его работу.Преобразователь последовательного кода в параллельный (Фиг.1) содержит блок 1.1 преобразования и сопряжения, управляемый генератор 1, мультиплек О сор 2, регистр 3 сдвига, блок 4 контроля нечетности, выходной регистр 5, онтроллер 6, К каналов 7 преобразоваия, каждый иэ которых включает инверор 8, элементы НЕ 9 и 1 О, триггеры 25 11 - 16, Формирователи 17-20 импульсов. элементы ИЛИ 21-27 элементы И 28-33, счетчики 34-35 регистры 36-38, блок 39 оперативной памяти, блок 40 сравнения, элемент 41 задержки. ЗОПреобразователь работает следующим образомПосле включения питания в контроллере 6 вырабатывается сигнал "Сброс" фиг.2 а) который приводит в исходное состояние все К каналов, в том числе регистр 37 сдвига, триггеры 15 и 16 в каждом из К каналов, запирая элементы И 32 и 33.По команде 1 Пуск", поступающей от элемента ИЛИ 22 (Фиг.2 в), триггер 16 перебрасывается и открывает элементГ 1 И 33. Независимо от команды Пуск поступают тактовые импульсы (Фиг,2 б) :на элементы И 32 и сигнал "Пауза" на триггер 15 По приходу первой паузы, триггер 5 открывает элемент И 32 и тактовые импульсы поступают на сдвиговый регистр 37 синхронно с информацией. После прихода восьмого им-;пульса сдвиговый регистр 37 вырабаты вает сигнал "строб" (фиг.2 д), который поступает на элемент И 33 а также через элемент ИЛИ 27 и элемент 41." задержки на вход "Сброс" сдвиговогоэ 5 регистра 37 Предварительно до коман-. ды "Пуск" в регистр 38 адреса был занесен требуемый адрес слова, с которого надо принимать информацию в преобразователь. Этот адрес сравнивается в блоке 40 сравнения., Блок 40 сравнения имеет два выхода: выход р О" и выход "=О". Если после прохождения восьми импульсов срабатывает сигнал "О" (фиг.2 е), то сигнал "Строб" проходит через элемент И 33 и обнуляет счетчик 34 адреса через элемент И 1 И 26. Если вырабатывается сигнал =0", то сигнал "Строб" не проходит через элемент И 33, а триггер 16 сбрасывается и блокирует элемент И 33 для дальнейшего прохождения импульсов "Строб" до прихода нового сигнала "Пуск".Таким образом находят нужное слово информации, и канал будет принимать информацию аналогично описанному для известного устройства.формула изобретенияПреобразователь последовательного кода в параллельньй по авт.св. У 1231613, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения преобразователя путем обеспечения возможности считывания информации, начиная с заранее определенного слова, в каждый из К каналов преобразования введены пятый и шестой элементы И, пятый и шестой триггеры, регистр сдвига, блок сравнения, четвертый Формирователь импульсов, седьмой элемент ИЛИ, элемент задержки и регистр адреса, информационный и управляющий входы которого подключены соответственно к восьмому и девятому входам канала преобразования, выход подключен к первому входу блока сравнения, выход пятого триггера соединен с первым входом пятого элемента И выход которого соединен с первым входом регистра сдвига, первый выход которого соединен с вторым входом блока сравнения выход которо-. го соединен с первыми входами шестого триггера и шестого элемента И, выход которого подключен к третьему, входу пятого элемента И 1 И, выход седьмого элемента ИЛИ через элемент задержки соединен вторым входом регистра сдвига, второй выход которого соединен с первым входом седьмого элемента ИП и третьим входом шестого элемента И, вторые входы седьмого элемента ИПИ и шестого триггера обьединены с входом чет3 34380074вертого Формирователя импульсов и импульсов, третьи входы седьмогоподключены к четвертому входу канала, триггера, регистра сдвига и второйвыход четвертого формирователя импуль- вход пятого элемента И подключенысов соединен с первым входом пятогосоответственно к выходам второго5триггера, второй вход которого подклю- элемента ИЛИ, первого триггера, пер"чен к выходу первого Формирователя ного элемента ИПИ. ель С,Берестевич,Дидык Корректор М. Шароши остав ехред актор А.Ога аз 5969/5 б 929 комитета и открыти ская наб, П Тираж НИИПИ Государственног по делам изобретений 35, Москва, Ж, Рау

СмотретьЗаявка

4083374, 02.07.1986

ПРЕДПРИЯТИЕ ПЯ М-5537

КОВНИР ВИКТОР ИВАНОВИЧ, ЦОДЫКОВСКИЙ ЕВГЕНИЙ ИСИДОРОВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 15.11.1988

Код ссылки

<a href="https://patents.su/3-1438007-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Устройство для подсчета числа единиц двоичного кода по модулю к

Следующий патент: Преобразователь кодов

Случайный патент: Установка для индукционного нагрева заготовок