Управляемый формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1309302

Авторы: Заболотный, Максимов, Петричкович, Филатов

Текст

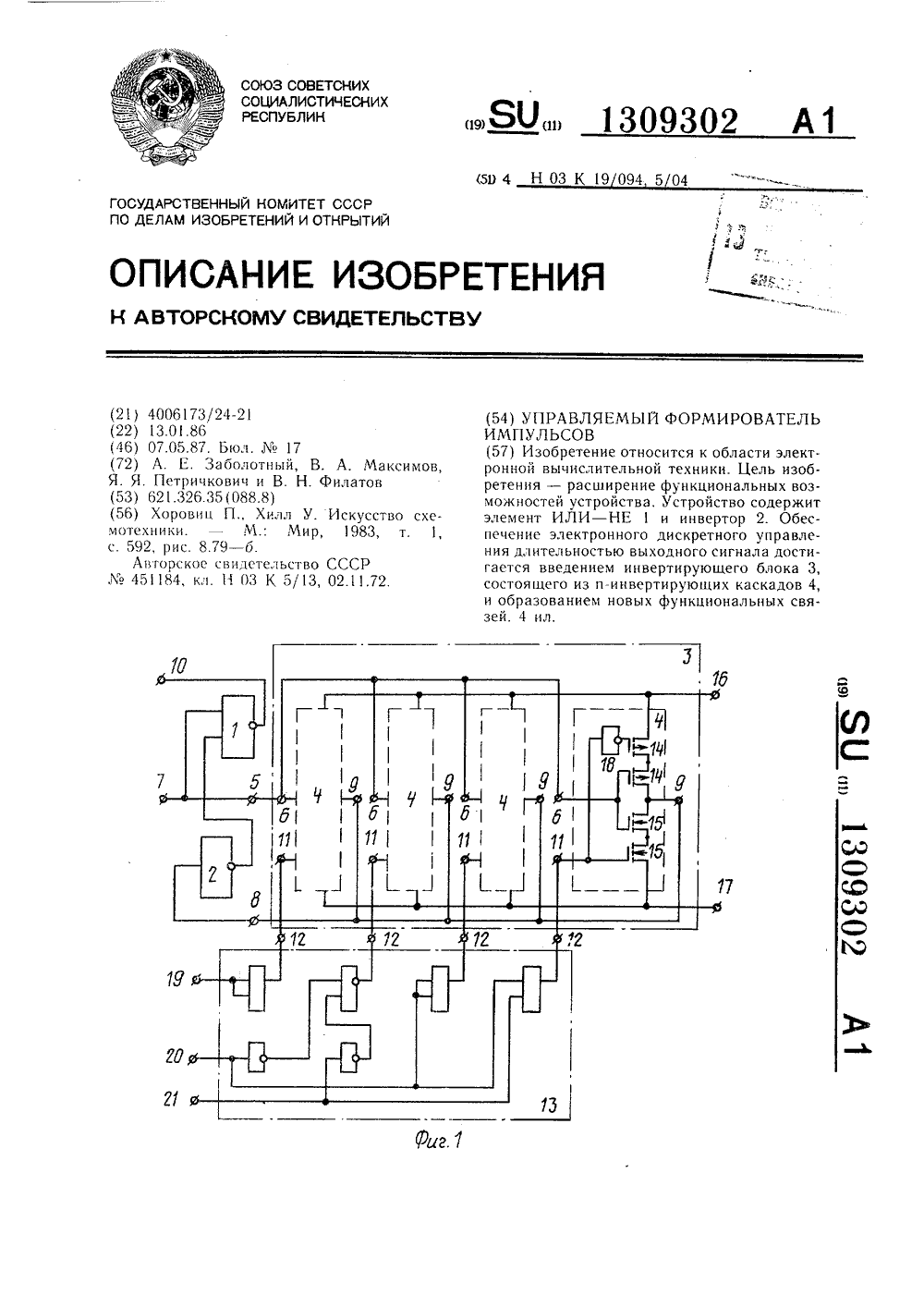

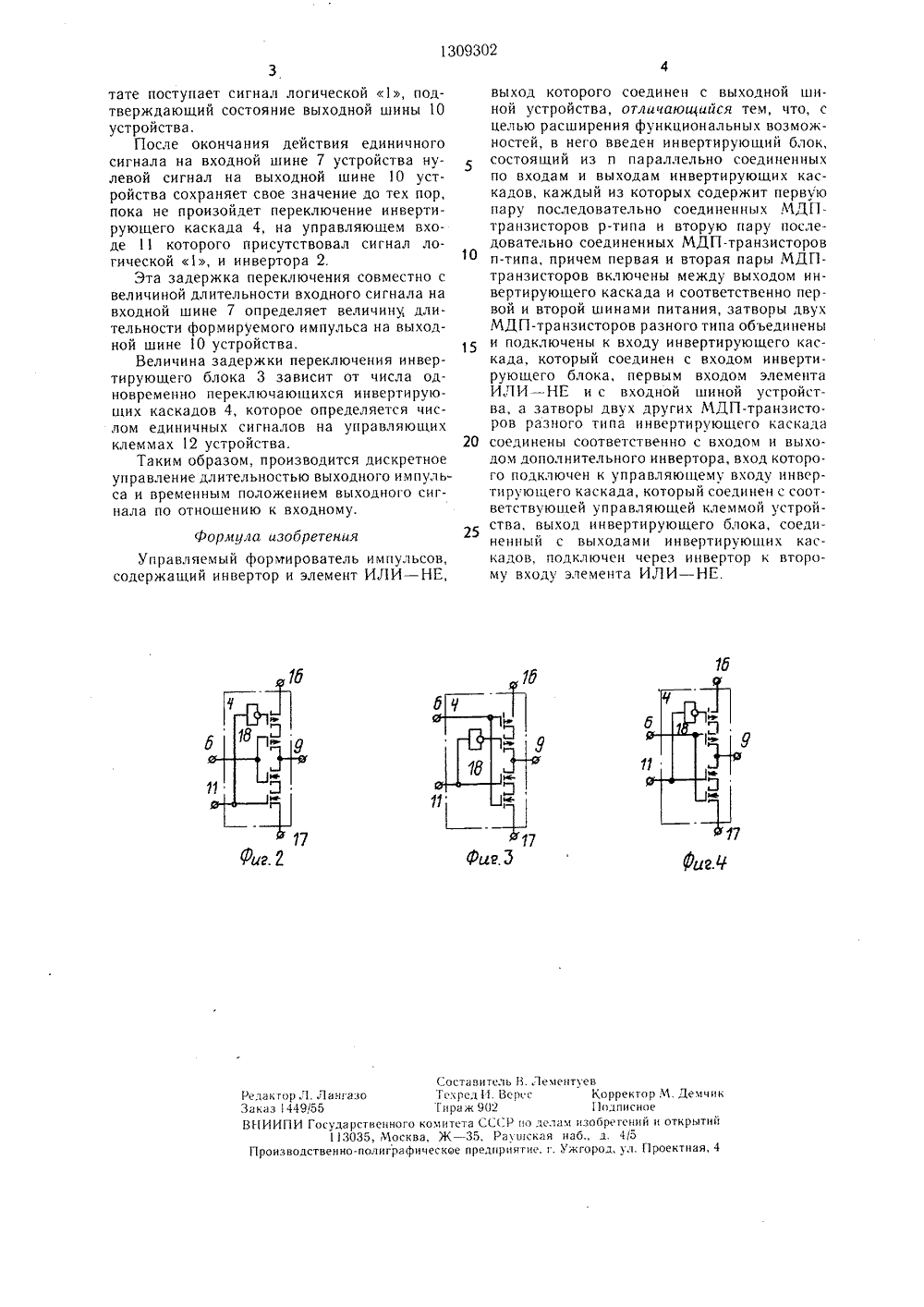

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН И 9) (11) А РЕТЕН ЕТЕЛЬСТВУ элект- изобх возержит ОбесА. Ма кси моилатов Искусство схер, 1983, т. 1,во СССР13, 02. 1.72. ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОПИСАН И А ВТОРСКОМУ(57) Изобретение относится к областиронной вычислительной техники. Цельретения - расширение фу нкциональньможностей устройства. Устройство содэлемент ИЛИ в1 и инвертор 2.печение электронного дискретного управления длительностью выходного сигнала достигается введением инвертирующего блока 3,состояшего из п-инвертируюших каскадов 4,и образованием новых функциональных связей. 4 ил.1Изобретение относится к электронной вы числительной технике и может быть использовано в качестве устройства формирования импульсов по фронтам входного сигналя с управлением по длительности.Целью изобретения является расширение функциональных возможностей устройства, а имсщо обеспечение электронного дискретного управления длительностью выходного сигнала путем введения инвертируюшего блока, состоящего из п параллельно соединенных инвертирующих каскадов, один из входов которых подключен к управляющей клемме устройства, благодаря чему достигается изменение числа одновременно включенных инвертирующих каскадов при подаче определенной комбинации сигналов на управляющие клеммы устройства, вследствие чс го дискретно изменяется залсржк сигнала В 5 Ивертцру(о(цм блоке (следов 1- тельно, длительность выходного сигналя.На фцг. 1 приведена функциональная схсмя лнраВЛ 51 смОГО фОрм ировятсл 51 имцульсоц; ця фиг. 2- - 4 - примеры реализации инвертирующего каскада, цыцолцсцио ца К-МДП-транзисторах.Устройство содержит элемент ИЛИ- - НЕ 1. Инвертор 2, ицвертируюший блок 3, сотояший из и ицвсртирук(цих каскадов 4. Вход 5 ицвертирующего блока 3 соединен с входами 6 цццертирующих каскадов 4, с первым входом элемента ИЛИ - НЕ 1 и подклкгчсц к входной шине 7 усройствя. В.ход 8 ццвертирующего блока 3 соедццсц с Выхолями 9 иццсртируюццх каскадов 4 и с Входом ицверторя 2, Выход которого подключен к второму входу элсмец та ИЛИ - НЕ 1, выход которого являет я выходной шиной 10 устройств; . Уцравляощис входы 1 Ицвсртиру(ошцх каскадов 4 подключены к соответству(ошцм управляющим к(сл(лал) 12 устройс(В(1, которые являются Выходами устройсВ 13 уцряцлсЦИ 51.Кс 1 жлый ицвсртируюц 1 и 1 каска;), 4 содсржит первую пару поспелова гсльцо соедицсццых М,11-трлИзисторов 14 р-тиц и Втор)ю цс рм пос)(ловстс;15 ИО со(ли цсцць х М, 1,1 1- тряГзистор(гц 15 )-тцця, црцчсм первая и ВТОРс 51 Цс)РЬ 1 ТРс 1 ЦЗИСОРОВ ВКОс(СЦЫ МСЖЛУ выхолом 9 ццпертируюшего каскад 4 и соответственно первой 16 ц ВгорОЙ 17 ц и(ями 1(итяциц устройства. 31 тв 1 рь лух трц- ЗИСОрОВ 4 И 15 рс 1 ЗИОГО )Иц ОбЬСИИИС- цы и по,(.кл(очсны к входу 6 иццсртируюшсго каскада, а затворы других трянзцс- ТОРОВ СОСДИЦСЦЬ 1 СООТВЕСТВСЦО С ВХОЛОМ И Выходом дополнительного ицвертора 8, вход которОГО цодклк)чсц к упряц)51 к)ц(ему Вхсду 1 ццвсртцрующсго кскаля 1В ксчсс 1 вс ицВср 10 рс 1 2 мке быгь (ГПОЛЬЗОВс 1 ЦЯ ГРПпс ЦС 1 СТНОГО ЧИС(1 ПОС 1 С. довятсльш) Вкл)очеццых инвсрторов.Устройство 3 управления может бть вьиолцецо в Виде лсшифрятора, рс ис"ря5 10 и произвольного преобразователя кодов фиг, ). На выходах (клеммах 12) устройства 13 управления устанавливается требуемая комбинация сигналов, формируемых в зависимости от кода, поданного на шины настройки 19 - 2. На фиг.приведен пример конкретной реализации устройства 13 управления для инвертирующих каскадов 4, построенных на основе устройства (фиг. 2), которое реализовано в виде комбинационной схемы на логических элементах И, И - НЕ и инверторах. 20 25 30 35 40 45 50 55 Управляемый формирователь импульсовфункционирует следующим образом.В исходном состоянии на входную шину 7 устройства подается нулевой сигнал, а на шины настройки 19 - 2 поданкод, например, 1, О, О. В результате навыходах кгСл(лях 12) лстройства 13 управления формируется комбинация сигналов1, О, О, 0 в соответствии с числом и параллельно соединенных инвертирующих каскадов 4 в ицвертирующем блоке 3. Число единичных сигналов на управляющих клеммах 12 устройства в зависимости от коданастройки может быть от одного до и. В соответствии с этим такое же число инвертирующих каскадов 4Отово к переключению,Единичный управс 5 юций сигнал подается на управляющий вход 11 соответствующего инвертирующеп) каскада 4 и открываст пару МДП-транзисторов разного типа.Поскольку вхолной сигнал равен нулю, второй МД 11-транзистор и-типа при этом заперт,а второй МДП-транзистор р-типа того жеинвертирующсго каскада 4 открыт. Поэтомуня выходе 9 хотя бы одного инвертирующего каскада 4 и, следовательно, ца выходе 8 ицвертирую(цего блока 3 через одну пару МДП-транзисторов р-тица формируется сигнал логической , равный напряжению ца первой шине 16 питания устройства.На втором входе элемента ИЛИ - НЕ 1при этом устанавливается нулевой сигнал,а на выходной пине 10 устройств - единичный. Устройство -отово к работе.При поступлении ня входную шину 7устройстсвя единичИц о сигнала элементИЛИ НЕ 1 переключается, и на выходной шине 10 устройства формируется фронтспада формируемого импульса. Одновременно начинает псреклк)чаться инвертируюшийкаскад 4, ня управляющем Входе 1 которо(о был шлан сигнал логическойотсоответствующей клеммы 12 управления,МДП-транзистор 14 цри этом закрывается,я 5(сДГ 1-транзистор 15 того же инвсртируюшсго каскада 4 открывается. На выходе 91 анш)го ицвертирующего каскада 4 и, следовательно, на выходе 8 ицвертирующего блока 3 формируется сигнал логического 0. Навторой вход элемента ИЛИ - НЕв резуль1309302 1 б 7 ие,З Состави Тскрсд 1 1 ира ж 9 комитета С а, Ж - 35, гческое пре ель В. 1 емснтуев. Верее КоррПодиС(:Р по делам изобретРа шская наб., д.приятие, г. Ужгород,едактор 1. а 1 ангазоаказ 1449/55ВИИИПИ Государственного113035, МоскПроизводственно-полиграф ектор М. Деисноеений и открь4/5 тий оектная, 4 тате поступает сигнал логической 1, подтверждающий состояние выходной шины 10 устройства.После окончания действия единичного сигнала на входной шинеустройства нулевой сигнал на выходной шине 1 О устройства сохраняет свое значение до тех пор, пока не произойдет переключение инвертирующего каскада 4, на управляющем входе 11 которого присутствовал сигнал логической 1, и инвертора 2.Эта задержка переключения совместно с величиной длительности входного сигнала на входной шине 7 определяет величину длительности формируемого импульса на выходной шине 10 устройства.Величина задержки переключения инвертирующего блока 3 зависит от числа одновременно переключающихся инвертирующих каскадов 4, которое определяется числом единичных сигналов на управляющих клеммах 12 устройства.Таким образом, производится дискретное управление длительностью выходного импульса и временным положением выходного сигнала по отношению к входному. Формула изобретения Управляемый формирователь импульсов,содержащий инвертор и элемент ИЛИ - НЕ,выход которого соединен с выходной шиной устройства, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен инвертирующий блок, состоящий из и параллельно соединенных по входам и выходам инвертирующих каскадов, каждый из которых содержит первчю пару последовательно соединенных МДП- транзисторов р-типа и вторую пару последовательно соединенных МДП-транзисторов п-типа, причем первая и вторая пары МДП- транзисторов включены между выходом инвертирующего каскада и соответственно первой и второй шинами питания, затворы двух МДП-транзисторов разного типа объединены и подключены к входу инвертирующего каскада, который соединен с входом инвертируюгцего блока, первым входом элемента ИЛИ - НЕ и с входной шиной устройства, а затворы двух других МДП-транзисторов разного типа инвертирующего каскада 20 соединены соответственно с входом и выходом дополнительного инвертора, вход которого подключен к управляющему входу инвертирующего каскада, который соединен с соответствующей управляющей клеммой устройства, выход инвертирующего блока, соединенный с выходами инвертирующих каскадов, подключен через инвертор к второму входу элемента ИЛИ - НЕ.

СмотретьЗаявка

4006173, 13.01.1986

ОРГАНИЗАЦИЯ ПЯ В-8466

ЗАБОЛОТНЫЙ АЛЕКСЕЙ ЕФИМОВИЧ, МАКСИМОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ПЕТРИЧКОВИЧ ЯРОСЛАВ ЯРОСЛАВОВИЧ, ФИЛАТОВ ВАЛЕРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 19/094, H03K 5/04

Метки: импульсов, управляемый, формирователь

Опубликовано: 07.05.1987

Код ссылки

<a href="https://patents.su/3-1309302-upravlyaemyjj-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Управляемый формирователь импульсов</a>

Предыдущий патент: Схема согласования уровней ттл-эсл

Следующий патент: Синхронный делитель частоты следования импульсов на пять

Случайный патент: Устройство для замены элементов армировки в вертикальных стволах эксплуатационных шахт