Преобразователь числа из двоичной системы счисления в систему остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

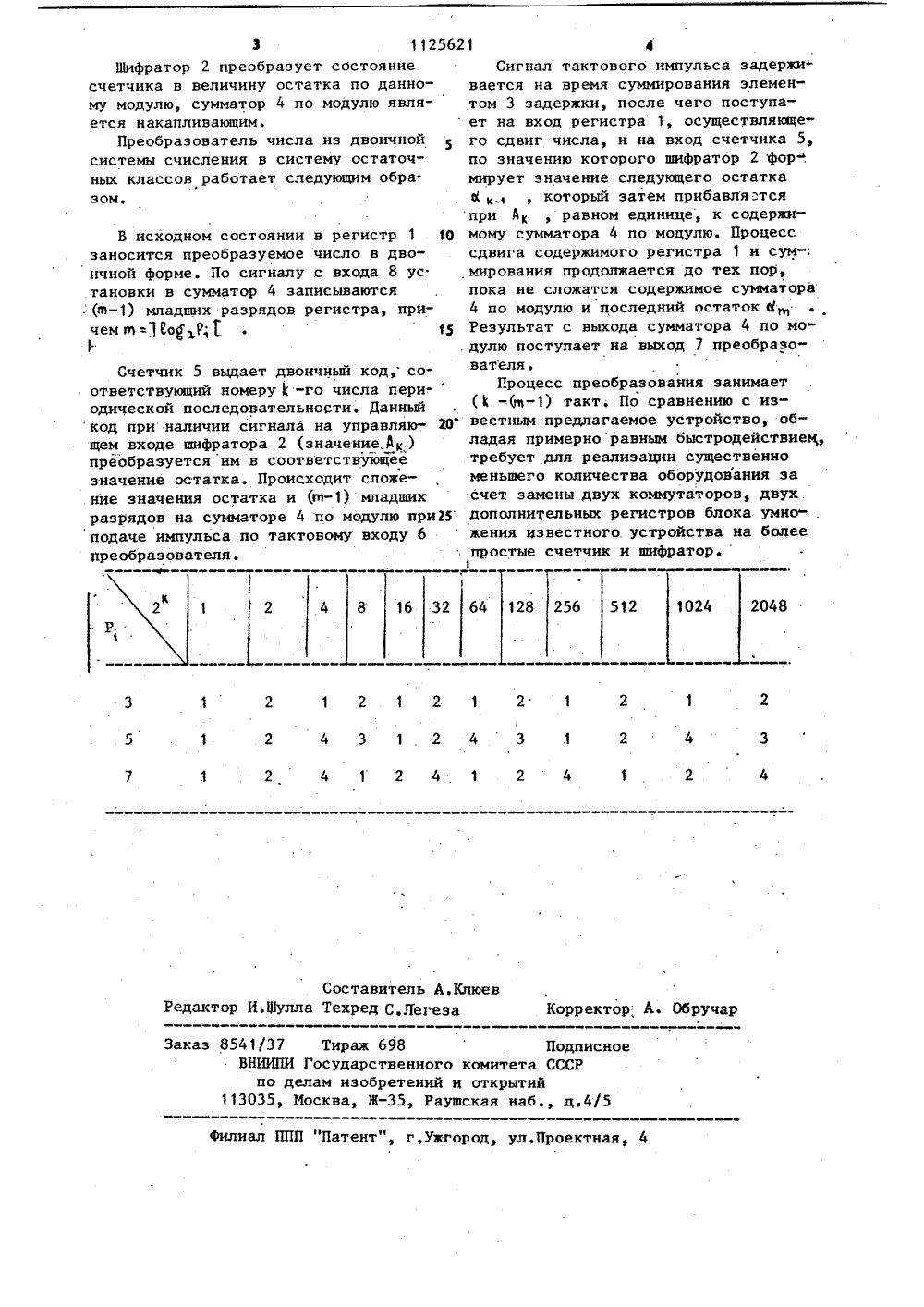

(56) 1, Авторское свидетельство СССР У 525947, кл. С 06 Г 5/02, 1975.2. Авторское свидетельство СССР У 1001079, кл. 606 Г 5/02, 1981 (прототип) .(54) (57) ПРЕОБРАЗОВАТЕЛЬ ЧИСЛА ИЗ ДВОИЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В СИСТЕМУ ОСТАТОЧНЫХ КЛАССОВ, содержащий входной регистр и сумматор по модулю, причем выход сумматора по модулю является выходом преобразователя, о тл и ч а ю щ и й с я тем, что, с целью сокращения количества оборудова.Хлевной ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПЪЮ ОПИСАНИЕ ИК АВТОРСКОМУ СВИДЕТ ния, он содержит шифратор, счетчик иэлемент задержки, причем выходы (%-1) младших разрядов входного регистра соединены соответственно с входа-ми первой группы сумматора по модулю,входы второй группы которого соединены соответственно с выходами шифратора, информационный и управляющийвходы которого соединены соответственно с выходом счетчика и выходомстаршего разряда входного регистра,тактовый вход которого соединен свходом счетчика и выходом элементазадержки, вход которого соединен стактовым входом сумматора по модулюи тактовым входом преобразователя,вход начальной установки которогосоединен с входами начальной установ"ки счетчика и сумматора по модулю.1125621 Изобретение относится к вычислительной технике и может быть использовано при сопряжении устройств,функционирующих в позиционной системе остаточных классов. 5Известен преобразователь числа издвоичной системы счисления в системуостаточных классов,. содержащий входной регистр, матрицу преобразованиядвоичного хода в промежуточный непозиционный код, корректирующие матричные сумматоры 1 .Данное устройство обладает большим объемом оборудования и низкимбыстродействием. 15Наиболее близким к изобретениюпо технической сущности являетсяпреобразователь числа из двоичнойсистемы счисления в систему остаточных классов, содержащий входной регистр, сумматор по модулю, блок умножения, два дополнительных регистра,Два коммутатора, причем первый и второй выходы выходного регистра соединены соответственно с первыми входами 2первого коммутатора и сумматора помодулю, выход которого соединен свходами первого и второго дополнительных регистров и является выходомпреобразователя, входы сдвига основной и дополнительной записи которогосоединены соответственно с управляющими входами входного первого и второго дополнительных регистров, выходы которых. соединены соответственнос первым и вторым входами второго35коммутатора, выход которого соединенс вторьм входом первого коммутатора,выход которого соединен с входом.блока умножения выход которого соеЭ40динен с вторым входом сумматора помодулю 21 .Недостатком известного преобразователя является большое количествооборудования,Целью изобретения является сокращение количества оборудования.ЪуПоставленная цель достигаетсятем, что преобразователь числа иэдвоичной системы счисления в систему 50остаточных классов, содержащий вход-,ной регистр и сумматор по.модулю,причем выход сумматора по модулю яв"ляется выходом преобразователя, со держит шифратор, счетчик и элемент 55задержки, причем выходы.(е) младших разрядов входного регистра соединены соответственно с входами первой 1 группы сумматора по модулю, входывторой группы которого соединены соответственно с выходами шифратора,информационный и управляющий входыкоторого соединены соответственно свыходом счетчика и выходом старшегоразряда входного регистра, тактовыйвход которого соединей с входом счет/чика и выходом элемента задержки,вход которого соединен с тактовымвходом сумматора по модулю и тактовымвходом преобразователя, вход начальной установки которого соединен свходами начальной установки счетчикаи сумматора по модулю.На чертеже представлена схема пре.обраэователя числа из двоичной системы счисления в систему остаточныхклассов,Преобразователь числа из двоичнойсистемы счисления в систему остаточных классов содержит входной регистр1, шифратор 2, элемент 3 задержки,сумматор 4 по модулю, счетчик 5,тактовый вход 6 преобразователя, выход 7 преобразователя, вход 8 началь.ной установки преобразователя.Работа преобразователя числа издвоичной системы в систему остаточных классов заключается в следующем,Число в двоичной системе счисления можно представить в видех=А 2 +А2 А 2( % огде К =0,1,2Для перевода числа х в СОК необходимо осуществить преобразование числапо модулю Р;рс; = хт.к. А принимает значения "О" или"1", то х можно представить При представлении весов разрядов по модулкГ Р; можно наблюдать периодичность повторения остатков. Например, при представлении двоичных раз- рядов по модулю 3,5 и 7 получаются последовательности остатков, приведенные в таблице. Представление весов разрядов по модулю 3 имеют периодичность Т=2, по модулю 5-Т=4, по модулю 7-Т=З.Счетчик 5 работает по модулю, рав ному периодичности остатков по данному модулю.3 1125621Шифратор 2 преобразует состояние счетчика в величину остатка по данно" му модулю, сумматор 4 по модулю явля-ется накапливающим.Преобразователь числа из двоичной системы счисления в систему остаточных классов работает следующим обраРэом,1024 204 4 128 256 16 3 1 2 1 2 2 2 4 Составитель А.КпюевРедактор И.Вулла Техред С.Легеза Корректор А. Обручар Заказ 8541/37 Тираж 698ПодписноВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж-ЗЬ, Раушская наб., д.4/5 иал ППП "Патент", г,ужгород ул.Проектная, 4 В исходном состоянии в регистр 1 10 заносится преобразуемое число в двоичной форме. По сигналу с входа 8 ус. тановки в сумматор 4 записываются .(а) младших разрядов регистра, причем т =1 6 о Р;15 1 Счетчик 5 выдает двоичный код, соответствующий номеру-го числа пери-одической последовательности. Данный код при наличии сигнала на управляю- Ю щем входе шифратора 2 (значение.Дк ) преобразуется им в соответствующее значение остатка. Происходит сложение значения остатка и (в) мпадших разрядов на сумматоре 4 по модулю при 25 подаче импульса по тактовому входу 6 Преобразователя,4Сигнал тактового импульса задерживается на время суммирования элементом 3 задержки, после чего поступает на вход регистра 1, осуществляющего сдвиг числа, и на вход счетчика 5, по значению которого шифратор 2 фор-. мирует значение следующего остатка К , , который затем прибавлятся при Д , равном единице, к содержимому сумматора 4 по модулю. Процесс сдвига содержимого регистра 1 и сум- ьярования продолжается до тех пор, пока не сложатся содержимое сумматора 4 по модулю и последний остаток Ю Результат с выхода сумматора 4 по модулю поступает на выход 7 преобразователя.Процесс преобразования занимает (1 -(щ) такт. По сравнению с известным предлагаемое устройство, обладая примерноравным быстродействием, требует для реализации существенно меньшего количества оборудования эа счет замены двух коммутаторов, двух дополнительных регистров блока умно- . жения известного. устройства на более простые счетчик и шифратор.

СмотретьЗаявка

3631757, 09.08.1983

СТАВРОПОЛЬСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ СВЯЗИ ИМ. 60-ЛЕТИЯ ВЕЛИКОГО ОКТЯБРЯ

ИВАНОВ СЕРГЕЙ ВЛАДИМИРОВИЧ, ХЛЕВНОЙ СЕРГЕЙ НИКОЛАЕВИЧ, ШВЕЦОВ НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 5/02

Метки: двоичной, классов, остаточных, систему, системы, счисления, числа

Опубликовано: 23.11.1984

Код ссылки

<a href="https://patents.su/3-1125621-preobrazovatel-chisla-iz-dvoichnojj-sistemy-schisleniya-v-sistemu-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь числа из двоичной системы счисления в систему остаточных классов</a>

Предыдущий патент: Дешифратор двоичного кода

Следующий патент: Устройство для сравнения цифровых кодов

Случайный патент: Устройство для роликовой сварки гибких герметических металлических труб (рукавов), изготавливаемых из профилированной ленты