Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1083360

Авторы: Волощенко, Петренко, Петровский

Текст

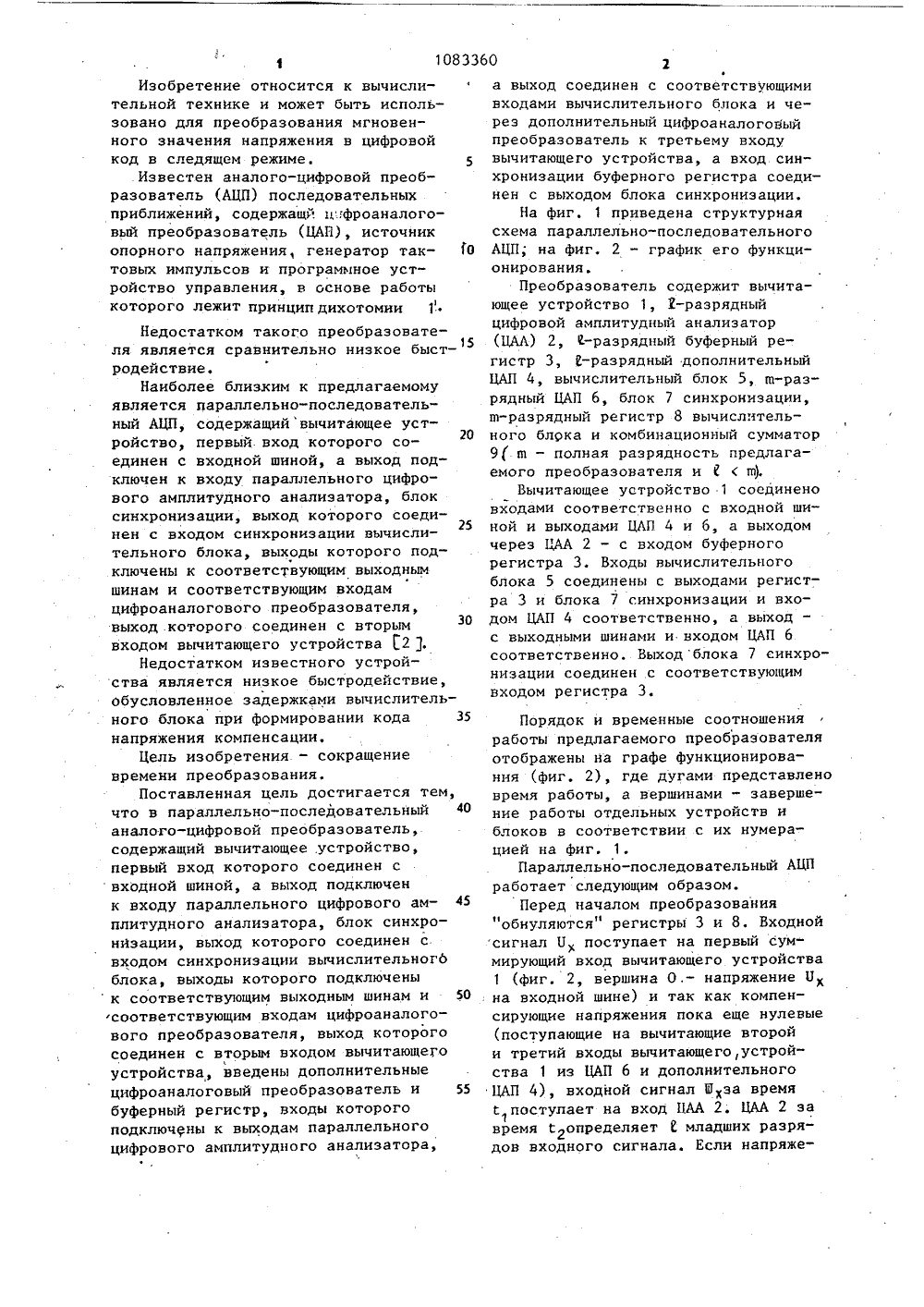

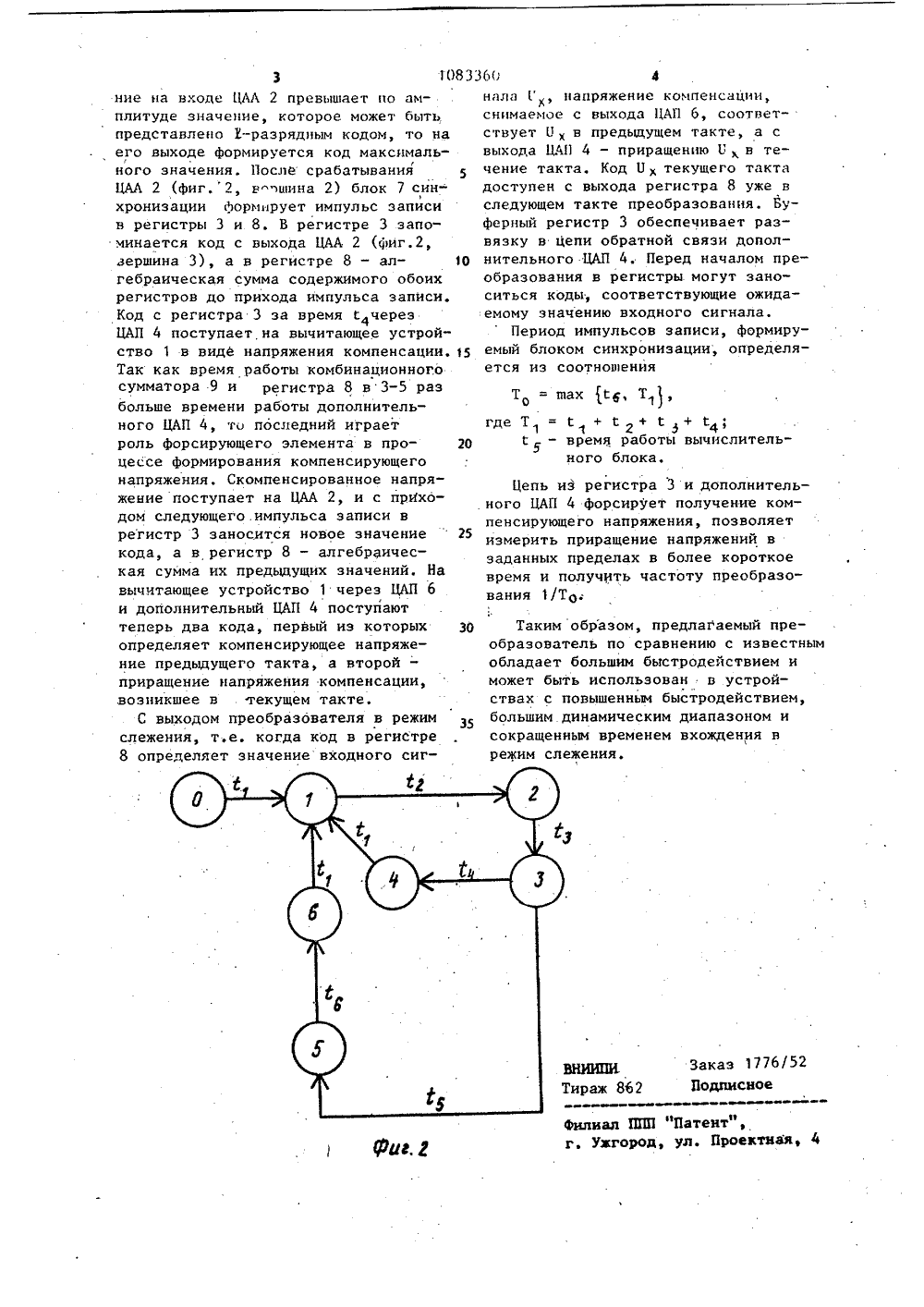

(54)(57) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ,содержащий вычитающее устройство,первый вход которого соединен свходной шиной, а выход подключен квходу параллельного цифрового амплитудного анализатора, блок синхронизации, выход которого соединен с входом синхронизации вычислительного1 блока, выходы которого подключены к соответствующим выходным шинам и соответствующим входам цифроаналогового преобразователя, выход которого соединен с вторым входом вычитающего устройства, о т л и ч аю щ и й с я тем, что, с целью сокра щения времени преобразования,в него введены дополнительный цифроаналоговый преобразовательн буферный регист входы которого подключены к выходам параллельного цифрового амплитудного анализатора, а выход соединен с со-. ответствующими входами вычислительного блока и через дополнительный цифроаналоговый преобразователь - к третьему входу вычитающего устройства, а вход синхронизации буферного регистра соединен с выходом блока синхронизации,Изобретение относится к вычислительной технике и может быть использовано для преобразования мгновенного значения напряжения в цифровой код в следящем режиме.Известен аналого-цифровой преобразователь (АЦП) последовательных приближений, содержащй ц.:фроаналоговый преобразователь (ЦАН), источник опорного напряжения, генератор тактовых импульсов и программное устройство управления, в основе работы которого лежит принцип дихотомии 110 20 Недостатком такого преобразователя является сравнительно низкое быст 15родействие,Наиболее близким к предлагаемомуявляется параллельно-последовательный АЦП, содержащийвычитающее устройство, первый. вход которого соединен с входной шиной, а выход подключен к входу параллельного цифрового амплитудного анализатора, блоксинхронизации выход которого соеди 125нен с входом синхронизации вычислительного блока, выходы которого подключены к соответствующим выходнымшинам и соответствующим входамцифроаналогового преобразователя,выход которого соединен с вторым30входом вычитающего устройства 2 1.Недостатком известного устройства является низкое быстродействие,обусловленное задержками вычислительного блока при формировании кода 35напряжения компенсации,Цель изобретения - сокращениевремени преобразования.Поставленная цель достигается тем,что в параллельно-последовательный 40аналого-цифровой преобразователь,содержащий вычитающее устройство,первый вход которого соединен свходной шиной, а выход подключенк входу параллельного цифрового амплитудного анализатора, блок синхронизации, выход которого соединен свходом синхронизации вычислительног 6блока, выходы которого подключенык соответствующим выходным шинам и 50соответствующим входам цифроаналогового преобразователя, выход которогосоединен с вторым входом вычитающегоустройства, введены дополнительныецифроаналоговый преобразователь и 55буферный регистр, входы которогоподключены к выходам параллельногоцифрового амплитудного анализатора,а выход соединен с соответствующимивходами вычислительного блока и через дополнительный цифроаналоговыйпреобразователь к третьему входувычитающего устройства, а вход синхронизации буферного регистра соединен с выходом блока синхронизации.На фиг. 1 приведена структурнаясхема параллельно-последовательногоАЦП; на фиг. 2 - график его функционирования,Преобразователь содержит вычитающее устройство 1, К-разрядныйцифровой амплитудный анализатор(ЦАА) 2, В-разрядный буферный регистр 3, -разрядный дополнительныйЦАП 4, вычислительный блок 5, ш-разрядный ЦАП 6, блок 7 синхронизации,ш-разрядный регистр 8 вычислительного блрка и комбинационный сумматор9ш - полная разрядность предлагаемого преобразователя и 1 ( в).Вычитающее устройство 1 соединеновходами соответственно с входной шиной и выходами ЦЛП 4 и 6, а выходомчерез ЦАА 2 - с входом буферногорегистра 3. Входы вычислительногоблока 5 соединены с выходами регистра 3 и блока 7 синхронизации и входом ЦАП 4 соответственно, а выход -с выходными шинами и входом ЦЛП 6соответственно. Выход блока 7 синхронизации соединен с соответствующимвходом регистра 3. Порядок и временные соотношения работы предлагаемого преобразователя отображены на графе функционирования (фиг. 2), где дугами представлено время работы, а вершинами - завершение работы отдельных устройств и блоков в соответствии с их нумерацией на фиг. 1,Параллельно-последовательный АЦП работает следующим образом.Перед началом преобразования "обнуляются" регистры 3 и 8. Входной сигнал Б поступает на первый суммирующий вход вычитающего устройства 1 (фиг. 2, вершина О. - напряжение Цх на входной шине) и так как компенсирующие напряжения пока еще нулевые (поступающие на вычитающие второй и третий входы вычитающего,устройства 1 из ЦАП 6 и дополнительного ЦАП 4), входной сигнал Шэа времяпоступает на вход ПАА 2, ЦАА 2 эа 1время 12 определяетмладших разрядов входного сигнала. Если напряжеИПИж 86 3ние на входе ЦАЛ 2 превышает по амплитуде значение, которое может быть представлено У-разрядным кодом, то на его выходе формируется код максимального значения. После срабатывания ЦАЛ 2 (фиг."2, в "шина 2) блок 7 син-хронизации формирует импульс записи в регистры 3 и 8. В регистре 3 запоминается код с выхода ЦАА 2 (фиг.2, вершина 3), а в регистре 8 - ал гебраическая сумма содержимого обоих регистров до прихода импульса записи. Код с регистра 3 эа времячерез4 ЦАП 4 поступает на вычитающее устройство 1 в виде напряжения компенсации. 15 Так как время работы комбинационного сумматора 9 и регистра 8 в 3-5 раэ больше времени работы дополнительного ЦАП 4, то последний играет роль форсирующего элемента в про цессе формирования компенсирующего напряжения. Скомпенсированное напряжение поступает на ЦАА 2, и с приходом следующего. импульса записи в регистр 3 заносится новое значение 25 кода, а в регистр 8 - алгебраическая сумма их предыдущих значений. На вычитающее устройство 1 через ЦАП 6 и дополнительный ЦАП 4 поступают теперь два кода, первый из которых З 0 определяет компенсирующее напряжение предыдущего такта, а второй- приращение напряжения компенсации, возникшее в текущем такте.С выходом преобразователя в режим слежения, т.е. когда код в регистре 8 определяет значение входного сиг 361; 4нала Г напряжение компенсации, снимаемое с выхода ЦА 11 6, соответствует Цв предыдущем такте, а с выхода ЦАП 4 - приращению Пв течение такта. Код Цтекущего такта доступен с выхода регистра 8 уже в следующем такте преобразования. Йуферный регистр 3 обеспечивает развязку в цепи обратной связи дополнительного ЦАП 4. Перед началом преобразования в регистры могут заноситься коды, соответствующие ожидаемому значению входного сигнала.Период импульсов записи, формируемый блоком синхронизации, определяется иэ соотношения Т,=шах с, ТгдеТ,= т +С 2+ С 5+ С 4с 5 - время работы вычислительного блока. Цепь из регистра 3 и дополнительного ЦАП 4 форсирует получение компенсирующего напряжения, позволяет измерить приращение напряжений в заданных пределах в более короткое время и получить частоту преобразования 1/ТО; Таким образом, предлагаемый преобразователь по сравнению с известным обладает большим быстродействием и может быть использован в устройствах с повышенным быстродействием, большим динамическим диапазоном и сокращенным временем вхождения в режим слежения. филиал ППП "Патент", . ужгород, ул. Проектная, 4

СмотретьЗаявка

3308784, 26.06.1981

ВОЛОЩЕНКО СЕРГЕЙ АЛЕКСЕЕВИЧ, ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ, ПЕТРОВСКИЙ СЕРГЕЙ ВИКТОРОВИЧ

МПК / Метки

МПК: H03K 13/17

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 30.03.1984

Код ссылки

<a href="https://patents.su/3-1083360-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Преобразователь код-ток

Следующий патент: Фазочувствительный преобразователь напряжение-код

Случайный патент: Жаропрочный сплав на основе никеля