Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 487390

Авторы: Асцатуров, Ковалев, Кондратьев, Мальцев

Текст

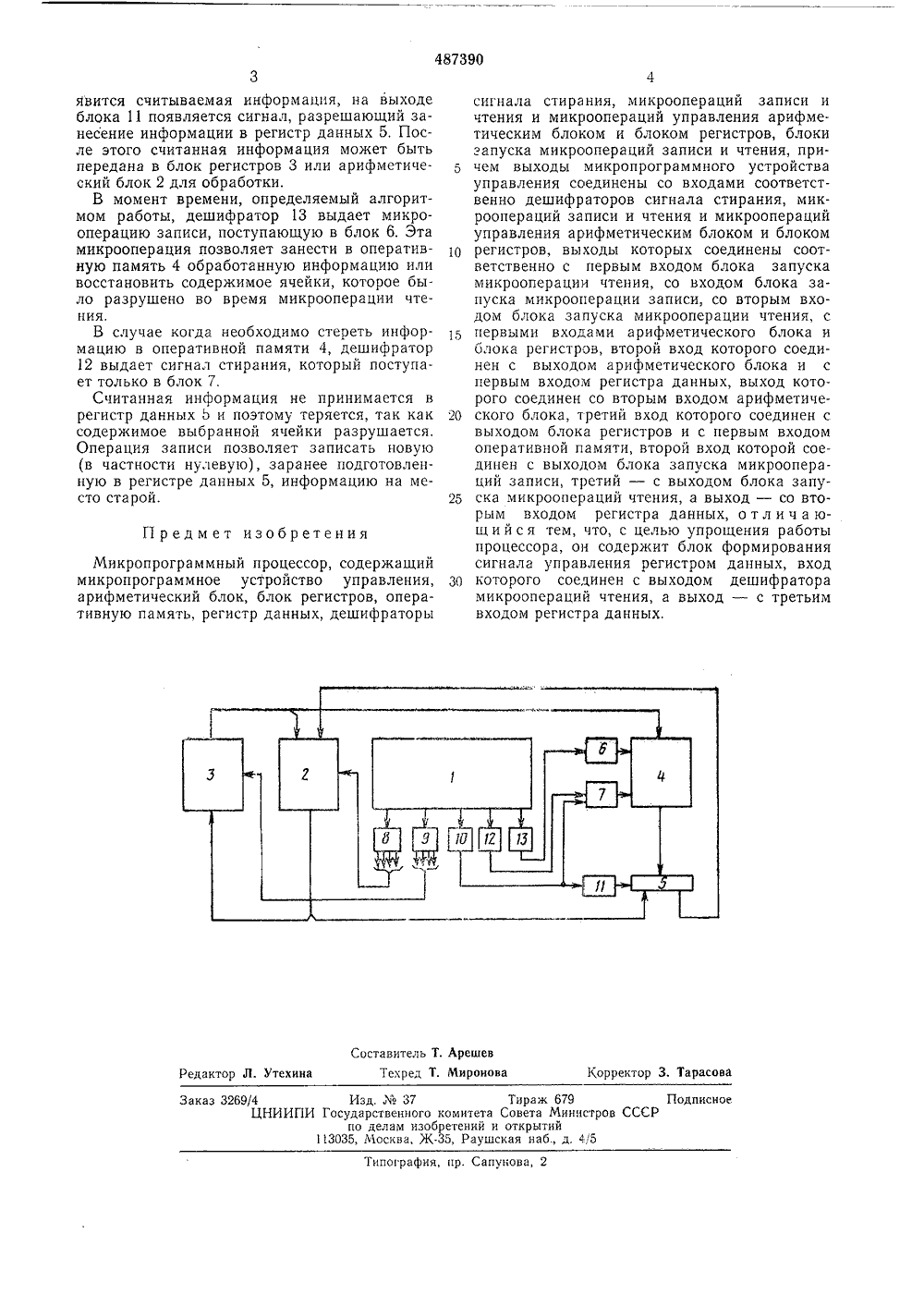

(51) М. Кл Государственный комитет Совета Министров ССС о 3) х Д 1 х 68 326(0888 Опчбчиковано37 10.75, Бюллет евам изобретений и открытий та опубликования описания 20.01.(54) МИКРОПРОГРАММНЫИ ПРОЦЕССО 1Изобретение относится к области вычислительной техники и предназначено для использования в ЦВМ.Известны микропрограммные процессоры, содержащие микропрограммное устройство управления, арифметический блок, блок регистров, оперативную память с расщепленным циклом обращения, регистр данных, дешифраторы сигнала стирания, микроопераций записи и чтения и микроопераций управления арифметическим блоком и блоком регистров и блоки запуска микроопераций записи и чтения,Недостатком известных процессоров является то, что интервал времени между началом микрооперации чтения и началом микрооперации записи должен быть немного меньше или равен времени считывания - времени от момента выдачи микрооперации чтения до момента появления информации на выходе оперативной памяти.Целью изобретения является упрощение работы процессора.Эта цель достигается путем введения блока формирования сигнала управления регистром данных, вход которого соединен с выходом дешифратора микроопераций чтения, а выход - с третьим входом регистра данных.Функциональная схема процессора изобракена на чертеже,Микропрограммный процессор содержитмикропрограммное устройство управления 1; арифметический блок 2, соединенный с блоком регистров 3; оперативную память 4, под ключенную к выходу блока регистров 3; регистр данных 5, соединенный с арифметическим блоком 2 и оперативной памятью 4; блок запуска микроопераций записи 6 и блок запуска микроопераций чтения 7, подклю ченные к оперативной памяти 4. Эти блокиуправляются дешифраторами, входы которых подключены к устройству 1. Выходы дешифратора микроопераций управления арифметическим блоком 8 подключены к арифметиче скому блоку 2, выходы дешифратора микроопераций управления блоком регистров 9 - к блоку регистров 3. Выходы дешифратора микроопераций чтения 10 подключены к блоку 7 и блоку формирования сигнала управле ния регистром данных 11, выход которогоподключен к регистру данных 5, Выход дешифратора сигнала стирания 12 подключен к блоку 7, а выход дешифратора мпкрооперацпй записи 13 - к входу блока 6.Во время работы процессора производятсяобращения к оперативной памяти 4. При чтении информации дешифратор 10 выдает микрооперацию чтения, которая поступает на блок 7 и на вход блока 11, К тому времени, 31 когда на выходе оперативной памяти 4 по487390 Предмет изобретения Составитель Т. Арешеведактор Л. Утехина Техред Т. Миронова Корректор 3, Тарасова каз 3269/4 Изд. ЛТ 37 ЦНИИПИ Государственног по делам из 113035, Москва, ПодписноеСССР Тираж 679комитета Совета Минисбретений и открытийЖ, Раушская наб., д. 4,ипография, пр. Сапунова, 2 явится считываемая информация, на выходе блока 11 появляется сигнал, разрешающий занесение информации в регистр данных 5, После этого считанная информация может быть передана в блок регистров 3 или арифметический блок 2 для обработки.В момент времени, определяемый алгоритмом работы, дешифратор 13 выдает микро- операцию записи, поступающую в блок 6. Эта микрооперация позволяет занести в оперативную память 4 обработанную информацию или восстановить содержимое ячейки, которое было разрушено во время микрооперации чтения.В случае когда необходимо стереть информацию в оперативной памяти 4, дешифратор 12 выдает сигнал стирания, который поступает только в блок 7.Считанная информация не принимается в регистр данных Ь и поэтому теряется, так как содержимое выбранной ячейки разрушается. Операция записи позволяет записать новую (в частности нулевую), заранее подготовленную в регистре данных 5, информацию на место старой. Микропрограммный процессор, содержащий микропрограммное устройство управления, арифметический блок, блок регистров, оперативную память, регистр данных, дешифраторы сигнала стирания, микроопераций записи и чтения и микроопераций управления арифметическим блоком и блоком регистров, блоки запуска микроопераций записи и чтения, при чем выходы микропрограммного устройствауправления соединены со входами соответственно дешифраторов сигнала стирания, микроопераций записи и чтения и микроопераций управления арифметическим блоком и блоком 10 регистров, выходы которых соединены соответственно с первым входом блока запуска микрооперации чтения, со входом блока запуска микрооперации записи, со вторым входом блока запуска микрооперации чтения, с первыми входами арифметического блока и блока регистров, второй вход которого соединен с выходом арифметического блока и с первым входом регистра данных, выход которого соединен со вторым входом арифметиче ского блока, третий вход которого соединен свыходом блока регистров и с первым входом оперативной памяти, второй вход которой соединен с выходом блока запуска микроопераций записи, третий - с выходом блока запу ска микроопераций чтения, а выход - со вторым входом регистра данных, о т л и ч а ющ и й с я тем, что, с целью упрощения работы процессора, он содержит блок формирования сигнала управления регистром данных, вход 30 которого соединен с выходом дешифраторамикроопераций чтения, а выход - с третьим входом регистра данных,

СмотретьЗаявка

1931335, 08.06.1973

ПРЕДПРИЯТИЕ ПЯ М-5339

АСЦАТУРОВ РУБЕН МИХАЙЛОВИЧ, КОВАЛЕВ ОЛЕГ СЕМЕНОВИЧ, КОНДРАТЬЕВ АНАТОЛИЙ ПАВЛОВИЧ, МАЛЬЦЕВ НИКОЛАЙ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 05.10.1975

Код ссылки

<a href="https://patents.su/2-487390-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для контроля и управления электропитанием электронной вычислительной машины

Следующий патент: Устройство для дефференцирования алгебраических полиномов

Случайный патент: Устройство для разбора матричных строк на наборной строкоотливной машине