Система обмена данными в вычислительной сети

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

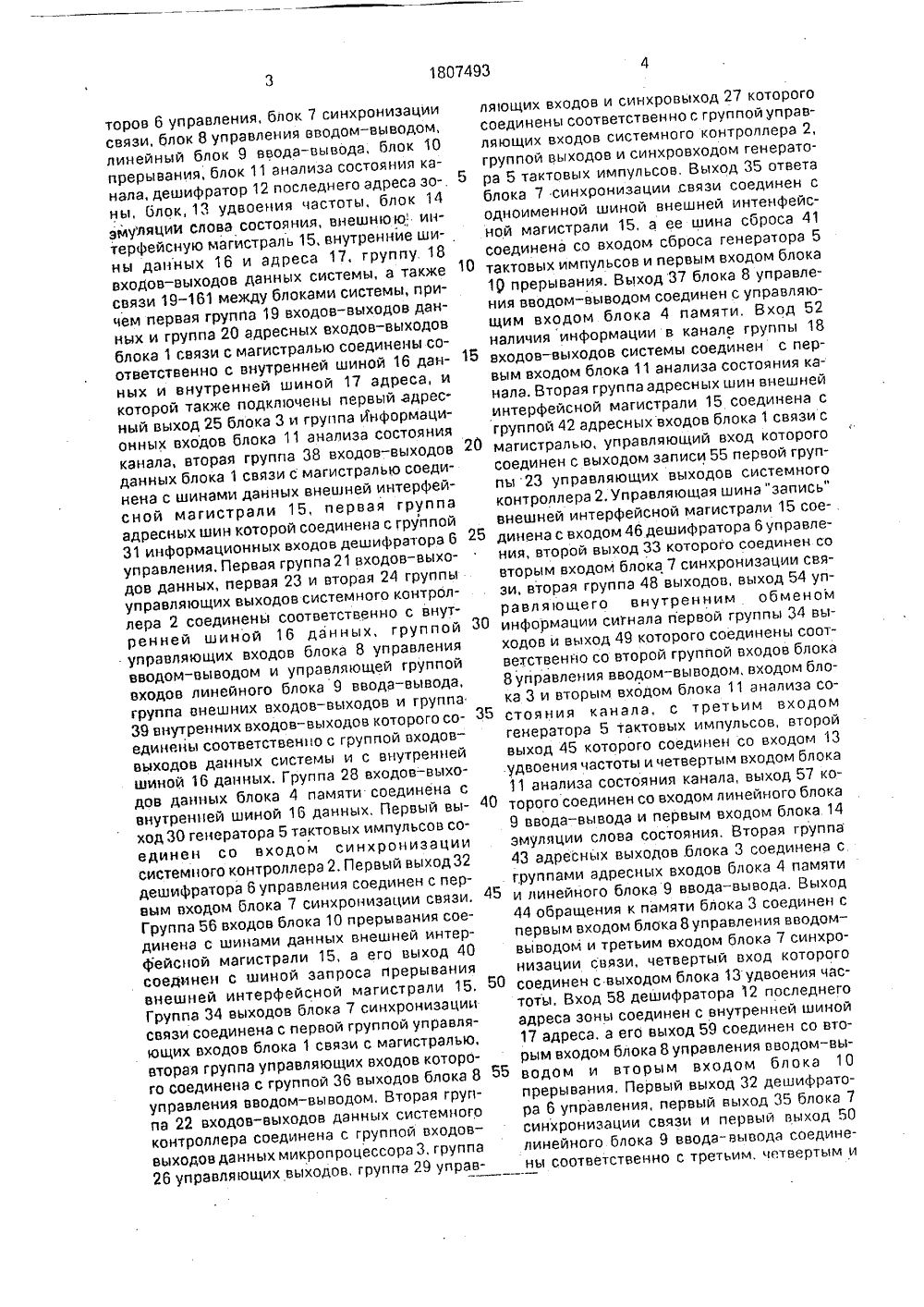

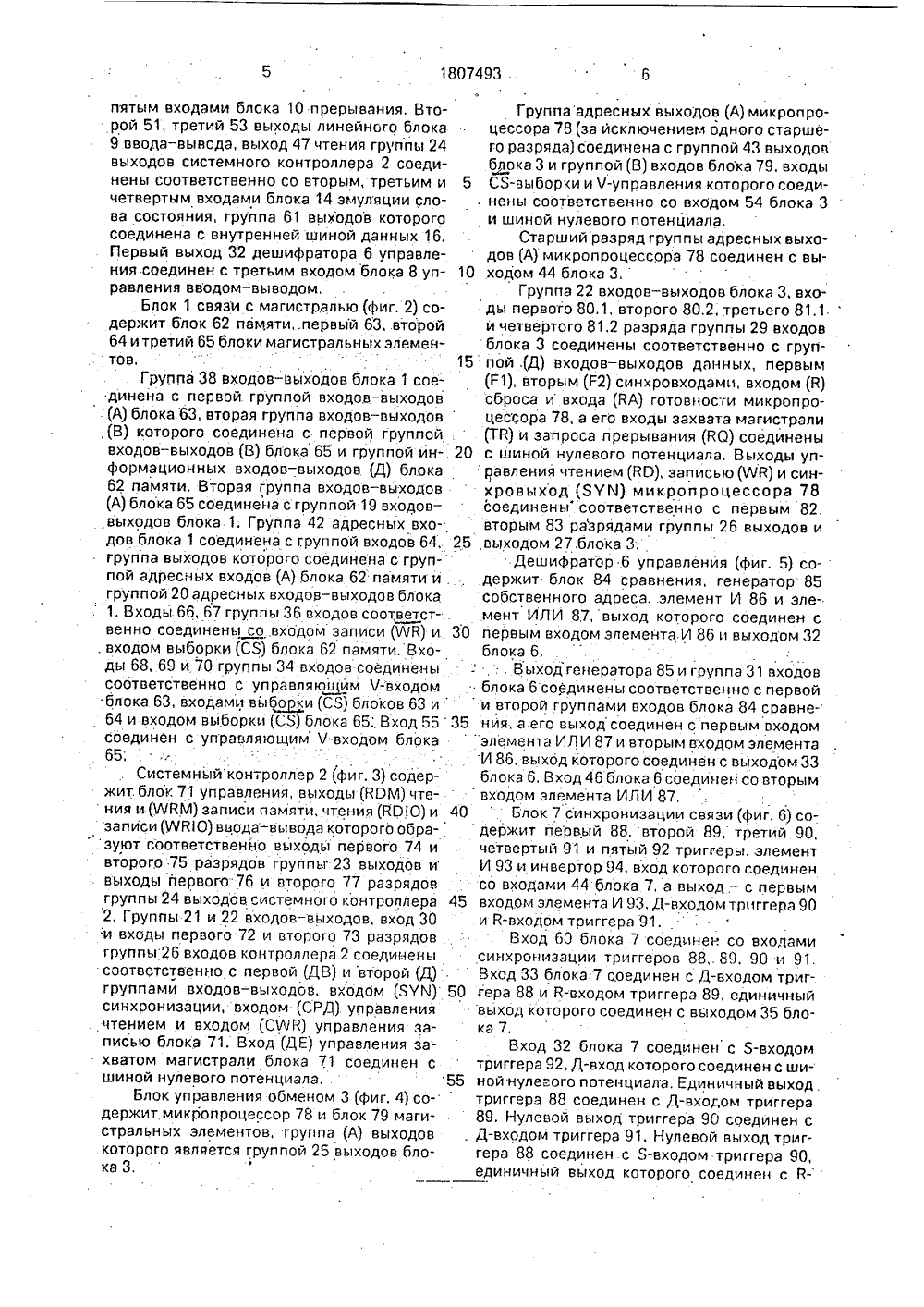

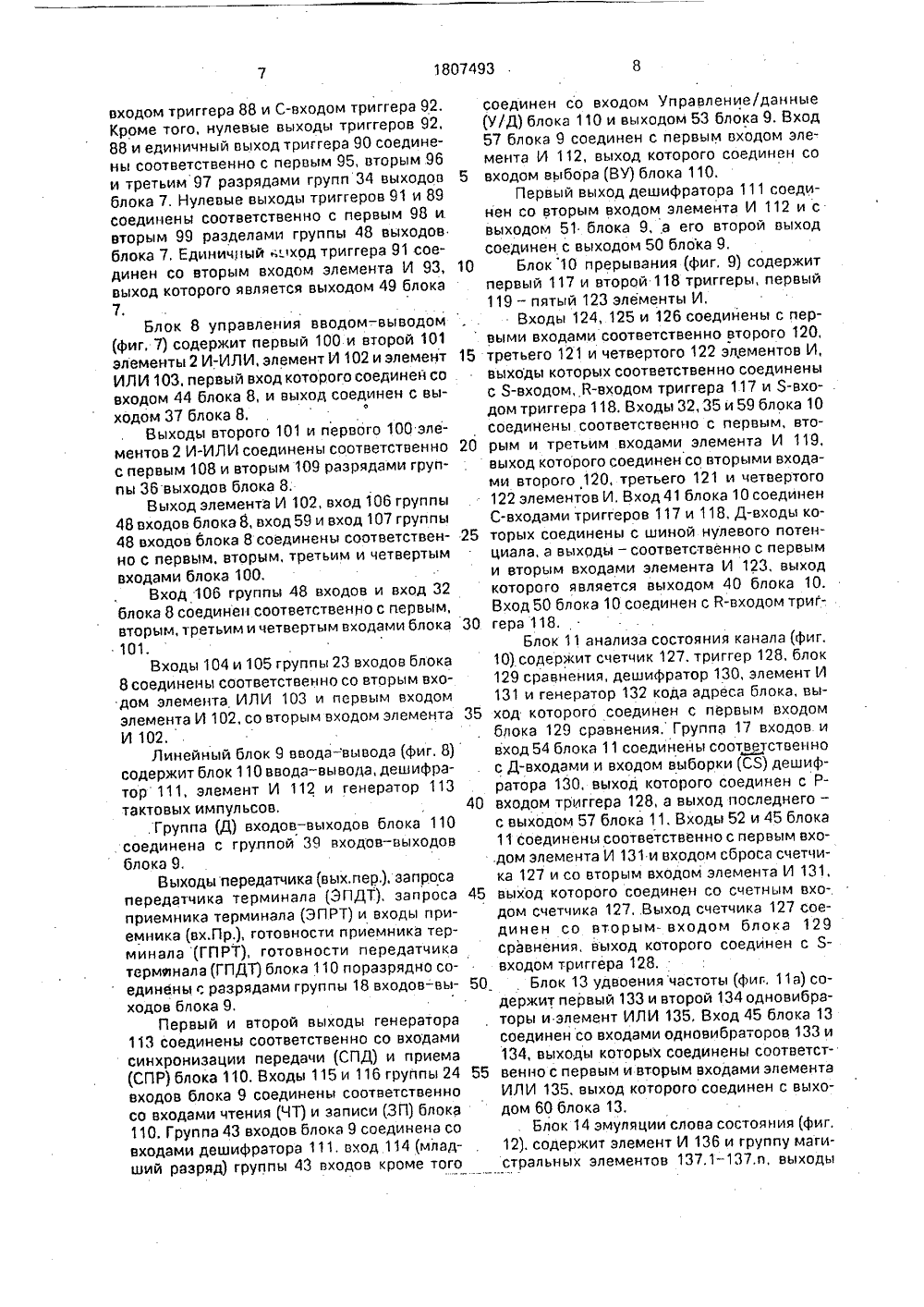

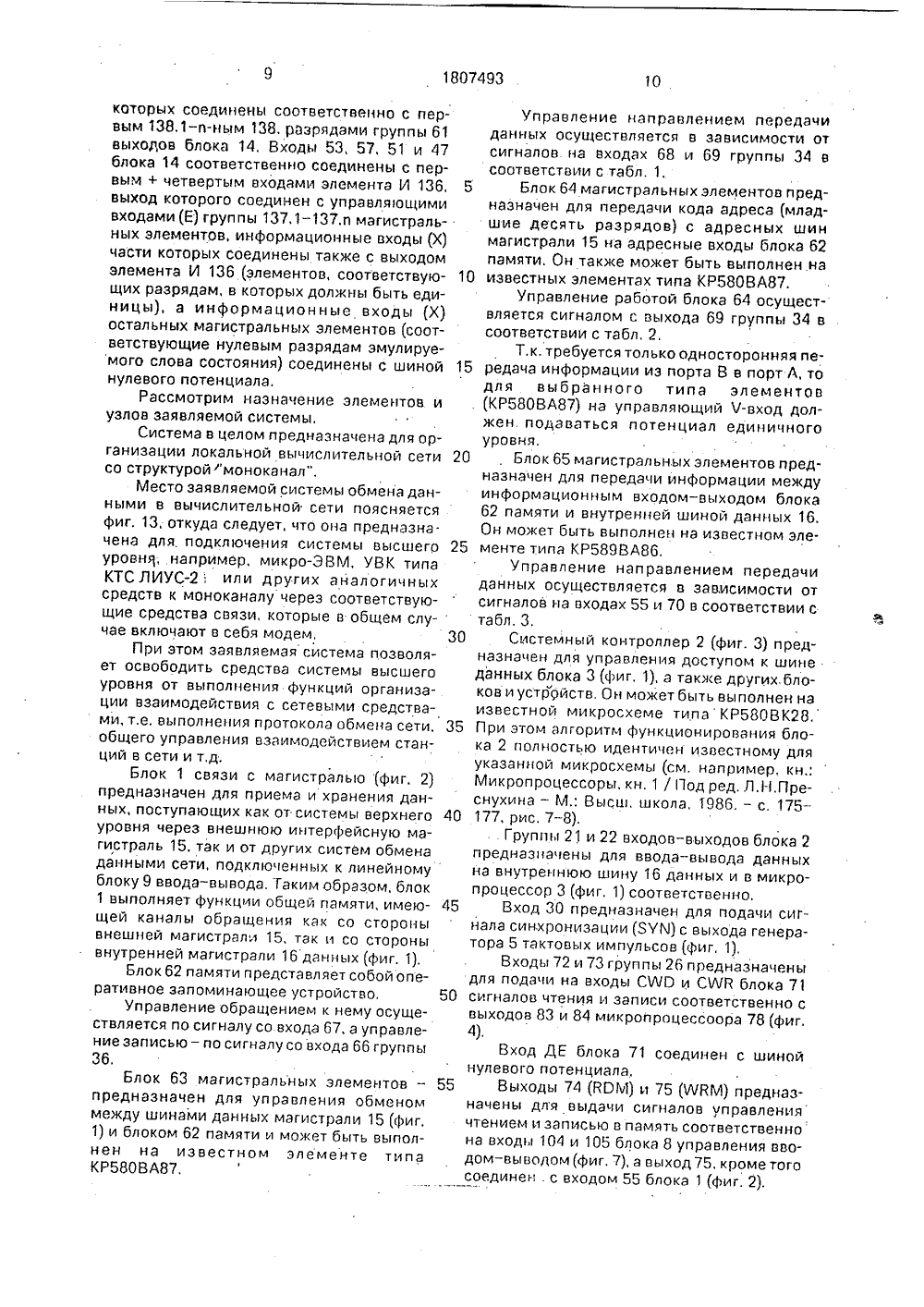

;,444 файф) ится к области выможет быть испольислительных сетях в на данными между ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(71) Харьковское научно-производственноеобьединение по системам автоматизированного управления(56) Авторское свидетел ьство СССРйт 756400, кл, 6 06 Р 13/00, 1977.Патент СШАМ 4156932, кл. 6 06 Р 3/04, 1979.Авторское свидетельство СССРМ 1432537, кл, 6 06 Р 13/12, 1988.(54) СИСТЕМА ОБМЕНА ДАННЫМИ В ВЫЧИСЛИТЕЛЬНОЙ СЕТИ(57) Изобретение отнчислительной техникизовано в локальных вькачестве системы обм Изобретение относится к области вычислительной техники и может быть использовано в локальных вычислительных сетях в качестве системы для обмена данными между локальными станциями и системами (процессорами) высшего уровня каждой локальной станции,Целью изобретения является повышение оперативности обмена информацией.На фиг, 1 приведена структурная схема заявляемой системы; на фиг, 2 - 12 - функциональные схемы блока связи с магистралью, системного контроллера, блока управления обменом, дешифратора управления, блока синхронизации связи, блока управления локальными станциями сети и системами (процессорами) высшего уровня каждой локальной станции, Цель изобретения - повышение оперативности обмена информацией. Сущность изобретения состоит в том, что совокупность конструктивных элементов и связей, реализованная в заявляемой системе обмена данными, позволяет повысить оперативность обмена информацией за счет сокращения непроизводительных затрат времени на передачу/возврат управления в сети, Система содержит блок связи с магистралью, системный контроллер, блок управления обменом, блок памяти, генератор тактовых импульсов, дешифратор управления, блок синхронизации связи, дешифратор последнего адреса зоны, блок управления вводом - выводом, линейный блок ввода - вывода, блок удвоения частоты, блок прерывания, блок анализа состояния канала, блок эмуляции слова состояния. 15 илб табл. вводом-выводом, линейного блока ввода- вывода, блока прерывания, блока анализа состояния канала, блока удвоения частоты и . блока эмуляции слова состояния; на фиг. 13приведен пример использования заявляемой системы в составе вычислительной сети; на фиг. 14 - схема алгоритма функционирования системы; на фиг, 15 - временные диаграммы основного командного цикла микропроцессора,Система обмена данными в вычислительной сети (фиг, 1) содержит блок 1 связи с магистралью, системный контроллер 2. блок управления обменом 3, блок 4 памяти, генератор 5 тактовых импульсов, дешифра10 15 20 30 35 50 за состояния канала связи (отсутствия передачи информации в нем в течение определенного интервала времени).Счетчик 127 предназначен для определения интервала времени. в течение которого по каналу связи не передается информация - канал не занят. На его счетный вход поступают импульсы с выхода элемента И 131, а обнуляется счетчик 127 единичным сигналом, поступившим на вход 52 (сигнал наличия информации в канале связи),Триггер 128 предназначен для формирования сигнала "ошибка" - фиксации признака окончания временного интервала ожидания передачи информации по каналу связи, В едиНичное состояние триггер 128 переходит по единичному сигнЪлу, поступившему на его Я-вход с выхода схемы 129 сравнения. а обнуляется единичным сигналом, поступившем на В-вход с выхода дешифратора 130, .Схема 129 сравнения служит для сравнения кодов, поступающих на его входы,При равенстве кода временного интервала,втечение которого канал связи оставался не занятым, и кода, задаваемого генератором 132 константы, на выходе схемы 129 сравнения формируется единичный сигнал.Дешифратор 130 служит для формирования сигнала сброса триггера 128. Сигнал, формируемый на выходе 97 группы 34 блока 7 (фиг, 6), поступает через вход 54 на управляющий вход (СЯ) дешифратора 130 (фиг. 10). Со входа 17 на информационный вход дешифратора 130 поступает код с шины 17 адреса.Элемент И 131 предназначен для управления счетчиком 127, Тактовые импульсы, поступающие на вход 45 блока 11, проходят на его выход при отсутствии информации в, канале связи (нулевой сигнал на входе 52 блока 11),Генератор 132 кода предназначен для задания кода временного интервала, в тече ние которого канал связи может оставаться не занятым. Этот временной интервал выбирается из расчета, что аналогичная система сати, получившая право на передачу,могла бы начать передачу (после окончания предыдущей передачи) и все остальные системы сети могли бы зафиксировать (услышать) факт начала передачи. Таким образом, отсутствие передачи информации в канале связи в течение времени, превышающего указанный интервал, свидетельствует о том, что система, получившая, право на занятие среды передачи, отказала.Дешифратор 12 (Фиг, 1) последнего адреса зоны предназначен для формирования управляющего сигнала при поступлении наего вход с шины 17 адреса кода последнегоадреса эоны. Этот адрес в предлагаемойсистеме закреплен за блоком 10 прерываний, что позволяет обращаться к блоку 10как к ячейке памяти.Преобразователь 13 частоты (фиг. 11, а)предназначен для формирования последовательности тактовых импульсов синхронизации блока 7 синхронизации связи путемудвоения частоты импульсной последовательности Р 2 ТТ, формируемой блоком 5 навыходе 45 (фиг 1)Основными элементами блока 13 являются одновибраторы 133 и 134 и элементИЛИ 135. Одновибраторы 133 и 134 могутбыть выполнены на известной микросхемеК 155 АГ 1 известным образом (см, Шило В,Л.Популярные цифровые микросхемы: Справочник - У Радио и связь, 1989 - стр, 188190), На фиг. 11, б приведена диаграммаработы блока 13,Блок 14 эмуляции слова состояния (фиг,12) предназначен для эмуляции слова состо- .яния линейного блока 9 ввода - вывода припревышении времени, в течение. которогоканал связи сети остается не занятым, заданного интервала ожидания (единичныйсигнал "ошибки" на выходе 57 блока 11, см.фиг, 1).Основные элементы блока 14 - элементИ,136 и группа 137.1 - 137.п магистральныхэлементов.Элемент И 136 формирует управляющий сигнал для группы 137 магистральныхэлементов. На его входы поступают сигналысо входов; 47 - сигнал Чтение (ЙО О) с вь 1 хода 76 группы 24 вьходов системного - контроллера 2 (см, фиг. 3)53 - сигналуправления управление / данные блока 110(см, фиг. 8), 51 - сигнал обращения к блоку110 и 57 - сигнал ошибки с выхода 57 блока11 (см, фиг. 10).При единиц,ных сигнала управление/данные и обращении к блоку 110 (фиг,8) для считывания слова состояния, а такженаличии единичного сигнала на выходе 57блока 11 (см. Фиг, 10) на выходе элемента И136 будет сформирован единичный сигнал.Группа 137.1-137. и магистральных элементов(и - разрядность эмулируемого слова состояния) служит для формирования слова состояния.Управляющие Е-входы элементов группы 137 соединены с выходом элемента И136. Информационные Х-входы элементов137 Л - которые соответствуют тем разрядамслова состояния, в которых должнь 1 бытьединицы, такжесоединены с выходом элемента И 136. Информационные входы осрый поступает на шину "ответа" магистрали 15 (фиг. 1) и информирует систему высшего уровня о том, что она получает доступ к памяти. На основании нулевого сигнала на 15 выходе 98 группы 48 выходов блока 7(фиг,6), который поступает на вход 106 группы 48 входов блока 8(фиг. 7), последний формирует нулевой сигнал на выходе 109 группы 36 выходов, который поступает через вход 67 20 группы 36 входов блока 1 (фиг. 2) на вход 25 30 35 50 55 тальных элементов группы 137 соединены сшиной нулевого потенциала. Выходы элементов группы 137 через группу выходов 61соединены с шиной данных 16.Примером эмулированного слова состояния может быть байт, биты ДО-Д 2 и Д 4 - Д 7которого равны нулю, а бит 13 равен единице, Этот бит в слове состояния микросхемыКР 580 ВВ 51 соответствует ошибке четности(см, Микропроцессоры и микропроцессорные комплекты интегральных микросхем,Справочник / Под ред, В,А.Шахнова, том 1,М. "Радио и связь", 1988, стр. 76) и в заявляемой системе может быть использован дляидентификации эмулируемого кода программного прерывания (слова состояния),т.к, проверка на четность не используется(см. описание блока 9),Таким образом, при обращении микропроцессора к блоку 9 ввода-.вывода для считывания его. слова состояния. при наличии.единичного сигнала на выходе 57 блока 11(фиг, 1), блок 14 сформирует код требуемогослова состояния на шину данных 16 (одновременно будет заблокировано считываниеслова состояния из блока 110, см. фиг, 8 иописание работы блока 9).Интерфейсная магистраль 15 предназначена для организации обмена данными. а.также адресными и управляющими сигналами между заявляемой системой и системойвысшего уровня, подключаемой к вычисли, тельной сети (фиг. 13).Она сожет быть построена в соответствии с известным интерфейсным протоколомИК 1 (см, кн. Диденко К,И, Проектированиекомплексов технических средств для АСУТП. - М: Э нергоатомиздат, 1984, с. 112-123)и содержиттри группы шин; данных, адресаи управляющие; 4Шины 16 и 17 (фиг, 1) предназначеныдля обмена данными и адресной информацией внутри заявляемой системы.Обращение к заявляемой системе приобмене данными с ней со стороны системы 4высшего уровня, например, вычислительной машины (сьев. фиг. 13), осуществляетсячерез интерфейсную магистраль 15 (фиг, 1) всоответствии с известным протоколом ИК 1.. При этом формат адреса при обращении к системе со стороны магистрали 15следующий (см, табл, 4).Запись (чтение) информации в (из) блок62 памяти (фиг, 2) осуществляется следующим образом,Для чтения содержимого блока 62 поадресу(Лбаз+Адоп), на вход 31 блока б(фиг.5) поступает код Абаз, а на вход 42 блока 1(фиг, 2) поступает код Адоп.1 В результате на выходе 33 блока 6 (фиг.5) формируется единичный сигнал, который поступает на вход 33 блока 7 (фиг,б),Блок 7, проведя арбитраж между внутренним микропроцессором и внешней системой, на основании этого сигнала формирует единичный сигнал на выходе 95 и нулевой сигнал на выходе 96 группы выходов 34 нулевой сигнал на выходе 98 группы 48 и единичный сигнал на выходе 35, котоОЗУ 62 и разрешает его работу.Нулевой сигнал с выхода 96 группы 34 выходов блока 7 (фиг. 6) поступает через вход 69 группы 34 входов блока 1 (фиг. 2) на СЯ-входы шинных формирователей 63 и 64,разрешая их работу.,Единичный сигнал с выхода 95 группы 34 выходов блока 7 (фиг. 6) поступает через вход 68 группы 34 входов блока 1 (фиг. 2) на Ч-вход шинного формирователя 63, определяя направление передачи информации спорта В в порт А.Таким образом код Адоп, поступив смагистрали 15 (фиг, 1) на вход 42 блока 1(фиг. 2), поступит на адресный вход блока 62 а информация, считанная из блока 62 по адресу Адоп, поступит через шинный формирователь 63 и выход 38 блока 1 на шинуданных магистрали 15 (фиг, 1),Для записи информации о блок 62 фиг 2) по адресу (Абаз + Адоп) с магистрали 15(фиг, 1) на вход 31 блока б (фиг. 5) поступаеткод Абаз, а на вход 42 блока 1 (фиг. 2) поступает код Адоп. В результате блоками 6 (фиг. 5), 7 (фиг 6) и 8 (фиг. 7) формируются сигналы, аналогичные описанным для чтения информации из блока 62 (фиг. 2).Отличие заключается.в том, что после получения сигнала "ответ" (с выхода 35 блока 7, фиг. 6) системз высшего уровня формирует на шине управления магистрали 15 (фиг, 1) нулевой сигнал "запись", который поступает на вход 46 блока б (фиг. 5), который сформирует нулевой сигнал на своем выходе 32, который поступит на вход 32 блока 7 (фиг. 6) и переведет триггер 92 в единичное состояние. В результате, на выходе 95 группы 34 выходов блока 7(фиг, б) сигнал с единичногоизменится на нулевой и шинный формирователь 63 блока 1 (фиг. 2) окажется настроенным на передачу информации с порта А в порт В, т.е. с шины данных магистрали 15 (фиг, 1) на О-вход блока 62 (фиг. 2),Кроме того, нулевой сигнал с выхода 32 блока 6 (фиг. 5) поступит на вход 32 блока 8 (фиг. 7) и последний сформирует на своем выходе 108 группы 36 выходов нулевой сигнал, который через вход 66 группы 36 входов блока 1 (фиг, 2) поступит на И/В-вход блока 62,В результате информация, поступившая с шины данных 15 (фиг. 1) на О-входблока 62 (фиг. 2) запишется в него по адресу Адоп;Таким образом, обмен массивами данных между системой высшего, уровня и заявляемой системой осуществляетсяпобайтно в соответствии с описанным выше алгоритмом,Запись информации в регистр (триггеры 117 и 118) блока 10 прерьваний (фиг. 9) осуществляется так же, как и в память. Дляэтого система высшего уровня обращаетсяк заявляемой системе по адресу (Абаз + Адоп.паз), где Адоп,паз - последний адрес зоны.Адоп,паз - поступит через выход 20 блока 1 (фиг. 2) на внутреннюю шину 17 адреса и далее на вход 58 дешифратора 12 последнего адреса зоны (фиг. 1) который сформирует на своем выходе 59 единичный сигнал, который блокирует формирование разрешающего СЯ-сигнала управления блоком 9 (фиг, 7)для блока 62 (фиг. 2).Запись информации, поступающей с шины данных магистрали 15 (фиг. 1) на вход 56 блока 10 (фиг. 9) в триггеры 117 и 118 осуществляется при наличии трех сигналов: единичного сигнала - "ответ" на выходе 35 блока 7 (фиг. 6), единичного сигнала на выходе 59 дешифратора 12 последнего адреса зоны и нулевого сигнала "запись" на выходе 32 блока 6 (фиг. 5). При этом используются значения сигналов разрядов ДО-Д 2 в соответствии со следующей табл. 5,Блок 62 памяти (фиг. 2) условно подразделяется на несколько зон, распределение информации по которым может быть, например, следующим;- зона конфигурации вь 1 числительной сети, включающая список адресов систем для обмена, аналогичных заявляемой, которые подключаются к локальной вычислительной сети,- Байт состояния передачи, содержащий информацию о коде выполняемой фун- кции (биты ДО - ДЗ), признак неответа канала связи (Д 4), признак занятости кана 10 15 20 30 35 40 45 5055 ла связи (Д 5), признак сбоя в канале (Д 6),признак выполнения функции (Д 7).Разряды ДО-ДЗ используются для задания функции запись (код 0001), остальныекоды не задействованы. Установка кодафункции осуществляется с магистрали 15(ноль) системой в случае отсутствия ответаот адресуемой станции, после трехкратногоповторения обращения к ней (сбрасываетсясистемой высшего уровня через магистраль15).Разряд Д 5 устанавливается системой вслучае занятости буфера приема у абонента,сбрасывается через магистраль 15.Разряд Д 6 устанавливается системойпри неполучении от адресуемой станцииподтверждения (поступает другой код) после трехкратного повтора передачи функции Запись. Сбрасывается со сторонымагистрали 15.Разряд Д 7 устанавливается через магистраль 15 после записи массива данных вбуфер передачи блока 62 (фиг. 2). Сброс Д 7осуществляется после выполнения функцииЗапись, При этом в зависимости от результата выполнения функции запись разряд Д 7может быть сброшен, а разряды Д 4 - Д 6 неустановлены, (если функция запись выполнена правильно), в противном случае разрядД 7, сброшен, а установлен один из разрядовД 4 - Д 6 в зависимости от причины невыполнения функции запись,- Байт состояния приема, содержащийинформацию о коде выполняемой функции(биты ДО-ДЗ) и признаке завершения приема информации из канала связи (Д 7), остальные биты Д 4 - Д 6 не используются.Функция запись имеет код 0001, Разряд Д 7устанавливается системой после приема сообщения из канала связи, а сбрасывается состороны магистрали 15 послеосвобожде"ния приемного буфера,- Байт состояния завершения приема,содержащий информацию о признаке "Молчания" канала(бит ДО), признаке неправильного приема (Д 1) и признаке приемаинформации в дополнительный буфер(Д 2),остальные разряды ДЗ - Д 7 не используются. Установка битов ДО-Д 2 осуществляетсяпри выполнении системой подпрограммыприема,- Зона рабочих ячеек памяти используется системой для выполнения основныхфункций, определения статуса инициативной управляющей системы и других операций,- Собственный адрес системы записывается системой в блок 62 (фиг, 2) в начале(фиг. 1) 30 35 45 50 55 выполнения программы в соответствии с кодом, генерируемым блоком 86 (фиг, 5) изПЗУ 4 (фиг, 1),- Байт логического таймера, в началевыполнения программы в него системой заносится собственный номер данной системы в сети, в дальнейшем код в этом байтеизменяется системой в соответствии с правилом ЛТ =.ЛТ+ 1 ы (где й - число абонентов сети, а .)Й - операция по модулю й),при получении системой маркера (или приэмуляции слова состояния блока 9 блоком14). Равенство кода логического таймера нулю дает право системе перейти к выполнению программы "Инициативнаяуправляющая система",- Байт числа станций в сети, в началепрограммы в него системой заносится кодчисла й развернутых систем в сети каналов(аналогичных заявляемой), в дальнейшем,при отказе какой-либо из станций изменяется системой в соответствии с правилом,- Байт числа сеансов в сети, в началепрограммы в него записывается код М числасеансов, которые должны быть проведены всчети, в дальнейшем после каждого сеанса(получен маркер, либо сеанс не состоялся -слово состояния блока 9 сэмулировано блоком 14). Код уменьшается на единицу М = М- 1. При равенстве кода нулю система выставляет флаг Установка исходного.- флаг установка исходного, устанавливается системой при обнулении кода числасеансов (см, выше), Кроме того, флаг "установка исходного" может быть установленсистемой высшего уровня (такая установкаиспользуется для инициализации сети), через магистраль 15. Установленный флагпредписывает системе при получении правана передачу (переход к выполнению программы "Инициативная управляющая система") передать сетевую функциюустановка исходного, сбрасывается системой после передачи этой функции, либо приприеме этой функции от аналогичных систем сети,- Флаг блокировка устанавливается припоступлении сигнала сброса со стороны магистрали 15, сбросфлага блокировка осуществляется при передаче (приеме) сетевойфункции установка исходного, кроме тогосброс может быть осуществлен системойвысшего уровня через магистраль 15 (используется при инициализации сети).- Буфер сообщения для передачи в канал связи, используется для записи в блок62 (фиг. 2) со стороны магистрали 15 сообщения, предназначенного для передачи надругую станцию. В буфер записывается адФ рес станции назначения, длина сообщения и текст сообщения.Основной и дополнительный буферы приема из канала связи, предназначены для приема сообщений от других станций.При обмене данными между станциями локальной сети (фиг. 13) в системе реализуется интерфейс ИМР (см. ГОСТ 26139-84 интерфейс для АСУ рассредоточенными обьектами) - бит-последовательный обмен данными по линиям связи.При этом передача сообщений между локальными станциями осуществляется посредством ограниченного набора байтов, порядок следования которых устанавливается форматом сообщения.Для протокола 30 С установлены два типа форматов; форма 1 и 2. В целом же следует заметить, что алго 20 ритм органиэации обмена данными между заявляемой системой и другими элементами вычиСлительной сети определяется программой, которая хранится в блоке 4 памяти 25 При этом характеристики алгоритма об. мена, определяемые протоколом обмена,форматами сообщений, способами формирования служебной информации (синхробайтов), контрольных битов и тгд.) и другими атрибутами могут варьироваться программно без изменения структуры техническихсредств системы,Система может выполнять несколько сетевых функций, код которых задается в формате сообщения байтом, содержащим информацию о виде сообщения (бит О, вызов-ответ), признаке занятости локальной станции (бит 1), типе формата сообщения(биты 4-7). Коды сетевых функций могут задаваться, например, следующей табл. 6,Кроме того, в системе для передачи управления используется уникальная комбинация (1 байт), например 01111111,маркер.Обмен сообщениями между локальными станциями в сети организован в виде сеансов, под которыми понимается процедура передачи в канал связи одного сообщения. Процесс передачи организуется по асинхронному принципу, поэтому на посылаемые в канал связи вызовы система должна получать ответы.Процедура проведения сеанса реализована в заявляемой системе в соответствии с . известным протоколом ЯОМС (см. Дж.Мартин. "Вычислительные сети и распределенная обработка данных, Программное обеспечение, методы и архитектура". Вып. 2 /Пер, с англ., - М "финансы и статистика",1986 и др, источники), В соответствии с протоколом ЯО.С при получении права на проведение сеанса система осуществляетсеанс и затем передает маркер, или еслиинформация для передачи в канал связи отсутствует, передает только маркер.Отличие протокола, используемого в системе, от протокола (который предназначендля кольцевых ЛВС) заключается в том, чтоон адаптирован под шинную топологию и вотсутствии главной системы в сети.Адаптация заключается в введении механиэма определения права системы напроведение сеанса, который основан на использовании логического таймера (реализованного в системе программно) имзаключается в следующем:20- в исходном состоянии в логическийтаймер заносится номер системы в сети;- после каждого сеанса, проведенногов сети (т.е, получен маркер), значение логического таймера изменяется по правилуЯТ= 25= ЛТ+ 1 й, где 1 Й - сложение по модулюй; Й - число станций в сети;- право на проведение сеанса система.получает, если ее логический таймер равеннулю.:30Таким образом, в силу полнодоступности передаваемой в сети информации всемсистемам, их логические таймеры будут изменять свое состояние по одним и тем жесигналам (макерам) и, следовательно, право 35на проведение сеанса будет получать только одна система в сети,Система, не обладающая правом напроведение сеанса, является управляемойподсистемой сети, в этом состоянии осуществляется прием адресованных системе сообщений и, формирование ответныхсообщений в соответствии с кодом реализуемой сетевой функции.При получении права на проведение сеанса система переходит в состояние инициативной управляющей подсистемы. В этомсостоянии система может осуществить передачу сообщения, принимать и анализировать ответные сообщения, и, по окончании 50сеанса, передать маркер,Таким образом, право на проведение сеанса передается очередной системе, а отказавшая (или отключенная система) исключается из цикла обслуживания. Кроме того, указанная процедура позволяет корректи- ровать информацию о конфигурации сети (а при инициализации сети формировать ее, исходя из максимально возможной) во всех системах сети, не прибегая к помощи систем высшего уровня или централизованному управлению.Для вхождения в работу сети вновьвключенных (отремонтированн ых) систем используется следующий механизм.При включении системы формируетсясигнал сброса со стороны системы высшего уровня, по которому система отрабатывает подпрограмму установки исходного и, кроме того, устанавливается флаг блокировка.При установленном флаге блокировка блокируется переход к выполнению программы "инициативная управляющая подсистема" и происходит изменение логического таймера данной системы, система способна прини-.мать информацию из канала связи и анализировать ее. 55 Для обеспечения отказоустойчивости сети каждая система прослушивает канал связи и анализирует его состояние. При отсутствии в нем передачи информации (канал свободен) система запускает контрольный таймер с заданным временем срабатывания, который обнуляется при очередном занятии канала связи, Срабатывание таймера свидетельствует о том, что система, получившая право на проведение сеанса (или система, которая должна была получить это право), либо отказала, либо отключена. В результате срабатывания контрольного таймера происходит эмуляция слова состояния приемопередатчика 9 блоком 14, что приводит к программному прерыванию микропроцессора 3. Данное прерывание обрабатывается следующим образом:- определяется номер отказавшей системы:- корректируется конфигурация сети (в соответствующей зоне блока 62 памяти, фиг. 2);-уменьшается на единицу число М станций в сети (соответствующий байт в блоке 62 памяти, фиг. 2);- далее выполняется подпрограмма, реализуемая при получении системой маркера. В каждой системе, работающей в рамках сети, программно поддерживается счетчик числа сеансов, проведенных в сети (соответствующий байт в блоке 62 памяти, фиг. 2). При его обнулении выставляется флаг установка исходного и при очередном получении данной системой права на проведение сеанса, она передает с циркулярным адресом сетевую функцию КФ 6 (установка исходного).В результате все включенные и работоспособные системы сети устанавливают в исходное состояние:- байт логического таймера (код номера системы); 5- байт числа станций в сети (код М);- байт числа сеансов в сети (код М);- сбрасывается флаг блокировка;- сбрасывается флаг установка исходного, 10Далее сеть функционирует аналогично описанному вышеАлгоритм работы заявляемой системы представлен на фиг. 14,Основными режимами работы заявляе мой системы являются режимы:- начального запуска;- передачи-приема данных.Рассмотрим режим начального запуска.В этот режим система переходит при 20 поступлении сигнала установки с шины 41 магистрали 15 (фиг. 1) от системы высшего уровня;При поступлении сигнала со входа 41 25 генератор 5 вырабатывает сигнал начальной установки, который поступает на вход сброса 811 (фиг. 4) микропроцессора 78. После этого последний переходит к реализации программы начального запуска: в 30 блок 62 (фиг. 2) заносится конфигурация сети (все существующие станции), устанавливается флаг блокировка, заносятся соотЬетствующие коды в байт логического таймера, в байт числа станций в сети, в байт 35 числа сеансов в сети и др,При этом программно блокируется обработка маркеров (т.е. заблокирован логический таймер), поступающих в систему из канала связи, остальные сообщения прини маются и анализируются.Благодаря указанной блокировке заявляемая система может войти в уже функционирующую сеть, не нарушая ее работы, а также обеспечивает начальную инициали зацию сети в целом.При вхождении заявляемой системы в работающую сеть она ожидает получения сетевой функции КФ 6 (установка исходного). При получении функции КФ 6 система 50 сбрасывает флаг блокировка и в дальнейшем функционирует в соответствии с алгоритмом, изображенным на фиг. 14.При инициализации сети после включения систем, аналогичных заявляемой, все 55 они оказываются заблокированными - установлен флаг блокировка.Инициализация сети осуществляетсяодной из систем высшего уровня. Для этого она обращается через магистраль,15 и сопряженной с ней системе обмена данными (см. фиг. 13) и выставляет в ее блоке 62 (фиг.2) флаг установка исходного, после этого сбрасывает флаг блокировка.Данная система обмена информации оказывается разблокированной - ее блок 11 анализа состояния канала (фиг. 1) формирует на своем выходе 57 сигналы "ошибки" (т.к. канал связи свободен), на основании которых блок 14 эмулирует на своем выходе 61 слово состояния блока 9, которое приводит к программному прерыванию микропроцессора 3, и он корректирует в блоке 62 (фиг. 2) байт логического таймера в соответствии с указанным ранее правилом. По достижению значения логического таймера нулю, данная система обмена данными формирует и посылает в канал связи циркулярное сообщение с сетевой функцией КФ 6 (установка исходного),В результате все системы обмена данными(включая и переданную функцию КФ 6) сбрасывает байт блокировка и производят операции в соответствии с принятой функцией и переходят к выполнению алгоритма работы, представленного на фиг. 14.Таким образом осуществляется начальная инициализация сети в целом.Рассмотрим режим приема-передачи данных.Перед, передачей данных в канал связи осуществляется проверка готовности системы к передаче. При этом система считается готовой к передаче, если в байте состояния передачи в блоке 62 (фиг, 2) разряд Д 7- О.Если передача данных в канал связи осуществляется с магистрали 15 (фиг. 1), то в блок 62 (фиг, 2) записываются адрес абонента назначения, длина сообщения и его текст. После этого в байт состояния передачи записывается код, который является признакол 1 задания системе выполнения функции запись. Система начинает передачу сообщения в канал связи после обнуления логического таймера.После передачи сообщения в канал связи система переходит в состояние ожидания ответа. При отсутствии ответа от абонента осуществляется повторная передача сообщения с последующим переходом в состояние ожидания ответа, Повтор передачи может быть произведен трехкратно,Если в состоянии ожидания ответа принимается информация с кодол 1 функции КФ 18 (подтверждение приел 1 а), система осуществляет сброс бита Д 7 в байте состояния передачи и передает в канал связи маркер (01111111),10 15 20 30 35 40 45 50 Любая система, входящая в сеть, осуществляет анализ информации, циркулирующей в канале связи, с целью обнаружения адресованного ей сообщения. После выбора;адресованного сообщения система контролирует правильность приема сообщения и кода функции, При неправильном приеме информации система переходит к выполнению программы анализа состояния канала связи (прослушивание канала),Если же информация принята правильно и получено сообщение с кодом функции запись, то система осуществляет передачу в канал ответного сообщения с кодом функции КФ 18 и формирует сигнал запроса прерывания блоком 10 (фиг. 9). После выполнения этих операций система переходит к программе анализа состояния канала связи.Если буфер приема из канала связи. занят, то система передает в канал связи ответное сообщение - код функции Кф 18 с признаком занятости и переходит к программе анализа состояния канала связи,При принятии системой маркера она корректирует значение своего логического таймера и проверяет его на равенство нулю. Если значение логического таймера равно нулю, то система переходит к,выполнению программы Инициативная управляющая подсистема" (т.е, получает право,на проведение сеанса), в противном случае - переходит к программе анализа состояния канала связи,При отсутствии информации в канале связи в течение интервала времени больше заданного (т.е. система, получившая право на проведение сеанса, не работает: отказала либо отключена) блок 11 анализа состояния канала (фиг. 1) формирует на своем выходе 57 сигнал ошибки, по которому блок 14 эмулирует и при очередной попытке микропроцессора 3 считает слово состояния блока 9, выдает нэ внутреннюю шину 16 данных код программного прерывания.Обработка данного прерывания микропроцессором заключается в том, что он сбрасывает триггер 128 (фиг, 10), определяет таймер отказавшей системы, и корректирует в блоке 62 (фиг. 2) информацию о конфигурации сети, изменяет значение байта числа станций в сети (Н = й - 1) и дальше выполняет операции как при приеме системой маркера.Формула изобретения Система обмена данными в вычислительной сети, содержащая блок связи с магистралью, системный контроллер, блок управления обменом, блок памяти, генератор тактовых импульсов, дешифратор управления, блок синхронизации связи, блок управления вводом - выводом, линейный блок ввода-вывода. блок прерывания, блок анализа состояния канала, причем первая группа входов-выходов данных и группа адресных входов - выходов блока связи с магистралью соединены соответственно с внутренней шиной данных и внутренней шиной адреса системы, к которой также подключены первый адресный выход блока управления обменом и группа информационныхвходов блока анализа состояния канала, вторая группа входов - выходов данных блока связи с магистралью соединенэ с шинами данных внешней интерфейсной магистрали системы, первая группа адресных шин которой соединена с группой информационных входов дешифраторэ управления, первая группа входов - выходов данных, первая и вторая группы управляющих выходов системного контроллера соединены соответственно с внутренней шиной данных системы, группой управляющих входов блокауправления вводом - выводом и управляющей группой входов линейного блока ввода - вывода, группа внешних входов-выходов и группа внутренних входов-выходов которого соединены соответственно с группой входов - выходов данных и с внутренней шиной данных системы, группа входов - выходов данных блока памяти соединена с внутренней шиной данных системь 1, первый выход генератора тактовых импульсов соединен с входом синхронизации системного контроллера, первый выход дешифратора управления соединен с первым входом блока синхронизации связи, группа входов блока прерывания сОединена с шинами данных внешней интерфейсной магистрали системы, а его выход соединен с шиной запроса прерывания внешней интерфейсной магистрали системы, группа выходов блока синхронизации связи соединена с первой группой управляющих входов блока связи с магистралью, вторая группа управляющих входов которого соединена с группой выходов блока управления вводом в вывод, вторая группа входов-выходов данных системного контроллера соединена с группой входов-выходов данных блока управления обменом, группа управляющих выходов, группа управляющих входов и синхровыход которого соединены соответственно с группой управляющих входов системного контроллера, группой выходов и синхровходом генератора тактовых импульсов, выход ответа блока синхронизации связи соединен с одноименной шиной внешней интерфейсной магистрэли системно а ее шина сброса соединена,с входом сброса генератора тактовых импульсов и первым входом блока прерывания, выход блока управления вводом - выводом соединен с управляющим входом блока памяти, вход наличия информации в канале группы входов - выходов данных системы соединен с первым входом блока анализа состояния канала, о т л и ч а ющ э я с я тем, что, с целью повышения оперативности обмена информацией, система содержит дешифратор последнего адреса зоны, блок удвоения частоты и блок эмуляции слова состояния, причем вторая группа адресных шин внешней интерфейсной магистрали системы соединена с группой адресных входов блока связи с магистралью, управляющий вход которого соединен с выходом записи первой группы управляющих выходов системного контроллера, управляющая шина "Запись" внешней интерфейсной магистрали системы соединена с входом дешифратора управления, второй выход которого соединен с вторым входом блока синхронизации связи, вторая группа выходов, выход управления внутренним обменом первой группывыходов и выход готовности которого соединены соответственно с второй группой входов блока управления вводом - выводом, управляющим входом блока управления обменом и вторым входом блока анализа состояния канала и с третьим входом генератора тактовыхимпульсов, второй выход которого соединен с входом блока удвоения частоты и четвертым входом блока анализа состояния канала, выход которого соединен с входом линейного блока ввода - вывода и первым входом блока эмуляции слова состояния, 5 вторая группа адресных выходов блока управления обменом соединена с группами адресных входов блока памяти и линейного блока ввода - вывода, выходобращения к памяти блока управления обменом соединен с 10 первым входом блока управления вводомвыводом и третьим входом блока синхронизации связи, четвертый вход которого соединен с выходом блока удвоения частоты, групповой вход дешифратора последне го адреса зоны соединен с внутреннейшиной адреса системы, а его выход соединен с вторым входом блока управления вводом - выводом и вторым входом блока прерывания, первый выход дешифратора 20 управления, выход ответа блока синхронизации связи и первый выход линейного блока ввода - вывода соединены соответственно с третьим, четвертым и пятым входами блока прерывания, второй, 25 третий выходы линейного блока ввода - вывода, выход чтения группы выходов системного контроллера соединены соответственно с втОрым, третьим и четвертым входами блока эмуляции слова состоя ния, группа выходов которого соединена свнутренней шиной данных системы, первый выход дешифратора управления соединен с третьим входом блока управления вводом - ВЫВОДОМ.1807493 Таблица 4 Таблица 5 а бди и м е ч а н и е. " Х" - безразличное состояние; - остальные 29 кодов (из 32 возможных) функций являются резервньми и в рассматриваемом примере не используютляющих входов и синхровыход 27 которого соединены соответственно с группойуправляющих входов системного контроллера 2, группой выходов и синхровходом генератора 5 тактовых импульсов, Вь 1 ход 35 ответа блока 7 синхронизации .связи соединен с одноименной шиной внешней интенфейсной магистрали 15, а ее шина сброса 41 соединена со входом сброса генератора 5 тактовых импульсов и первым входом блока 1 Д прерывания. Вь 1 ход 37 блока 8 управления вводом-выводом соединен с управляющим входом блока 4 памяти. Вход 52 наличия информации в канале группы 18 входов-выходов системы соединен с первым входом блока 11 анализа состояния канала, Вторая группа адресных шин внешней интерфейсной магистрали 15 соединена с группой 42 адресныхвходов блока 1 связи с магистралью, управляющий вход которого соединен с выходом записи 55 первой группы 23 управляющих вь 1 ходов системного контроллера 2. Управляющая шина "запись" внешней интерфейсной магистрали 15 сое- .динена с входом 46 дешифратора буправления, второй выход 33 которого соединен со вторым входом блока 7 синхронизации связи, вторая группа 48 выходов, вь 1 ход 54 управляющего внутренним обменом информации сигнала первой группы 34 выходов и выход 49 которого соединены соответственно со второй группой входов блока 8 управления вводом-выводом, входом блока 3 и вторым входом блока 11 анализа со стояния канала, с третьим входомгенератора 5 тактовых импульсов, второй выход 45 которого соединен со входом 13 .удвоения частоты и четвертым входом блока 11 анализа состояния канала, выход 57 ко торого соединен со входом линейного блока9 ввода - вывода и первым входом блока 14 эмуляции слова состояния. Вторая группа 43 адресных выходов .блока 3 соединена с.группами адресных входов блока 4 памяти 5 и линейного блока 9 ввода-вь 1 вода. Выход44 обращения к памяти блока 3 соединен с первым входом блока 8 управления вводом - выводом и третьим входом блока 7 синхронизации связи, четвертый вход которого 0 соединен с выходом блока 13 удвоения частоты, Вход 58 дешифратора 12 последнего адреса зоны соединен с внутренней шиной 17 адреса, а его выход 59 соединен со вторым входом блока 8 управления вводом-выводом и вторым входом блока 10 прерывания, Первый выход 32 дешифратора 6 управления, первый вь 1 ход 35 блока 7 синхронизации связи и первый выход 50 линейного блока 9 ввода-вывода соединены соответственно с третьим, четвертым и торов 6 управления, блок 7 синхронизации связи, блок 8 управления вводом-выводом, линейный блок 9 ввода-вывода, блок 10 прерывания, блок 11 анализа состояния канала, дешифратор 12 последнего адреса зо-. 5 ны, блок, 13 удвоения частоты. блок 14 эмуляции слова состояния, внешнюю, интерфейсную магистраль 15, внутренние шины данных 16 и адреса 17, группу. 18 входов-выходов данньх системы, а также 010 связи 19-161 между блоками системы, причем первая группа 19 входов - выходов данных и группа 20 адресных входов-выходов блока 1 связи с магистралью соединены соответственно с внутренней шиной 16 данных и внутренней шиной 17 адреса, и которой также подключены первый адресный выход 25 блока 3 и группа информационных входов блока 11 анализа состояния канала, вторая группа 38 входов-выходов 20 данных блока 1 связи с магистралью соединена с шинами данных внешней интерфейсной магистрали 15, первая группа адресных шин которой соединена с группой 31 информационных входов дешифратора 6 25 управления, Первая группа 21 входов-выходов данных, первая 23 и вторая 24 группы управляющих выходов системного контроллера 2 соединены соответственно с внутренней шиной 16 данных, группой 30 управляющих входов блока 8 управления вводом-выводом и управляющей группой входов линейного блока 9 ввода-вывода, группа внешних входов - выходов и группа 39 внутренних входов-выходов которого со единены соответственно с группой входов- выходов данных системы и с внутренней шиной 16 данных, Группа 28 входов-выходов данных блока 4 памяти соединена с внутренней шиной 16 данных. Первь 1 й вы ход 30 генератора 5 тактовых импульсов соединен со входом синхронизации системного контроллера 2, Первый выход 32 дешифратора б управления соединен с первым входом блока 7 синхронизации связи. Группа 56 входов блока 10 прерывания соединена с шинами данных внешней интерфейсной магистрали 15, а его выход 40 соединен с шиной запроса прерывания внешней интерфейсной магистрали 15. 5 Группа 34 выходов блока 7 синхронизации связи соединена с первой группой управляющих входов блока 1 связи с магистралью, вторая группа управляющих входов которого соединена с группой 36 выходов блока 8 5 управления вводом-выводом, Вторая группа 22 входов-выходов данных системного контроллера соединена с группой входов- выходов данных микропроцессора 3, группа 26 управляющих выходов, группа 29 управ1807493 Составитель В.Вью Техред М.Моргента Корректор С,йекмар Редак Заказ 1381 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С 113035, Москва, Ж, Раушская наб 4/5 город. ул, Га га пи на 101 изводственно-издательский комбинат "Патент Я А Ж ис.лоущг1807493 Группаадресных выходов (А) микропроцессора 78 (за исключением одного старшего разряда) соединена с группой 43 выходов пятым входами блока 10 прерывания. Второй 51, третий 53 выходы линейного блока 9 ввода - вывода, выход 47 чтения группы 24 блока 3 и группой (В) входов блока 79, входы СЯ-выборки и Ч-управления которого соедивыходов системного контроллера 2 соединены соответственно со вторым, третьим и, нены соответственно со входом 54 блока 3 и шиной нулевого потенциала,четвертым входами блока 14 эмуляции слова состояния, группа 61 выходов которого Старший разряд группы адресных выходов (А) микропроцессора 78 соединен с вы ходом 44 блока 3,Группа 22 входов - выходов блока 3, входы первого 80.1, второго 80.2, третьего 81.1 и четвертого 81,2 разряда группы 29 входов 64 итретий 65 блокимагистрэльныхэлемен- блока 3 соединены соответственно с груптов,15 пой .(Д) входов - выходов данных, первым входов-выходов (В) блока 65 и группой ин с шиной нулевого потенциала. Выходы упформационных входов-выходов (Д) блока равления чтением(ЯО),записью(ЮВ) исин памяти. Вторая группа входов - выходов хровыход (ЯУй) микропроцессора 78 (А) блока 65 соединена сгруппой 19 входов- соединенысоответственно с первым 82, выходов блока 1. Группа 42 адресных вхо- вторым 83 разрядами группы 26 выходов и дов блока 1 соединена с группой входов 64, 25 выходом 27.блока 3 Дешифратор 6 управления (фиг. 5) содержит блок 84 сравнения, генератор 85 группа выходов которого соединена с группой адресных входов (А) блока 62 памяти и группой 20 адресных входов-выходов блока собственного адреса, элемент И 86 и эле, Входы 66, 67 группы 36 входов соответст- . мент ИЛИ 87, выход которого соединен с венно соединены со входом записи (О/В) и 30 первым входом элемента И 86 и выходом 32. входом выборки(СЯ) блока 62 памяти. Вхо- блока 6,ды 68, 69 и 70 группы 34 входов соединены -,: Выходгенератора 85 и группа 31 входов соответственно с управляющим Ч-входом ." блока 6 соединены соответственно с первой блока 63, входами выбокки (СЗ) блоков 63 ии второй группами входов блока 84 сравне 64 и входом выборки(СЯ) блока 65: Вход 55 35 ния, а его выход соединен с первым входом соединен с управляющим Ч-входом блока элемента ИЛИ 87 и вторым входом элемента 65;"И 86, выход которого соединен с выходом 33Системнь 1 й контроллер 2 (фиг, 3) содер- блока 6. Вход 46 блока бсоединен со вторым жит.блок 71 управления, выходы (ВОМ) чте-входом элемента ИЛИ 87,ния и(ЮВМ) записи памяти, чтения (ВО)0) и 40 Блок 7 синхронизации связи (фиг, 6) созаписи(ЮВ 10)ввода-выводакоторогообра- . держит первый 88, второй 89, третий 90,четвертый 91 и пятый 92 триггеры, элемент зуют соответственно выходы первого 74 и второго 75 разрядов группьг 23 выходов ивыходы первогои второго 77 разрядовгруппы 24 выходов системного контроллера 45 И 93 и инвертор 94, вход которого соединен со входами 44 блока 7, а выход - с первым входом элемента И 93, Д-входомтриггера 90 2. Группы 21 и 22 входов-выходов, вход 30 и В-входом триггера 91.и входы первого 72 и второго 73 разрядовВход 60 блока 7 соединен со входами группы 26 входов контроллера 2 соединены синхронизации триггеров 88,. 89, 90 и 91. соответственно с первой (ДВ) и второй (Д) Вход 33 блока 7 соединен с Д-входом триггруппами входов - выходов, входом (ЯУМ) 50 гера 88 и Я-входом триггера 89, единичный синхронизации, входом (СРД) управления выход которого соединен с выходом 35 бло. чтением и входом (СИ/В) управления за- ка 7,писью блока 71, Вход (ДЕ) управления за- Вход 32 блока 7 соединен с Я-входом хватом магистрали блока 71 соединен сшиной нулевого потенциала 55 триггера 92, Д-вход которого соединен с шиной нулевого потенциала, Единичный выход Блок управления обменом 3 (фиг. 4) содержит микропроцессор 78 и блок 79 магитриггера 88 соединен с Д-входом триггера 89. Нулевой выход триггера 90 соединен с стральных элементов, группа (А) выходовкоторого является группой 25 выходов блока 3. Д-входом триггера 91. Нулевой выход триггера 88 соединен с Я-входом триггера 90, единичный выход которого соединен с Всоединена с внутренней шиной данных 16, Первый выход 32 дешифратора 6 управления.соединен с третьим входом блока 8 управления вводом - выводом,Блок 1 связи с магистралью (фиг. 2) содержит блок 62 памятипервый 63, второй(Е 1), вторым (Е 2) синхровходами, входом (В) сброса и входа (ВА) готовности микропроцессора 78, а его входы захвата магистрали (ТЯ) и запроса прерывания (ВО) соединенывходом триггера 88 и С-входом триггера 92. Кроме того, нулевые выходы триггеров 92, 88 и единичный выход триггера 90 соединены соответственно с первым 95, вторым 96 и третьим 97 разрядами групп 34 выходов блока 7. Нулевые выходы триггеров 91 и 89 соединены соответственно с первым 98 и. вторым 99 разделами группы 48 выходов блока 7, Единичный ход триггера 91 соединен со вторым входом элемента И 93, выход которого является выходом 49 блока 7.Блок 8 управления вводом-выводом (фиг. 7) содержит первый 100 и второй 101 элементы 2 И-ИЛИ, элемент И 102 и элемент ИЛИ 103, первый вход которого соединен со входом 44 блока 8, и выход соединен с выходом 37 блока 8.Выходы второго 101 и первого 100 элементов 2 И-ИЛИ соединены соответственно с первым 108 и вторым 109 разрядами группы 36 выходов блока 8.Выход элемента И 102, вход 106 группы 48 входов блока 8, вход 59 и вход 107 группы 48 входов блока 8 соединены соответственно с первым. вторым. третьим и четвертым входами блока 100.Вход 106 группы 48 входов и вход 32 блока 8 соединен соответственно с первым, вторым, третьим и четвертым входами блока 101.Входы 104 и 105 группы 23 входов блока 8 соединены соответственно со вторым входом элемента ИЛИ 103 и первым входом элемента И 102, со вторым входом элемента И 102.Линейный блок 9 ввода - вывода (фиг. 8) содержит блок 110 ввода-вывода, дешифратор 111, элемент И 112 и генератор 113 тактовых импульсов..Труппа (Д) входов - выходов блока 110 . соединена с группой 39 входов-выходов блока 9.Выходы передатчика (вых.пер,), запроса передатчика терминала (ЭПДТ), запроса приемника терминала (ЭПРТ) и входы приемника (вх.Пр.), готовности приемника терминала (ГПРТ), готовности передатчика терманала (ГПДТ) блока 110 поразрядно соединены с разрядами группы 18 входов-выходов блока 9.Первый и второй выходы генератора 113 соединены соответственно со входами синхронизации передачи (СПД) и приема (СПР) блока 110. Входы 115 и 116 группы 24 входов блока 9 соединены соответственно со входами чтения (ЧТ) и записи (ЗП) блока 110. Группа 43 входов блока 9 соединена со входами дешифратора 111, вход 114 (младший разряд) группы 43 входов кроме того35 40 45 50 55 венно с первым и вторым входами элементаИЛИ 135, выход которого соединен с выходом 60 блока 13.Блок 14 эмуляции слова состояния (фиг.12), содержит элемент И 136 и группу магистральных элементов 137,1-137.п, выходы 5 10 15 20 25 30 соединен со входом Управление/данные (У/Д) блока 110 и выходом 53 блока 9. Вход 57 блока 9 соединен с первым входом элемента И 112, выход которого соединен со входом выбора (ВУ) блока 110.Первый выход дешифратора 111 соединен со вторым входом элемента И 112 и с выходом 51 блока 9, а его второй выход соединен с выходом 50 блока 9,Блок 10 прерывания (фиг, 9) содержит первый 117 и второй 118 триггеры, первый 119 - пятый 123 элементы И,Входы 124, 125 и 126 соединены с первыми входами соответственно второго 120, третьего 121 и четвертого 122 элементов И, выходы которых соответственно соединены с Я-входом, В-входом триггера 117 и -входом триггера 118, Входы 32, 35 и 59 блока 10 соединены соответственно с первым, вторым и третьим входами элемента И 119, выход которого соединен со вторыми входами второго 120, третьего 121 и четвертого 122 элементов И. Вход 41 блока 10 соединен С-входами триггеров 117 и 118, Д-входы которых соединены с шиной нулевого потенциала, а выходы - соответственно с первым и вторым входами элемента И 123, выход которого является выходом 40 блока 10, Вход 50 блока 10 соединен с В-входом триггера 118,Блок 11 анализа состояния канала (фиг, 10) содержит счетчик 127, триггер 128, блок 129 сравнения, дешифратор 130, элемент И 131 и генератор 132 кода адреса блока, выход которого соединен с первым входом блока 129 сравнения. Группа 17 входов и вход 54 блока 11 соединены соответственно с Д-входами и входом выборки (СЯ) дешифратора 130, выход которого соединен с Рвходом триггера 128, а выход последнего - с выходом 57 блока 11, Входы 52 и 45 блока 11 соединены соответственно с первым входом элемента И 131 и входом сброса счетчика 127 и со вторым входом элемента И 131,выход которого соединен со счетным входом счетчика 127 Выход счетчика 127 соединен со вторым- входом блока 129 сравнения, выход которого соединен с 5- входом триггера 128. Блок 13 удвоения частоты (фиг. 11 а) содержит первый 133 и второй 134 одновибраторы и элемент ИЛИ 135. Вход 45 блока 13 соединен со входами одновибраторов 133 и 134, выходы которых соединены соответсткоторых соединены соответственно с первым 138.1 - п-ным 138, разрядами группы 61 выходов блока 14, Входы 53, 57, 51 и 47 блока 14 соответственно соединены с первым + четвертым входами элемента И 136, выход которого соединен с управляющими входами (Е) группы 137.1-137.п магистральных элементов, информационные входы (Х) части которых соединены также с выходом элемента И 136 (элементов, соответствующих разрядам, в которых должны быть единицы), а информационные входы (Х) остальных магистральных элементов (соответствующие нулевым разрядам эмулируемого слова состояния) соединены с шиной нулевого потенциала,Рассмотрим назначение элементов и узлов заявляемой системы.Система в целом предназначена для организации локальной вычислительной сети со структуроймоноканал",Место заявляемой системы обмена данными в вычислительной сети поясняется фиг, 13, откуда следует, что она предназначена для, подключения системы высшего уровня, .например, микро-ЭВМ, УВК типа КТС ЛИУС:, или других аналогичных средств к моноканалу через соответствующие средства связи, которые в общем случае включают в себя модем,При этом заявляемая система позволяет освободить средства системы высшего уровня от выполнения функций организации взаимодействия с сетевыми средствами, т.е, выполнения протокола обмена сети, общего управления взаимодействием станций в сети и т,д.Блок 1 связи с магистралью (фиг. 2) предназначен для приема и хранения данных, поступающих как от системы верхнего уровня через внешнюю интерфейсную магистраль 15, так и от других систем обмена данными сети, подключенных к линейному блоку 9 ввода - вывода. Таким образом, блок 1 выполняет функции общей памяти, имеющей каналы обращения как со стороны внешней магистрали 15, так и со стороны внутренней магистрали 16 данных (фиг, 1).Блок 62 памяти представляет собой оперативное запоминающее устройство,Управление обращением к нему осуществляется по сигналу со входа 67, а управление записью - по сигналу со входа 66 группы 36.Блок 63 магистральных элементов - предназначен для управления обменом между шинами данных магистрали 15 (фиг, 1) и блоком 62 памяти и может быть выполнен на известном элементе типа КР 580 ВА 87. Управление направлением передачиданных осуществляется в зависимости отсигналов на входах 68 и 69 группы 34 всоответствии с табл. 1.5 Блок 64 магистральных элементов предназначен для передачи кода адреса (младшие десять разрядов) с адресных шинмагистрали 15 на адресные входы блока 62памяти, Он также может быть выполнен на10 известных элементах типа КР 580 ВА 87.Управление работой блока 64 осуществляется сигналом с выхода 69 группы 34 всоответствии с табл, 2,Т,к. требуется только односторонняя пе 15 редача информации из порта В в порт А, тодля выбранного типа элементов. (КР 580 ВА 87) на управляющий Ч-вход должен подаваться потенциал единичногоуровня.20 Блок 65 магистральных элементов предназначен для передачи информации междуинформационным входом - выходом блока62 памяти и внутренней шиной данных 16.Он может быть выполнен на известном эле 25 менте типа КР 589 ВА 86,Управление направлением передачиданных осуществляется в зависимости отсигналов на входах 55 и 70 в соответствии стабл. 3.30 Системный контроллер 2 (фиг. 3) предназначен для управления доступом к шинеданных блока 3 (фиг, 1), а также других.блоков и устройств, Он может быть выполнен наизвестной микросхеме типа КР 580 ВК 28.35 При этом алгоритм функционирования блока 2 полностью идентичен известному дляуказанной микросхемы (см. например. кн.:Микропроцессоры, кн, 1 / Под ред. Л.Н,Преснухина - М Высш, школа, 1986. - с. 17540 177, рис. 7 - 8).Группы 21 и 22 входов-выходов блока 2предназначены для ввода - вывода данныхна внутреннюю шину 16 данных и в микропроцессор 3 (фиг, 1) соответственно.45 Вход 30 предназначен для подачи сигнала синхронизации (БУМ) с выхода генераторэ 5 тактовых импульсов (фиг, 1),Входы 72 и 73 группы 26 и редназначеныдля подачи на входы САНЧО и СВ/й блока 7150 сигналов чтения и записи соответственно свыходов 83 и 84 микропроцессоора 78 (фиг.4),Вход ДЕ блока 71 соединен с шинойнулевого потенциала,55 Выходы 74 (ВОЫ) и 75 (И/ЯМ) предназначены для выдачи сигналов управлениячтением и записью в память соответственнона входы 104 и 105 блока 8 управления вводом - выводом (фиг. 7), а выход 75, кроме тогосоединен . с входом 55 блока 1 (фиг. 2).выходы 76 (ВО 0) и 77 (ЯИО) блока 71 руемого микропроцессором в начале каждо- предназначены для выдачи сигналов чтения го машинного цикла.и записи во внешние устройства соответст- Выход 44 блока 3 (фиг. 4) соединен с венно на входы 115 и 116 линейного блока одним из старших разрядов адресного вы ввода-вывода (фиг, 8), а выход 76, кроме 5 хода (А) микропроцессора 78, не используе- того, соединен со входом 47 блока 14 (см. мого для формирования адресного фиг, 3, 1, 12) пространства (например. разряд А 11, приЕсли. в качестве приемо-передатчика одиннадцатиразрядном Ао+ А 1 о адреса), иблока 9 используется известная микросхе- служит для формированияпризйака обра-. ма типа КР 580 ВВ 51, то выходы 76 й 77 блока 10 щения микропроцессора 78 и ОЗУ системы 71 соединяются с ее входами Чтение (ЧТ) и (блок 62, фиг. 2).Запись (ЗП) соответственно (см, кн.: Микро- Блок,4 памяти (фиг. 1) представляет сопроцессоры, кн. 1 / Под ред. ЛНПреснухи- бой ПЗУ и предназначен для хранения про-на - М.; Высш. шк 1986, с. 213, рис. 7.28, б). грамм работы системы при обмене даннымиБлок 3 (фиг, 4) предназначен для управ в вычислительной сети.ленияобменомданнымииуправляющейин- Вход 37 и группа 43 входов блока 4 формацией в системе в соответствии с предназначены для подачи сигнала разрезаданным сетевым протоколом,например, шения выборки кристалла с выхода 37 блока адаптированным для шинной топологии се (фиг, 7) и адреса ячейки памяти с выхода ти протоколом ЯО С (см, далее по описа 43 блока 3(фиг. 4) соответственно,нию), Группа 28 входов-выходов блока 4Микропроцессор 78 может быть выпол- предназначена для обмена данными между нен на ивзестной. микросхеме, например, блоком 3 и шиной 16 данных,типа КР 580 ИК 80, 1 ИТЕ 8080 или другой Генератор 5 тактовьх импульсов (фиг, 1)25 предназначен для формирования тактовыхНазначение входов-выходов и алгорит- и синхронизирующих сигналов, координимы реализации команд микропроцессора 78 рующих работу блоков системы. Он может полностью аналогичны известным для мик.- быть выполнен на известной микросхеме ропроцессора указанного типа, типа КР 580 ГФ 24 или 1 йТЕ 8024 (см, кн,Основной командный цикл микропро Коффрон Дж, Технические средства микроцессора 78 приведен на фиг. 15. процессорных систем - М: Мир, 1984, с,Блок 79 магистральных элементов (фиг. 62-.66).4) предназначен для управления передачей При этом входы 41, 27 и 49. предназнакода адреса с группы адресных выходов (А)чены соответственно для подачи сигналов микропроцессора 78 на группу 25 выходов 35 установки(сброса) с одноименной шины маблока 3 и далее на шину 17 адреса системы. гистрали 15 (фиг, 1) синхронизации (ЯУИ) сБлок 79 может быть выполнен на изве- одноименного выхода микропроцессора 78 стной микросхеме типа КР 580 ВА 86 и раба- (фиг, 4) и сигнала готовности с выхода 49 тает аналогично блоку 65 (фиг. 2). блока 7 синхронизацИи связи (фиг. 6),Группа 22 входов-выходов предназна. Выходы 30 и 45 блока 5 предназначены чена для обмена данными между блоком 78 для вь 1 дачи сигнала синхронизации на вход и системным контроллером 2 (фиг, 3), 30 (ЯУН) системного контроллера 71 (фиг. 3)На входы 80.1 (Р 1), 80,2 (Р 2), 81, (В), и и тактового сигнала Ф 2 ТТ соответственно. .81.2 (ВА) группы 29 входов блока 3 поступа- . Группа выходов 29 блока 5 (фиг, 1) предют соответственно известные сигналы пер назначена для выдачи сигналов тактовых Р 1 вой синхросерии, второй синхросерии, и Р 2, сигнала установки (сброса) и сигнала установки в исходное состояние (сброса) и готовности на входы 80.1 (В) и 80,2 (КА), 81.1 готовности с соответствующей группы вы- . (В) и 81,2 (ЙА) микропроцессора 78 (фиг. 4) ходов генератора 5 тактовых импульсов соответственнд.(фиг, 1), который может быть выполнен на 50 Дешифраторбуправления(фиг.5)пред- известной микросхеме типа КР 580 ГФ 24. назначен для формирования управляющихВходы ТВ и РО блока 78 соединены с сигналов на основе кода адреса, поступаю- шиной нулевого потенциала. щего с магистрали 15 на группу входов 31 иВыходы 82 (ВО) и 83 (ЯВ) группы 26 управляющего сигнала (Запись), поступаю- выходов предназначены для выдачи сигна щего с магистрали 15 на вход 46 (фиг, 1), лов Прием /Чтение/ и Запись на входы 72 Блок 84 сравнения (фиг. 5) предназна- (СВО) и 73(СВ) системного контроллера 71 чен для сравнения кода адреса, поступаю(фиг. 3) соответственно. щего с магистрали 15 на группу входов 31, иВыход 27 (БУМ) блока 3 предназначен кода, формируемогогенератором 85 адреса, для выдачи сигнала синхронизации, форми- При совпадении кодов, поступивших на входы блока 84, на его выходе формируется Триггер 90 предназначен для фиксации нулевой сигнал, факта обращения к ОЗУ микропроцессора 3Генератор 85 адреса (фиг, 5) предназна- (фиг, 1) сигнал с его единичного выхода почен для формирования кода собственного ступает на выход 97 группы 34 выходовблоадреса системы при подклоченли к интер ка 7 и далее на вход 70 группы 34 входов фейсной магистрали 15 (фиг, 1), блока 1 (фиг. 2) и на вход 54 блоков 3 (фиг, 4)ЭлементИ 86 предназачен для форми- и 1 (фиг, 10) в качестве сигналов выборки рования управляющего сигнала а выходе (С) блока 65 магистральных элеметов (фиг.33 блока 6 (фиг, 5). 2) и дешифратора 130 (фиг. 10), и блока 79Элелент ИЛИ 87 служит для формиро О магистральных элементов (фиг. 4).вания управляющего сигнала на выходе 32 Информация, поступаощая на О-вход блока 6, триггера 90 (фиг. 6) - инвертированный элеБлок 7 синхронизации связи (фиг, 6) ментом НЕ 94 сигнал обращения к ОЗУ, предназначен для арбитража блока 3 систе- поступаощий на вход 44 блока 7 с выхода мы и системы вышего уровня и формирова блока 3 (фиг, 4), записывае,ся в триггер 90 ния.управляющих сигналов, по заднему фронту синхроимпульса, постуБлок 7(фиг, б) содержит триггеры 88,89, пившего на вход 60 блока 7,90, 91 и 92, элемент И 93 и элемент НЕ 94. На установочный Я-входтриггера 90 поТриггер 88 предназначен для фиксации ступает сигнал с нулевого выхода триггера обращения системьвысшего уровня, На его 20 88,Д-вход поступает сигнал со входа 33, фор- Поэтому, если .триггер 88 находится в мируемый дешифраторол 6 управления единичном состоянии, то триггер 90 оказы(единичный сигнал на этом входе свидетель- вается заблокированным также в едиичствует об обращении системы вьсшего ном состоянии,уровня), который записьвается в триггер 88 25 Триггер 91 гредназначен для Форлиро- по переднему фронту синхроимпульса, по- вания признака готовности для микропроступившего на вход 60 блока 7 (на этот вход цессора при обращении последнего к ОЗУ поступают синхроимпульсы с удвоенной ча- (единичное состояние триггера 91).стотой Р 2 ТТ 3 ) с выхода блока 13, При отсутствии сигнала обращения микТриггер 88 обнуляется нулевым сигна ропроцессора к ОЗУ - единичный сигнал на лом, поступающим на его Р-вход с единич- выходе элемента НГ 94 - триггер 91 заблоного выхода триггера 90, т,е. если триггер 90 кирован в нулевом состоянии и с его нуле - в нулевом состоянии. то триггер 88 будет вого выхода на выход 98 групь 48 выхода заблокирован также в нулевом состоянии, блока 7 поступает единичный сигал. Этот Сигнал, формируемый на нулевом выходе 35 сигнал далее поступает на вход 106 группы триггера 88 поступает на выход 96 группы 48 входов блока 8 управления вводом-вьво выходов блока 7 и далее на вход 69 груп- дом (фиг, 7),пы 34 входов блока 1 (Фиг, 2) в качестве При обращении микропроцессора к сигнала выборки блоков 63 и 64 магистраль- ОЗУнулевой сигнал а выходе элемента ных элементов. 40 1- Е 94 триггер 91 разблокируется и загп,сь вТриггер 89 служит для формирования него информации, поступающей на Г)-вход с единичного сигнала Ответ, который с его нулевого выходатриггера 90,осуществляет- единичного выхода поступает на вход 35 ся по переднему Фронту синхроимпульса, блока 7 и далее на соответствующую шину поступившего на вход 60 блока 7 (фиг. 6), магистрали 15(фиг, 1). 45 Триггер 92 предназначедля управлеПри нулевом сигнале а входе 33 блока . ния обменом мекду интерфсйсноймагист, поступающем на его К-вход, триггер 89 ралью 15 и блоком 1 связи с малстральо заблокирован в нулевом состоянии и с его (фиг, 1).нулевого выхода на выход 99 группы 48 вы- Сигнал с нулевого выхода триггеоа 92 ходов блока 7 поступает единичньй сигнал, 50 поступает на выход 95 группы 34 выходов который далее поступает на вход 107 груп- блока 7 и далее на вход 68 группь 34 входов пы 48 входов блока 8 (фиг, 7). блока 1 связи с магистралью (фиг, 2) в качеПоявление единичного сигнала на вхо- стве управляющего(ч) сгала блока 63 маде 33 блока 7 (фиг, 6). что соответствует гистральных элелетов,обращению системы высиего урогня, раз В нулевое состояние триггер 92(фиг, 6) блокирует триггер 89, переходит по переднему фронту едини ноИнформация, поступающая на Д-вход го сигнала, сформированного на единичном триггера 89 записывается в него по заднелу выходе триггера 90 (на О.-вход триггера 92 фронту синхроимпульса, поступившего на постоянно подан улевой потенциал), а в С-вход со входа 60 блока 7, единичное состояние триггер 92 переходитпо нулевому сигналу, поступившему на вход32 блока 7 с выхода 33 дешифратора 6 управления (фиг. 5),Элемент И 93 (фиг. 6) служит для формирования единичного сигнала готовности,поступающего с его выхода (выход 49 блока. 7) на вход 49 генератора 5 тактовых импульсов (фиг. 1).Единичный сигнал на выходе элементаИ 93 (фиг. 6) Формируется следующим образом,- и ри отсутствии обращения микроп роцессора к ОЗУ (единичный сигнал на выходеэлемента НЕ 94) - постоянно;- при обращении микропроцессора кОЗУ(нулевой сигнал на выходе элемента Н Е94) - только в том случае, если триггер 91находится в единичном состоянйи,Элемент НЕ 94 служит для инвертирования сигнала, поступающего на вход 44блока 7 (и ризна к обращения ми к роп роцессора к ОЗУ).Таким образом, благодаря взаимнойблокировке триггеров 88 и 90 осуществляется арбитраж системы высшего уровня ивнутреннего микропроцессора при их обращении. К ОЗУ и формирование соответствующих сигналов управления.Блок 8 управления вводом-выводом(фиг, 7) предназначен для формирования управляющих сигналов (СЯ-выбор кристалла иВ/В - запись) для ОЗУ 62 блока 1 (фиг. 2) исигнала управления ПЗУ (блок 4, Фиг. 1),Элемент 2 И-ИЛИ 100 предназначендля формирования управляющего сигнала(СЗ - выбор кристалла) для ОЗУ 62 (фиг. 2),Его выход (выход 109 группы 36 выходовблока 8, фиг. 7) соединен со входом 67 группы 36 входов блока 1 (Фиг, 2),Нулевой сигнал на выходе элемента 2 И-ИЛИ 100 (фиг. 7), разрешающий работу ОЗУ 62 (фиг, 2), появляется, если на выходе элемента И 102 (фиг, 7) присутствует нулевой сигнал и на входе 106 группы 48 входов блока 8 также присутствует нулевой сигнал, или в случае если на входе 59 и на входе 107 группы 48 входов - нулевые сигналы.Элемент 2 И-ИЛИ 101 (Фиг. 7) служит для формирования сигнала записи (В/В) для ОЗУ 62 (фиг, 2). 3: го выход (выход 108 группы 36 выходов блока 8, Фиг. 7) соединен со входом 66 группы 36 входов блока 1(фиг. 2).Нулевой сигнал записи Формируется на выходе элемента 2 И-ИЛИ 101 (фиг. 7) если одновременно нулевые сигналы присутствуют на входе 105 группы 23 входов и входе 106 группы 48 входов, или если на входе 32 и входе 107 группы 48 входов присутствуют нулевые сигналы, мента И 102 формируется нулевой сигнал.10 Элемент ИЛИ 103 (фиг, 7) служит для 15 20 25 обработки 40 50 55 3035 Элемент И 102 предназначен для формирования обобщенного сигнала обращения микропроцессора к памяти, Для этого на его входы со входов 104 и 105 группы 23 поступают соответственно сигналы РОМ и КВМ, формируемые системным контролле-ром 2 (Фиг, 3), При наличии хотя бы одного из указанных выше сигналов на выходе элеформирования сигнала управления ПЗУ 4 (фиг. 1), При нулевом сигнале на входе 44 блока 8(фиг, 7)-отсутствии обращения микропроцессора к ОЗУ - и наличии нулевого сигнала РОМ на входе 104 группы 23 входов,на выходе элемента ИЛИ 103 (выходе 37 блока 8) формируется нулевой сигнал, разрешающий работу ПЗУ,4 (фиг. 1),Линейный блок 9 ввода-вывода (Фиг.8) предназначен для осуществления обмена последовательными кодами данных между заявляемой системой и каналом связи вычислительной сети, Он может быть выполнен на базе микросхемы, например, типа КР 580 ВВ 51(см, кн, Микропроцессорь 1, кн, 1 ( Под ред. Л.Н.Преснухина, - М,: Высшая школа, 1986, с, 211-219, рис. 7,28, 7,29) и функционирует по известному для этой схемы алгоритму. На фиг. 8 показаны только те входы и выходы схемы, которые необходимы для пояснения сущности изобретения и его вы пол нен и я.Дешифратор 111 предназначен для распознавания кода собственного адреса блока 9 и кода, Формируемого микропроцессором 3 (фиг. 1), в случае правильного приема сообщения из канала связи вычислительной сети по окончании его При поступлении на вход 43 блока 9(Фиг, 8) кода собственного адреса блока 9 на первом выходе дешифратора, соединенном с выходом 51 блока 9, формируется единичный сигнал. Если на вход 43 поступил код, соответствующий правильному приему сообщения из сети, то на втором выходе дешифратора 111, соединенном с выходом 50 блока 9. формируется единичный сигнал запроса прерывания,Элемент И 112 предназначен для формирования сигнала управления (Выбор устройства) для блока 110, Нулевой сигнал на выходе элемента И 112 формируется при обращении микропроцессора к блоку 8 (единичный сигнал на первом выходе дешифратора 111) и отсутствии сигнала ошибки (нулевой сигнал на входе 57).Генератор 113 является известным элементом и предназначен для синхронизации работы блока 110 известным образом,Выход 114 группы 43 адресных входов данных, количество разрядов в каждом бло(например, разряд АО кода адреса) блока 9 ке данных, число разрядов останова, режимпредназначен для формирования сигнала работы, наличие или отсутствие разрядаУправление/данные (У/Д) на одноименный четности каждого блока данных (в рамкахвход блока 110, который предназначен для 5 предлагаемого изобретения контроль наидентификации сигнала записи (чтения) четность каждого блока данных не испольданных или уйравляющих сигналов. зуется, т,к, все сообщение контролируетсяС выходов 76 и 77 системного контрол- программно на основе циклического кода).лера 2 (фиг. 3) через группу 24 выходов блока Управляющие слова подразделяются на2 на входы 115 и 116 блока 9 (фиг. 8) посту два типа: инструкции режима и инструкциипают.сигналы Чтение(ЧТ) и Запись(ЗП), по . команды.которым разрешается передача данных и При передаче данных блоком 9 осущеинформации о состоянии на шину 16 данных ствляется преобразование данных, постуиз блока 110 или данных и управляющих пающих с группы 39 входов-выходов. всигналов с шины 16 даннйх в блок 110 через 15 параллельном коде в последовательностьгруппу 39 входов-выходов,: символов со служебной информацией и выВыход передатчика (Вых пер.) предназ- дача ее в канал связи с различной програмначен для выдачи во вне последовательного мно задаваемой скоростью.кода, формируемого блоком 110. При приеме информации блок 9 получаВходы синхронизации передатчика. 20 етпоследовательностьсимволовсослужеб-.(СПД) и приемника (СПР) предназначены ной информацией из канала связи,для приема тактовых импульсов, сформиро- . осуществляет выделение данных в ней, преванных генератором 113, для синхрониза- образование их в параллельный код и переции передачи и приема блоком 110. дачу его на группу 39 входов-выходов.Выходы запрос передатчика терминала 25 Блок 10 прерываний (фиг. 9) предназна,(ЗПдТ) и запрос приемника терминала чен для формирования интерфейсного сиг(ЗПрТ) предназначены соответственно для нала запроса прерывания на выходе 40,выдачи сигнала информирования внешнего который поступает на соответствующую шипередатчика о готовности канала приемни- ну магистрали 15 (фиг, 1),ка блока 110 к приему информации и сигна . Основными элементами блока 10 (фиг,ла запроса.о готовности приемника 9) являются триггеры маски 117 и запросатерминала принять данные. прерывания 118.Входы готовность передатчика терми- Элементы И 119 - 122 предназначенынала (ГПдТ) и готовность приемника терми- . для управления состоянием триггеров 117 инала (ГПрТ) предназначены соответственно 35 118.для информирования блока 110 о готовно-На группу 56 входов с магистрали 115стивнешнегопередатчикакпосылкеинфор- (входы 124, 125 и 126) поступают сигналымации по каналу связи и о готовности значенийданных(разрядыДО,Д 1 иД 2), кодприемника терминала принять информа- которых предназначен для управления тригцию в ответ на сигнал запроса по выходу 40 герами 117 и 118, В частности, сигналом со .3 ПрТ. входа 124 устанавливается маска прерыва. Вход приемника (Вх.Пр.) предназначен ния, сигналом со входа 125 осуществляется.для приема последовательного кода извне. сброс маски, а сигналом со входа 125 проВходы смещения (СМ) и подложки (П) изводится сброс запроса прерывания.соединяются друг с другом, 45 Управление элементом И 119 осуществ-Подключение блока 110 к средствам ляется на основании значений сигналов, посвязи, в качестве которых могут испольэо- ступающих на входы 32, 35 и 59,ваться известные схемы модемов или со- На.вход 50 поступает сигнал запросапряжения по уровню, осуществляются прерывания, формируемый дешифраторомизвестным обраэом(см, например кн.; Мик 111 блока 9 (фиг. 8),ропроцессоры, кн. 1 / Под ред, Л.Н Пресну- На вход 41 поступает сигнал установкихина, - М, Высшая школа, 1986, стр. 218, в исходное состояние с соответствующейрис. 7,29 и др, источники). шины йнтерфейсной магистрали 15.Управление блоком 110 осуществляется Элемент И 123 формирует на выходе 40программно. сразу после начальной уста блока 10 сигнал запроса прерывания приновки (вход начальной установки условно не его поступлении на вход 50 и неустановлен- .показан), в блок 110 со входов 39 эаписыва- ной маске,ются команды начальной установки, Блок 1 анализа состояния канала (фиг,Посредством управляющих слов блоку 10) предназначен для формирования управ 110 сообщается скорость приема-передачи ляющего сигнала "ошибка" на основе анали

СмотретьЗаявка

4908375, 04.02.1991

ХАРЬКОВСКОЕ НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ ПО СИСТЕМАМ АВТОМАТИЗИРОВАННОГО УПРАВЛЕНИЯ

ВЬЮННИК ВЛАДИМИР КУЗЬМИЧ, КАПУСТИН АЛЕКСАНДР МИХАЙЛОВИЧ, МОГУТИН РОМАН ИВАНОВИЧ, СОРОКИН НИКОЛАЙ ИВАНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТОПОРКОВ ВАЛЕНТИН ВАСИЛЬЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 13/12

Метки: вычислительной, данными, обмена, сети

Опубликовано: 07.04.1993

Код ссылки

<a href="https://patents.su/26-1807493-sistema-obmena-dannymi-v-vychislitelnojj-seti.html" target="_blank" rel="follow" title="База патентов СССР">Система обмена данными в вычислительной сети</a>

Предыдущий патент: Устройство вывода информации

Следующий патент: Устройство для обмена информацией

Случайный патент: Способ определения локализации эпилептического очага