Процессор быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1086438

Авторы: Вершков, Ветохин, Голубева, Парфенов, Прокошенков

Текст

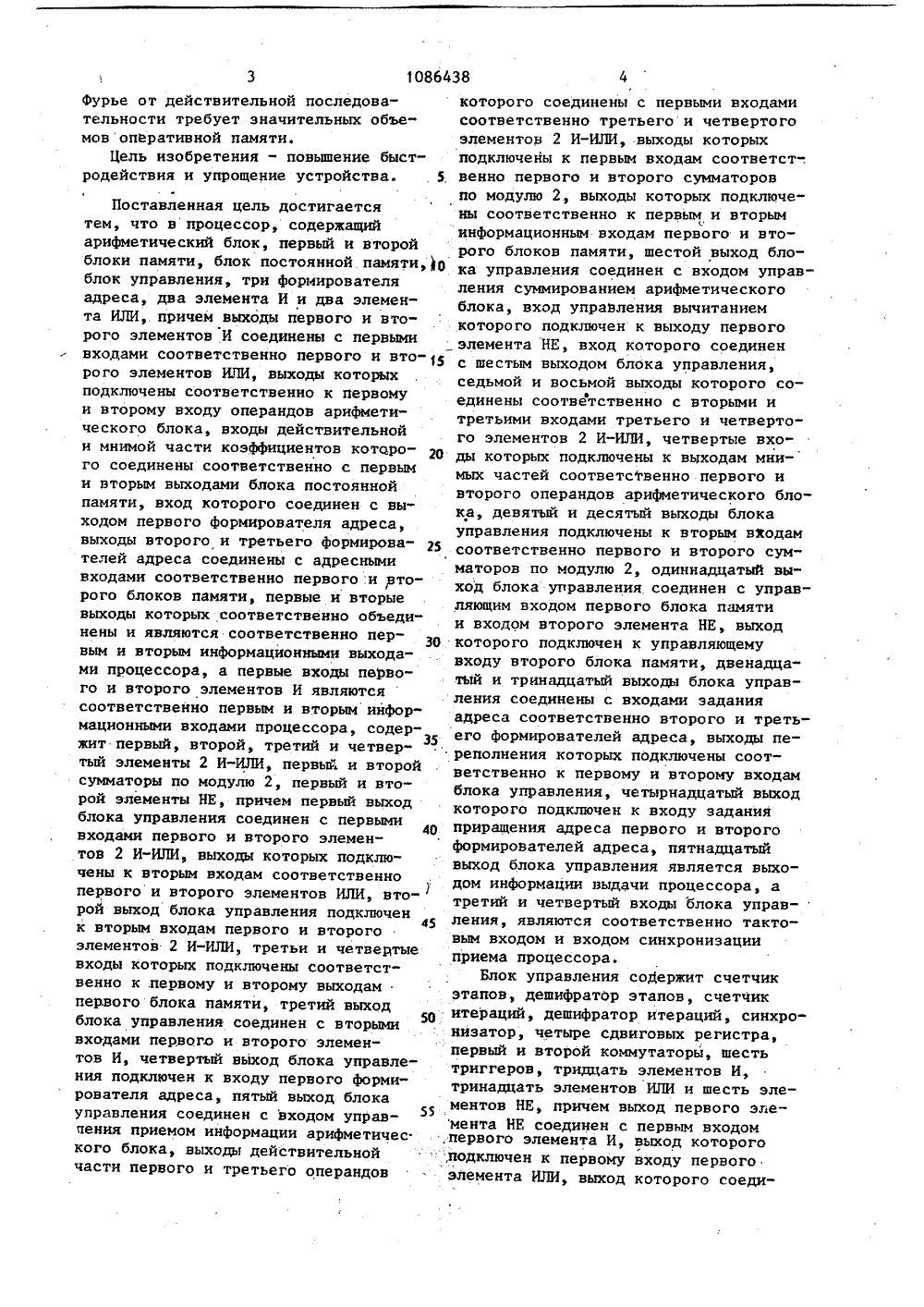

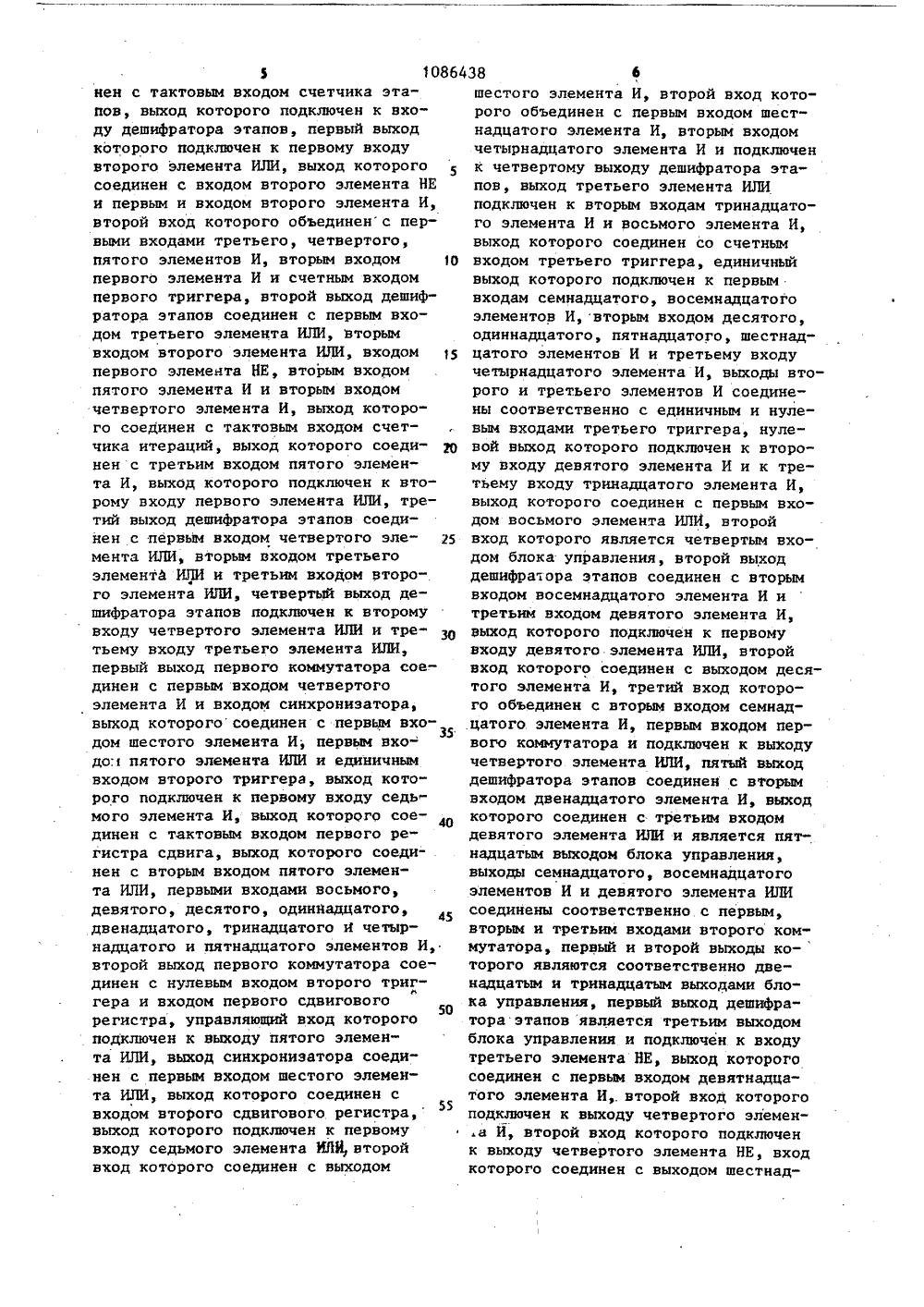

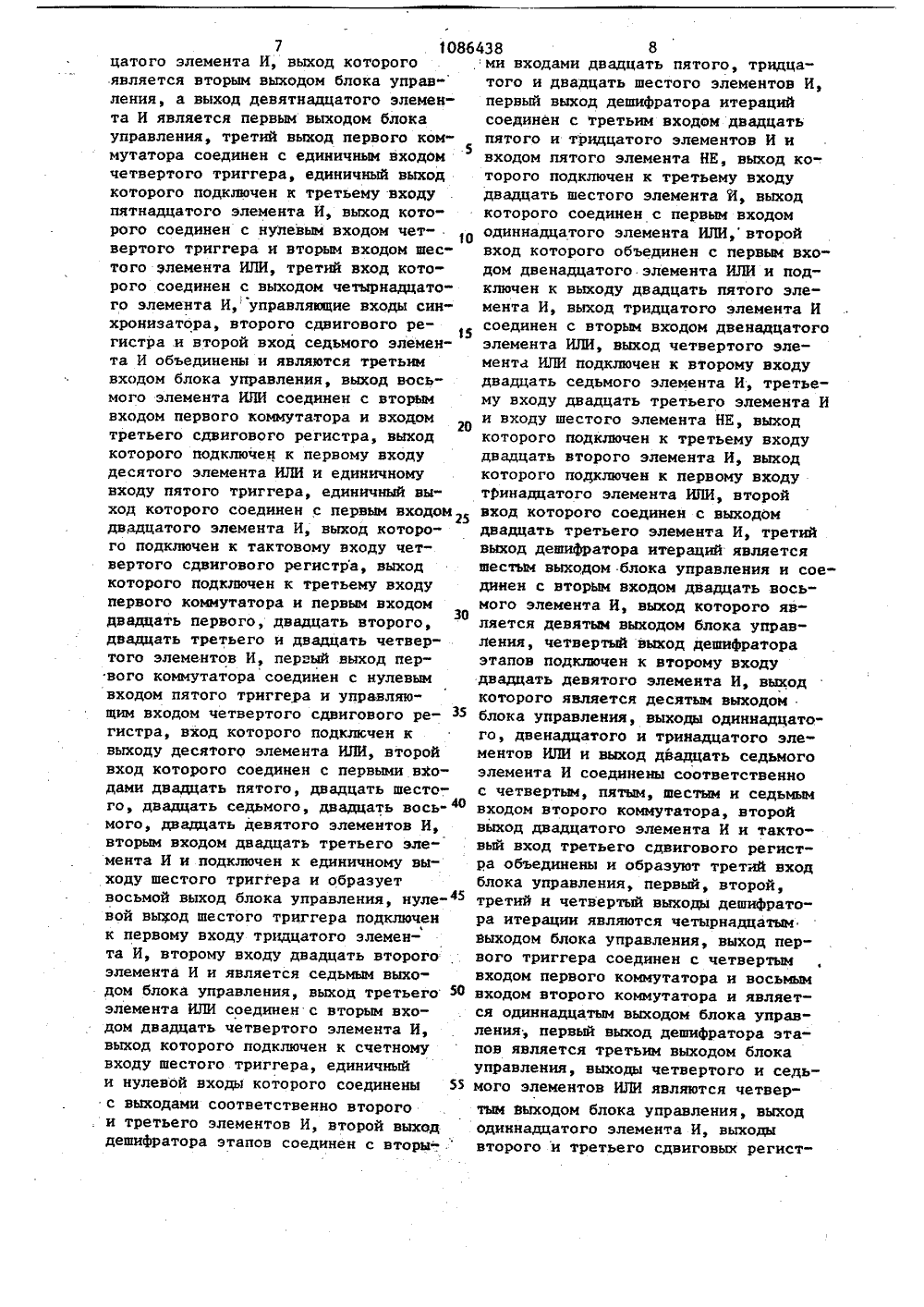

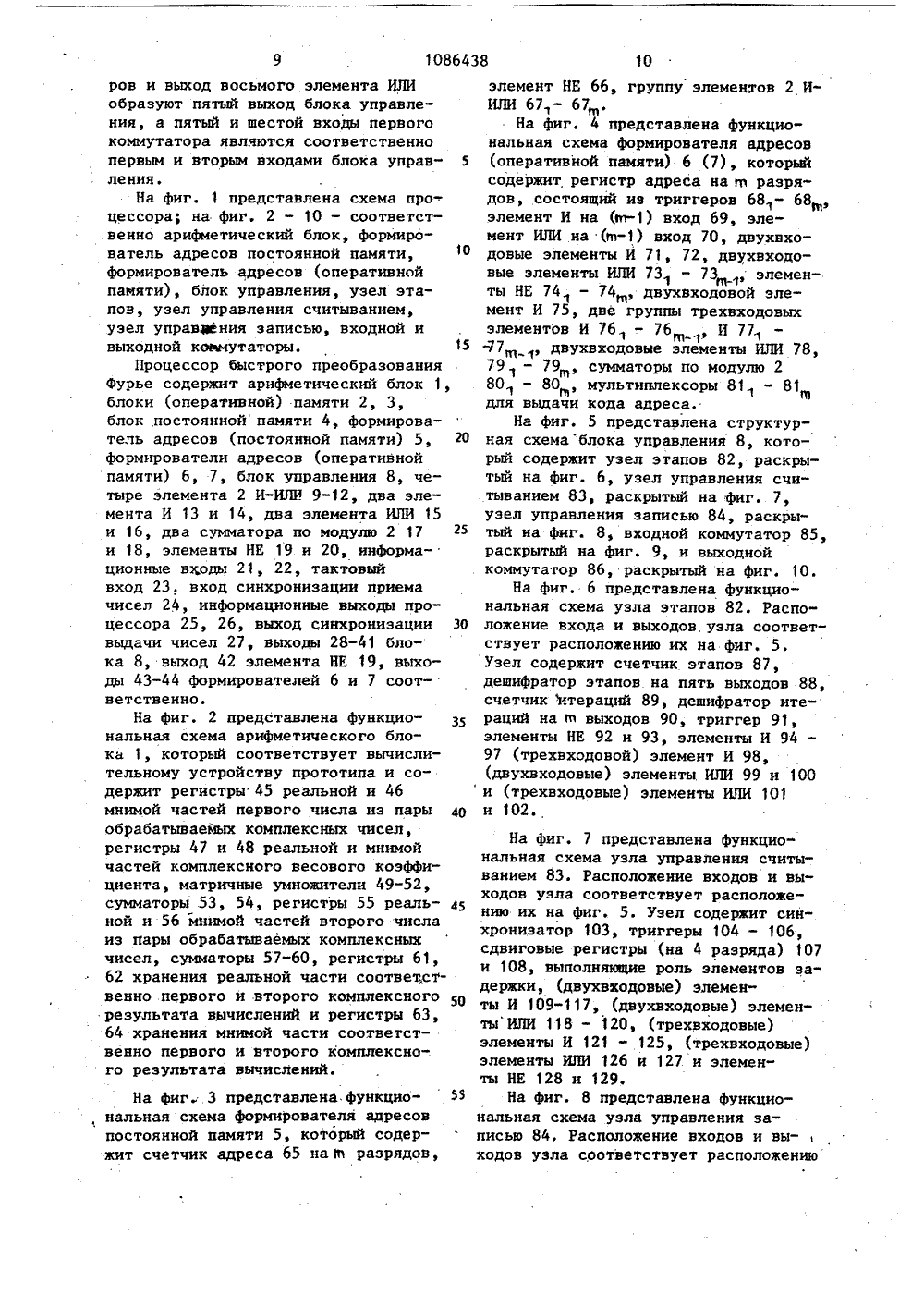

10864313отсчетов 5 Д . Каждая пара соседнихотсчетов поступает на информационныевходы процессора 21 и 22 одновремени сопровождается сигналом синхронизации приема числа по входу 24. Четные 5отсчеты (55 , ,5) поступаютна информационные входы регистра 55арифметического блока 1 через первыевходы элементов И 13 и элементов ИЛИ 15, а нечетные (5,5 ,О-5 ) - на информационные входы регистра 56 арифметического блока 1 черезпервые входы элементов И 14 и элементов ИЛИ 16,Во время ввода счетчик этапов 87(фиг. 6) блока управления 8 находится в нулевом состоянии, при этом спервого выхода дешифратора этапов 88блока управления 8 на вторые входыгрупп элементов И 13 и 14 по шине(выходу) 30 поступает разрешающийпотенциал.Сигнал синхронизации приема чиселчерез первый вход элемента ИЛИ 120(фиг, 7) блока управления 8 поступаетна последовательный вход сдвиговогорегистра 130 (фиг. 8) блока управления 8 и ьа входы записи регистров 55и 56 пэ входу 32 - 3 (фиг, 2).Тактовые импульсы по входу 23 30поступают на сдвиговый вход регистра 130 и обеспечивают последовательное продвижение сигнала синхронизации по его разрядам.Сигнал с выхода сдвигового регист-Зра 130 производит запись в регистры 61-64 арифметического блока 1 входных отсчетов, поступающих на их информационные входы с выходов регистров 55 и 56 через сумматоры 57 - 6040арифметического блока 1, на вторыевходы которых поступает нулевая информация, заданная при установке исходного состояния процессора. Одновременно этот же сигнал устанавливает45в единичное состояние триггер 132 ичерез элемент ИЛИ 140 поступает на.последовательный вход сдвигового регистра 131 (фиг. 8) блока управления 8, Сдвиговые регистры 130 и 131служат в качестве схем задержки, Сдвиговый регистр 130 обеспечивает задержку сигнала записи в регистры 6164 относительно сигнала записи в регистры 56 й 55 на время вычисленияв сумматорах 57-60. Сдвиговый регистр 131 обеспечивает задержку изменения кода адреса и информаций на 8 14/входах блоков оперативной памяти навремя их цикла записи, Триггер 133 (Фиг. 8) блока управления во время ввода находится в нулевом сос" тоянии и разрешающий потенциал с его нулевого плеча по входу 34 поступает на вторые входы элементов 2 И-ИЛИ 12 и 11, тем самым к информационным входам блоков оперативной памяти будут подключены выходы регистров 61 и 63.Изменение знаков входных отсчетов на элементах 17 н 18 не производится, так как на вторые нх входы поступают нулевые потенциалы с выходов элементов И 138 и 139 (фиг. 6) блока управления 8. Триггер 91 (фиг. 6) блока управления 8 находится в нулевом состоянии, Нулевой потенциал с единичного выхода этого триггера по,входу 38 посту" пает.на третьи входы (входы управления записью и считыванием) первогс и через элемент НЕ 20 второго блоков оперативной памяти 2 и 3, Высокий уровень на третьем входе блока оперативной памяти задает режим записи, а низкий - режим считывания. Поэтому входные отсчеты записываются в блок оперативной памяти 3. Кроме того, нулевой потенциал триггера 91 поступает на элементы выходного коммутатора 86 (фиг. 10) блока управления 8 и обеспечивает подключение выходов элементов ИЛИ 141-143 и элемента И 137 (фиг. 8) блока управления 8 по шинам 40 на входы формирователя адресов и оперативной памяти 7 (фиг. 4). Во время ввода всей последовательности входных отсчетов на выходах элементов ИЛИ 141-143 находится низкий потенциал. Низкие потенциалы с выходов эленентов ИЛИ 141-143поступают соответственно через элементы И .162, 2 И-ИЛИ 166 и 167 выходного коммутатора 86 (фиг. 10) на управляющие входы мультиплекеоров 81 - 81 щ и вторые входы элементов сумматоров по модулю 2 801 - 80по входам 40-4, 40-3 и 40"2, обеспечивая тем самым передачу кода регистра адреса 68 - 68,через мультиплексоры 81 - 81 (фиг 4) на (адресный) вход блока оперативной памяти 3.1Во время ввода в счетчике итераций 89 (фиг. 6) блока управления 8 нулевой код, при этоМ на всех выходах дешифратора 90 низкий потенциал.20 Низкие потенциалы с выходов дешифратора 90 по выходам 41 поступают на входы элементов формирователя адре сов оперативной памяти 6 и 7 и задают в формирователе приращений кода5 адреса режим естественного порядка счета.На первом входе элемента И 135, на втором входе элемента И 136, на первом и третьем выходах элемента И 149 низкие потенциалы, а на первом итретьем входах элемента И 150 высокие потенциалы (фиг. 8), поэто- му сигналы с выхода сдвигового регистра 131 проходят только на выход элемента И 150 (фиг, 8). С выхода элемента И 150 через элемент ИЛИ 143 эти сигналы в качестве сигналов счета поступают через первый вход элемента 2 И-ИЛИ 168 (на втором входе этого элемента высокий потенциал) выходного коммутатора 86 (фиг. 10) по шине 40-1 на первые входы элементов И 71,и 72 (счетный вход) формиро вателя адресов оперативной памяти 7 (фиг. 41). С приходом каждого сигнала счета содержимое регистра адреса 68 - 68 увеличивается на едини 1 Вцу1 Сигнал счета с номером К 2 во вре мя записи в блок оперативной памя.ти 7 пары отсчетов с номеромй(Я, проходя по цепочке элементов 71, 761 -7673 - 73 , производит переключение триггеров 68. - 68 регист- З 5П 1 ра адреса из единичного в нулевое состояние и через первые вход элемента И 75, второй вход элемента ИЛИ 78 в качестве сигнала переполнения по третьему выходу 44 (фиг. 4) поступает 40 на третий вход элемента 2 И-ИЛИ 153 и первый вход элемента 2 И-ИЛИ 155 (фиг. 9). На этом ввод массива входных отсчетов заканчивается, В каждой ячейке блока оперативной памяти 745 записаны по два соседних отсчета.Второй этап работы процессора заключается в вычислении промежуточнЫхкоэффициентов Фурье по формулам (1)и (2). На всех итерациях, кроме по-50следней, адреса записи вычисленных операндов А;(1) и А(%) такие же,- как и адреса считывания входных операндов А 1 (1) и А;(к). Обозначимадреса для операндов А (1) и А, (к), 1-1 55через Х 1 и Х 2, адреса операндов А;(1) и А;(к) на всех итерациях, кро.ме последней, через У 1 и У 2, а дляпоследней итерации - У 1 и У 2+. Адреса Х 1 и У 1 формируются на регистре адреса формирователем приращений формирователей адресов 6 и 7в естественном порядке счета с запретом установки в единичное состояниетех триггеров регистра адреса, номера которых совпадают с позиционнымномером выполняемой итерации, причем ./первый номер имеет старший триггер 68 регистра адреса (фиг. 4), Конкретно, на первой итерации запрещенаустановка в единицу триггера 68, навторои итерации триггера 68 и т.д.Формирование адресов Х 2 и У 2 производится логическим суммированиемна элементах ИЛИ 79 - 79 кода ре 6гистра адреса 68 - 68 с позиционнымномером выполняемой итерации.Формирование адресов У 1 и У 2 производится двоичной инверсией адресов У 1 и У 2 через вторые и четвертыевходы мультиплексоров 81 - 81 , ЗаОпись результатов вычислений по адресам У 1 и У 2 .обеспечивает. естествен- .ный порядок их расположения в блокеоперативной памяти 6 или 7.Значения комплексных весовых коэф 2 лофициентов 3хранятся в ячейЮ=еках блока постоянной памяти последо-.вательно, причем и однозначно соответствует номеру ячейки.Считывание кодов весовых коэффициентов в арифметический блок 1 производится в начале каждой итерации и посигналу конца зоны, поступающему с выхода элемента И 70 (фиг. 4) на второмвыходе 43 для блока 6 и по второмувходу 44 для блока 7. Адреса для считывания весовых коэффициентов формируются путем двоичной инверсии на элементах 2 И-ИЛИ 67 - 67 кода счет.1чика адреса 65,Рассмотрим работу процессора повычислению промежуточных коэффициентов по формулам.(1) и (2) на примереобработки первой пары операндов первой итерации.Сигнал переполнения по окончанииввода с выхода элемента ИЛИ 78 блока 7 (фиг. 4) по третьему выходу 44через первый вход элемента 2 И-ИЛИ 155(на втором входе высокий потенциал),через второй вход элемента ИЛИ 159(фир. 9)входного коммутатора, в качестве сигнала конца записи массива,поступает на вход узла управлениясчитыванием 83 и на третий вход узла17 108643чуправления записью 84. В блоке управления 8 сигнал конца записи массивапроизводит следующее: через второйвход элемента И 94 (на первом входевысокий потенциал) и второй вход элемента ИЛИ 99 добавляет единицу всчетчик этапов 87, обеспечивая темсамым высокий уровень на втором выходе дешифратора этапов 88 (фиг. 6)и низкий на всех остальных выходах;переключение триггера 91 (фиг. 6)из нулевого в единичное состояние,устанавливая тем самым блок оперативной памяти 2 в режим записи, а блок .оперативной памяти 3 в режим считы.вания; через первый вход элемента И 96 (на втором выходе высокийпотенциал) устанавливает в единичноесостояние триггер 106 (Фиг, 7) узлауправления считыванием 83 и треггер 133 (фиг. 8) узла управления за"писью 84; через синхронизатор 103(фиг, 7) устанавливает в единичноесостояние триггер 104 и через элементы ИЛИ 118 и 12 б первые разряды.сдвиговых регистров 107 и 108; подтверждает нулевое состояние тригге"ра 132 и регистра 131 (Фиг. 8) узлауправления записью 94.Высокий потенциал с единичного выхода триггера 91 (фиг, 6) по двенадцатому выходу узла этапов поступаетна вход элемента НЕ 169, на вторыевходы элементов И 161 и 162 и на четвертые входы элементов 2 И-ИЛИ 163 -168 (Фиг. 10), обеспечивая тем самымпередачу сигналов из узла управлениясчитыванием 83 по выходам 40 в формирователь адресов 7 и передачу сигналов из узла управления записью 84 40.по выходам 39 в Формирователь адреосов 6,Высокий уровень на втором выходе дешифратора этапов 88 и единичное45 состояние триггера 106 обеспечивает формирование высокого потенциала на выходе элемента И 116 и низкого - на; выходе элемента И 117 (фиг. 7) узла управления считыванием 83, при этдм на выходах элементов И 162 и 2 И 50 ИЛИ 167 низкие потенциалы, а на выходе элемента 2 И-ИЛИ 166 в . высокий потенциал (фиг. 1.0) выходного коммутатора 86. Эти потенциалы, поступая по выходам 40-3, 40-2, 40-4 в Форми рователь адресов 7, обеспечивают формирование и выдачу адреса Х 2 в блок оперативной памяти 3, при этом на выходах его устанавливается значение операнда А; (к). Аналогично высокий уровень на втором выходе дешифратора этапов 88 и единичное состояние триггера 133 (фиг. 8) узла управления записью 84 обеспечивают в формирователе адресов 6 формирование и выдачу из него в блок оперативной памяти 2 адреса У 2. Адреса Х 2 и У 2 формируются на элементах ИЛИ 79 1 - 79, при этом на управляющих входах А и В соответственно единичный и нулевой потенциалы и на выходы мультиплексоров передаются уровни вторых входов (входы "1"). На выходе элемента И 113 в процессе выполнения второго этапа держится высокий потенциал. Поступая по выходу 28 (фиг, 1) на вторые входы элементов 2 И-ИЛИ 9 и 10, этот потенциал разрешает прямую передачу операндов из блоков оперативной памяти 3 или, 2 в арифметический блок 1, т,е, мнимая часть операнда поступает на первый вход, а действительная на второй вход арифметического блока 1.Высокий уровень единичного плеча триггера 104 (фиг. 7) разрешает прохождение через элемент И 109 тактовых импульсов на сдвиговый вход регистра 107, которые производят последовательное продвижение единицы по разрядам регистра, Сигнал с выхода (старший разряд) сдвигового регистра 107 при единичном состоянии триггера 106 производит следукнцее: через первый вход элемента И 115 по выходу 32-1 поступает на вторые входы регистров 45 и 46 арифметического блока 1 и производит запись в них соответственно реальной и мнимой частей операнда А; (к); через первый вход элемента ИЛЙ 118 устанавливает в единицу первый разряд сдвигового регистра. 107; через первый вход элемента И 110 производит переключение триггера 106 (фиг. 7). Тактовые импульсы поступают на сдвиговый вход регистра 108 (фиг, 7) производя продвижение единицы по разрядам регистра. Сигнал с выхода сдвигового регистра 108 производит следующее: по выходу 32-2 поступает на вторые входы регистров 47 и 48 арифметического блока 1, записывая в них соответственно реальную и мнимуючасть комплексного весового коэффициента.При нулевом состоянии триггера 106 и 64 поступают соответственно реаль(фиг. 7) на выходе элементов И 116 ная и мнимая части результата А;(к).и 1 17 низкие потенциалы, которые че- Сигнал с выхода сдвигового регистреэ первые входы элементов 2 И-ИЛИ 166 ра 130 (фиг. 8), задержанный по оти 167 по выходам 40-4 и 40-2 посту ношению к входному сигналу на времяпают в формирователь адресов .7 и задержки сумматоров 57-60, производитсовместно .с низким, потенциалом с вы- . следующее: по выходу 32-4 записываетхода элемента И 162, поступаинцим по результаты А.(1) и А;(к) в региствыходу 40-3 также в формирователь ры 61-64 арифметического блока 1;1адресов 7, обеспечивают выдачу в10устанавливает первыи разряд сдвиговоблок оперативной памяти 3 кода адре- го регистра 131 через второй входса Х 1, при этом на информационных вы- элемента ИЛИ 140 (фиг. 8) в единичходах этого блока устанавливается ное состояние; устанавливает в едизначение операнда А, который яичное состояние триггер 132, разреаналогично операнду А; (к) поступа- шая прохождение тактовых импульсов15ет на первый и второй входы арифме- через элемент И 134 на сдвиговыйтического блока 1. вход регистра 131,При нулевом состоянии триггера 106 Единичное состояние триггера 133(фиг. 7) сигнал с выхода сдвигового (фиг. 8) обеспечивает подключениерегистра 107 производит следующее:выходов регистров 62 и 64 на информачерез третий вход элемента И 121 иционные входы блоков оперативной павторой вход элемента ИЛИ 120 устанав- мяти 2 и 3, при этом из формирователивает в единицу первый разряд ре- ля адресов 6 в блок оперативной памягистра, 130 (фиг. 8) и но выходу 32-3 ти 2 поступает адрес У 2. К моментупоступает на вторые (управляющие) появления сигнала на выходе регист 25входы регистров 55 и 56, записывая в ра 131 в блоке оперативной памяти 2них соответственно реальную и мнимую происходит запись результата А (к),1часть операнда А; ; через третий . Сигнал с выхода регистра 131 провход элемента И 124, второй вход эле- изводит следующее: через второй входмента ИЛИ 127 узла управления считы- ЗО элемента И 136 (на первом входе этованием 83 (фиг. 7) и третий вход эле- го элемента разрешающий потенциал,мента 2 И-ИЛИ 168 выходного коммута- образованный сборкой по ИЛИ второго,тора 86 (фиг. 10) по выходу 40-1 по" третьего и четвертого выходов дешиступает на.первые входы элемен- фратора этапов 88, фиг, 6, на элетов И 71 и 72 (счетный вход) форми менте ИЛИ 101) переключает в нулевоерователя адресов 7, увеличивая содер- состояние триггер 133 (фиг. 8), прижимое регистра адреса 68 1 - 68 этом на выходе формирователя адресов 6 формируется адрес У 1; черезПри выполнении всех этапов обра- второй вход элемента И 135 и первыйботки сумматоры 53 и 57 выполняют 40 вход элемента ИЛИ 140 записывает едиоперацию сложения входных операндов, нину в первый разряд регистра 131,сумматоры 54 и 58 выполняют операцию При нулевом состоянии триггера 133вычитания, причем вычитаемым являются к блокам оперативной памяти 2 и 3операнды, поступающие на вторые вхо- подключены регистры 61 и 62.ды этих сумматоров. Низкий потенци 45ал с третьего выхода дешифратора эта-. К моменту появления сигнала на выпов.88 (фиг. 6) по выходу 33 поступа- ходе регистра 131 в блоке оперативет на управляющий вход сумматора 59 ной памяти 2 происходит запись резуль(фиг. 2) и через элемент НЕ 19 по тата А (1) но адресу У 1.выходу 42 (фиг. 1) на управляющий50При нулевом состоянии триггера .133вход сумматора 60, обеспечивая тем сигнал с выхода регистра 131 черезсамым операцию сложения на суммато-второй вход элемента И 150, второйре,59 и операцию вычитания на сумма- вход элемента ИЛИ 143, третий вход.торе 60. элемента 2 И-ИЛИ 165 выходного комНа информационные входы регист мутатора 86 (фиг. 10) по выходу 39-1ров 61 и 63 поступают реальная и мни- поступает на счетный вход формировамая части результата А;, а на ин- теля адресов 6 и увеличивает код реформационные входы регистров 62 гистра адреса 68- 68,.на управляющий вход сумматора 60 арифметического блока 1.Организация считывания операндов А и Ал 7 в регистры 55, 56 и 45, 46 такая же, как и для операн дов А;, А; (к) при выполнении второго этапа.Для обеспечения подачи реальной части с с регистра 45 на вторые входы сумматоров 57, 58 и мнимой час ти д с регистра 46 на вторые входы сумматоров 59, 60 в регистры 47 и 48 в начале этапа лроизвопится считывание по нулевомч апоесч из блока постоянной памяти весового коэЬЬипиента, у которого Реальная часть равна единице, а мнимая нулю. В результате считывания в регистре 47 все разряды установлены в единичное состояние, а в регистре 48 - нулевое состояние на протиженип всего этапа выполнения.Адресом на считывание операнда Аявляется прямой код, а операнда А1 сМ 7-Фобратнуй код регистра адреса 68 - 1 25-68, формирователя адресов (6 или 7)включенного в режим считывания,Адреса на запись результатов теЕже, что и адреса считывания входныхоперандов, причем запись.1 + 1 Л про 7 30изводится по прямому коду адреса,а 6 +6 по обратному коду адресаформирователя адресов, включенногов режим записи,Формирование обратного кода адреса производится при высоком потенциа-З 5,ле па вторых входах сумматоров по модулю 2 80 - 80 п, высокий потенциалформируется на элементе И 117:приединичном состоянии триггера 106 узлауправления считыванием 83 (фиг. 7) ина выходе элемента И 137 при единичном состоянии триггера 133 узла управления записью 84 (фиг. 8).Адреса для считывания и записиоперандов передаются в блоки оперативной памяти 2 и 3 через первые входымультиплексоров 81 в . 81 (фиг. 4)11 лпутем подачи на управляющие входы А .и В низких потенциалов с выходов элементов И 161, 2 И-ИЛИ 163 для блока 6, И 162, 2 И-ИЛИ 166 (фиг. 10)для блока 7. Добавление единицы к содержимому регистра 68- 68 формиро-",вателя адресов (6 или 7), включенно-го в режим считывания, производитсячерез первый вход элемента И 125 итретий вход элемента ИЛИ 127 (фиг, 7).Добавление единицы к содержимому ре гистра адреса 68 - 68, формирователя адресов (6 или 7), включенного врежим записи, производится через второй вход элемента И 149 и первыйвход элемента ИЛИ 143 (фиг. 8).Сигналы конца считывания и записимассива на третьем и четвертом этапахформируются при единичном состояниитриггеров 681 - 68 л , при .этом навыходе элемента И 69 (фиг. 4) устанавливается высокий потенциал,Пусть для определенности триггер 91 находится в единичном состоянии, Тогда высокий потенциал с единичного выхода этого триггера поступает на вход элемента НЕ 160 и на четвертые входы элементов 2 И-ИЛИ 151155. Формирователь адресов 7 включен в режим считывания, а формирователь адресов 6 - в режим записи. Высокий потенциал с выхода элемента И 69 формирователя адресов 7 повыходу 44 через третий вход элемента 2 И-ИЛИ 151 поступает на второйвход элемента И 156 (на третьем входе высокий потенциал)При поступлении импульсного сигнала с выходаэлемента ИЛИ 120 (фиг. 7) на первый .вход элемента И 156 (фиг. 9) на еговыходе формируется сигнал конца считывания массива, который устанавливает в нулевое состояние триггер 132,прекращая процесс считывания.Высокий потенциал с выхода элемента И 69 формирователя адресов 6по выходу 43 через третий вход элемента 2 И-ИЛИ 154 поступает на первыйвход элемента И 157 (на втором входевысокий потенциал). При поступленииимпульсного сигнала с выхода элемента 131 (фиг. 8) на третий вход элемента И 157 на его выходе формируется сигнал конца записи массива, который производит пействия 1 аналогичныепействиям на предыдущих этапах.К счетчику этапов 87 добавляется еди-ница, а на дерифраторе этапов устанавливается высокий потенциал начетвертом выходе.При выполнении четвертого этапавычисление коэффициентов фурье произВОДИТСЯ ПО фоРМУЛаМь:л+л,+- а.ь,а", а8л+И -(Й+6 В, (102 Й 11к=1, 2, 3(-1) ЧЧУ Ц27 1086438 28Другим преимуществом процессорафурье в естественном порядке за счет является сокращение в два раза ем- реализации в процессоре соответсткости блоков оперативной памяти при вующей работы формирователей адресов сохранении функциональных возмож- оперативной памяти исключает ностей за счет упаковки каждбй пары 5 необходимость перестановки кососедних отсчетов в каждую ячейку эффициентов фурье на последую- памяти. Кроме того, вывод сформиро" щих этапах обработки инфор" ванных (вычисленных) коэффициентов машки.арифметического блока, вход управле ния вычитанием которого подключен к выходу первого элемента НЕ, вход которого соединен с шестым выходом блока управления, седьмой и восьмой выходы которого соединены соответственно с вторыми и третьими входамитретьего и четвертого элементов 2 ИИЛИ, четвертые входы которых подключены к выходам мнимых частей соответственно первого и второго операндов арифметического блока, девятый и десятый выходы блока управления подключены к вторым входам соответственно первого и второго сумматоров по модулю 2, одиннадцатый выход блока управления соединен с управляющим входом первого блока памяти и входом второго элемента НЕ, выход которого подключен к управляющему входу второго блока памяти, двенадцатый и тринадцатый выходы блока управления соединены с входами задания адреса соответственно второго и третьего формирователей адреса, выходы переполнения которых .подключены соответственно к первому и второму входам блока управления, четырнадцатьп выход которого подключен к входу задания приращения адреса первого и второго формирователей адреса, пятнадцатый выход блока управления является выходом информации выдачи процессора, а третий и четвертый входы блока управления, являются соответст-. венно тактовым входом и входом синхронизации приема процессора.а2. Устройство по п, 1, о т л и - ч а ю щ е е с я тем, что блок управления содержит счетчик этапов, дешифратор этапов, счетчик итераций, дешифратор итераций, синхронизатор, четыре сдвиговых регистра, первый и второй коммутатор, шесть триггеров, . тридцать элементов И, тринадцать элементов ИЛИ и шесть элементов НЕ, причем выход первого элемента НЕ соединен с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого соединен с тактовым входом счетчика этапов, выход которого подключен к входу дешифратора этапов, первый выход которого подключен к первому, входу второго элемента ИЛИ, выход которого соединен с входом второго элемента НЕ и первым входом второго элемента И, второй вход которого объединен с первыми входами третьего, четвертого, пятого элементов И, вторым входом первого элемента И и счетным входом первого триггера, второй выход дешифратора этапов соединен с первым входом третьего элемента ИЛИ, вторым входом второго элемента ИЛИ, входом первого элемента НЕ, вторым входом пятого элемента И и вторым входом четвертого элемента И, выход которого соединен с тактовым входом счетчика итераций, первый выход которого соединен с третьим входом пятого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, третий выход дешифратора этапов соединен с первым входом четвертого элемента ИЛИ, вторым вхо" дом третьего элемента ИЛИ и третьим входом второго элемента ИЛИ, четвертый выход дешифратора этапов подключен к второму входу четвертого элемента ИЛИ и третьему входу третьего элемента ИЛИ, первый выход первого коммутатора соединен с первым входом четвертого элемента И и входом синхронизатора, выход которого соединен. с первым входомшестого элемента И, первым входом пятого элемента.ИЛИ иединичным входом второго триггера,выход которого подключен к первомувходу седьмого элемента И, выход ко"торого соединен с тактовым входомпервого регистра сдвига, выход кото рого соединен с вторым входом пятогоэлемента ИЛИ, первыми входами вомьйого, девятого, десятого, одиннадцатого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого элементов И, второй выход первого коммута-, тора соединен с нулевым входом второго триггера и входом первого сдвигового регистра, управляющий вход которого подключен к выходу пятого элемента ИЛИ, выход синхронизатора соединен с первым входом шестого элемента ИЛИ, выход которого соединен с входом второго сдвигового регистра, выход которого подключен к первому входу седьмого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, второй вход которого объединен с первым входом шестнадцатого элемента И, вторым входом четырнадцатого элемента И и подключен к четвертому выходу дешифратора этапов, выход третьего элемента ИЛИ подключен к вторым входам тринадцатого элемента И; Уято 3/46 . Тираж 69 ВНИИПИ Государственног по делам ийобрет 035 Москва, Ж, Рауш10864 и восьмого элемента И, выход которогосоединен со счетным входом третьего триггера, единичный выход которого подключен к первым входам семнадцатого, восемнадцатого элементов И, вторым входом десятого, одиннадцатого, пятнадцатого, шестнадцатого элементов И и третьему входу четырнащатого элемента И, .выходы второго и третьего элементов И соединены соответст" венно с,единичным и нулевым входами третьего триггера, нулевой выход которого подключен к второму входу девятого элемента И и третьему входу тринадцатого элемента И, выход которого соединен с первым входом восьмо- го элемента ИЛИ, второй вход которого является четвертым входом блока управления, второй выход дешифратора этапов соединен с вторым входом восемнадцатого элемента И и третьим входом девятого элемента И, выход которого подключен к первому входу девятого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, третий вход которого соединен с вторым входом семнадцатого элемента И, первым входом первого коммутатора и подключен к выходу чет" вертого элемента ИЛИ, пятый выход дешифратора этапов соединен с вторым входом двенадцатого элемента И, выход . которого соединен с третьим входом девятого элемента ИЛИ и является пятнадцатым выходом блока управления, выходы семнадцатого, восемнадцатого элементов И и девятого элемента ИЛИ соединены соответственно с первым, вторым и третьим входами второго коммутатора, первый и второй выходы которого являются соответственно двенадцатым и тринадцатым выходами блока управления, первый выход дешифратора этапов является третьим выходом блока управления и подключен к входу третьего элемента НЕ, выход которого соединен с первым входом девятнадцатого элемента И, второй вход которого подключен к выходу четвертого эле"мента НЕ, вход которого соединен с выходом шестнадцатого элемента И, выход которого является вторым выходом блока управления, а выход девятнадцатого элемента И является первым выходом блока управления, третий выход первого коммутатора соединен с единич. ным входом четвертого триггера, единичный выход которого подключен ктретьему входу пятнадцатого элемен 38та И, выход которого соединен с нулевым входом четвертого триггера и вторым входом шестого элемента ИЛИ, третий вход которого соединен с выходом четырнадцатого элемента И, управляющие входы синхронизатора, второго сдвнгового регистра и второй вход седьмого элемента И объедйены и являются третьим входом блока управле ния, выход восьмого элемента ИЛИ соединен с вторым входом первого коммутатора и входом третьего сдвигового регистра, выход которого подключен к первому входу десятого элемента ИЛИ и единичному входу пятого триггера, единичный выход которого соединен с первым входом двадцатого элемента И, выход которого подключен к тактовому входу четвертого сдвигового регистра, выход которого подключен к третьему входу первого коммутатора и первым входом двадцать первого, двадцать второго, двадцать третьего и двадцать четвертого элементов И, первый выход первого коммутатора соединен с нулевым входом пятого триггера и управляющим входом четвертого сдвигового регистра, вход которого подключен к выходу десятого элемента ИЛИ, второй вход которого объединен с первыми входами двадцать пятого, двадцать шестого, двадцать седьмого, двадцать восьмого, двадцать девятого элементов И, вторым входом двадцать третьего элемента И и подключен к единичному выходу шестого триггера и образует восьмой выход блока управления, нулевбй выход шестого триггера подключен к первому входу тридцатого элемента Й, вчърому входу двадцатьвторого элемента И и является седьмым выходом блока управления, выходтретьего элемента ИЛИ соединен с вторым входом двадцать четвертого элемента И, выход которого подключенк счетному входу шестого триггера, единичный и нулевой входы которогосоединены с выходами соответственно второго и третьего элементов И, второй выход дешифратора этапов соединен с вторыми входами двадцать пятого, тридцатого и двадцать шестого элементов И, первый выход дешифратора итераций соединен с третьим входомдвадцать пятого и тридцатого элемеп;тов И, входом пятого элемента НЕ, выход которого подключен к третьемувходу двадцать шестого элемента И, выход которого соединен с первым вхо108 б 438 дом одиннадцатого элемента ИЛИ, вто-рой вход которого объединен с первым входом двенадцатого элемента ИЛИи подключен к выходу двадцать пятогоэлемента И, выход тридцатого элемента И, соединен с вторым входом двенадцатого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к второму входу двадцать седьмого элемента И, третьему входу двадцать третьего элемента И и входу шестого элемента НЕ, выход которого подключен ктретьему входу двадцать второго элемента И, выход которого подключен кпервому входу тринадцатрго элемента ИЛИ, второй вход которого соединен с выходом двадцать третьего элемента И, третий выход дешифратораитераций является шестым выходом блока управления и соединен с вторымвходом двадцать восьмого элемента И,выход которого является девятым вы-ходом блока управления, четвертыйвыход дешифратора этапов подключенк второму входу двадцать девятогоэлемента И, выход которого являетсядесятым выходом блока управления,выходы одиннадцатого, двенадцатогоИзобретение отиосится к области вычислительной техники и может быть использовано для решения задач цифровой обработки сигналов.Известно устройство для вычисления коэффициентов Фурье, в котором быстродействие повышается за счет совмещения вычислений. Устройство содержит блоки умножения, суммирующие блоки, регистры действительной и мнимой частей весового коэффициента Г 13. Несмотря на применение четырех множительных блоков и одновременное выполнение операций умножения, сложения и вычитания, устройство отличается сравнительно небольшим быстродейст вием, так как результаты вычислений оказываются записанными в те же ре-, гистры, куда записываются исходные данные. Поэтому вычислительное устройство не может начать обработку следующих операндов до тех пор, пок; 5 10 5 20 и тринадцатого элементов ИЛИ и выходдвадцать седьмого элемента И соединены соответственно с четвертым, пятым,шестым и седьмым входом второго коммутатора, второй выход двадцатого элемента И и тактовый вход третьего сдвигового регистра объединены и образуют третий вход блока управления, первый, второй, третий и четвертый выходы дешифратора итерации являются четырнадцатым выходом блока управления, выход первоготриггера соединен с четвертым входом первого коммутатора и восьмым входом второго коммутатора и является одиннадцатым выходом блока управления, первый выход дешифратора этапов является третьим выхо, дом блока управления, выходы четвертого и седьмого элементов ИЛИ являются четвертак выходом блока управления, выход одиннадцатого элемента И, выходы второго и третьего сдвиговых регистров и выход восьмого элемента ИЛИ образуют пятйй выход блока управления, а пятый и шестой входы первого коммутатора являются соответственно первым и вторым входами блока управления. ранее вычисленные результаты не будутпереписаны в ОЗУ,Наиболее близким техническим решением к изобретению является устройство для вычисления коэффициентовФурье, содержащее блоки умножения,суммирующие блоки, регистры действительной и мнимой частей входных операндов, регистры действительной имнимой частей весового коэффициента,регистры действительной и мнимой частей выходных операндов, а также промежуточные регистры, обеспечивающиеповышение быстродействия вычисленийза счет совмещения работы блоков ум-ножения и суммирующих блоков Г 2 3.К недостаткам данного устройстваследует отнести относительно небольшое быстродействие при вычислениикоэффициентов Фурье от действительнойпоследовательности входных данных;кроме того, реализуемая в нем организация вычислений коэффициентов1086438фурье от действительной последова- которого соединены с первыми входамительности требует значительных объе- соответственно третьегои четвертогомов оперативной памяти. элементов 2 И-ИЛИ, выходы которыхЦель изобретения - повышение быст- подключены к первым входам соответст-.родействия и упрощение устройства. . 5 венно первого и второго сумматоровпо модулю 2, выходы которых подключеПоставленная цель достигаетсяны соответственно к первым и вторымтем, что впроцессор, содержащий(.информационным входам первого и втоарифметический блок, первый и второй р го блоков памяти, шестой выход блоблоки памяти, блок постоянной памятиф ам О ка управления соединен с входом управблок управления, три формирователя ления суммированием арифметическогоадреса, два элемента И и два элемен- блока, вход управления вычитаниемта ИЛИ, причем выходы первого и втокоторого подключен к выходу первогорого элементов И соединены с первыми элемента НЕ, вход которого соединенвходами соответственно первого и вто с шестым выходом блока управления,рого элементов ИЛИ, выходы которых седьмой и восьмой выходы которого соподключены соответственно к первому единены соответственно с вторыми ии второму входу операндов арифметитретьими входами третьего и четверточеского блока, входы действительной го элементов 2 И-ИЛИ, четвертые вхои мнимой части коэффициентов котаро ды которых подключены к выходам мни-го соединены соответственно с первым мых частей соответственно первого ии вторым выходами блока постоянной второго операндов арифметического блопамяти, вход которого соединен с вы- ка, девятый и десятый выходы блокаходом первого формирователя адреса,управления подключены к вторым входамвыходы второго и третьего формировасоответственно первого и второго сумтелей адреса соединены с адресными маторов по модулю 2, одиннадцатый вывходами соответственно первого и вто- ход блока управления соединен с управрого блоков памяти, первые и вторые ляющим входом первого блока памятивыходы которых соответственно объеди- и входом второго элемента НЕ, выходиены и являются соответственно перЗО которого подключен к управляющемувым и вторым информационными выхода- входу второго блока памяти, двенадцами процессора, а первые входы пврво- тый и тринадцатый выходы блока управго и второго элементов И являютсяпения соединены с входами заданиясоответственно первым и вторым инфорадреса соответственно второго и третьмационными входами процессора, содер- его формирователей адреса, выходы пежит первый, второй, третий и четверреполнения которых подключены сооттый элементы 2 И-ИЛИ, первый и второйветственно к первому и второму входамсумматоры по модулю 2, первый и вто- блока управления, четырнадцатый выходрой элементы НЕ, причем первый выходкоторого подключен к входу заданияблока управления соединен с первыми40 приращения адреса первого и второговходами первого и второго элеменформирователей адреса, пятнадцатыйтов - , выходы которых подклю- выход блока управления является выхочены к вторым входам соответственнодом информации выдачи процессора, апервого и второго элементов ИЛИ, вто- третий и четвертый входы блока управ-роМ выход блока управления подключен л нления, являются соответственно такток вторым входам первого и второгоэлементов 2 И-ИЛИ, рвым входом и входом синхронизацииИ-ИЛИ, третьи и четвертыеприема процессора.входы которых подключены соответстБлок управления содержит счетчиквенно к .первому и второму выходампервог бэтапов, дешифратор этапов, счетчикпервого лока памяти, третий выход итераций, д ифра р р ц рщи . низатор, четыре сдвиговых регистра,входами первого и второго элеменпервый и второй коммутаторы, шестьтов , четвертыи выход блока управлетриггеров, тридцать элементов И,ния подключен к входу первого форми- тринадцать элементов ИЛИ и шесть элерователя адреса, пятый выход блока ментов НЕ, причем выход первого элеуправления соединен с входом управпения приемом инф ацм информации а ифметичес.мента НЕ соединен с первым входомр фметичес ,первого элемента И, выход которогопервому входу первогокого блока, выходы действительной .:,подключен к первомучасти первого и третьего операндов . элемен ИЛИнта , выход которого соеди3 10864 нен с тактовым входом счетчика этапов, выход которого подключен к входу дешифратора этапов, первый выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом второго элемента НЕ и первым и входом второго элемента И, второй вход которого объединен с первыми входами третьего, четвертого, пятого элементов И, вторым входом 10 первого элемента И и счетным входом первого триггера, второй выход дешифратора этапов соединен с первым входом третьего элемента ИЛИ, вторым входом второго элемента ИЛИ, входом первого элемента НЕ, вторым входом пятого элемента И и вторым входом четвертого элемента И, выход которого соединен с тактовым входом счетчика итераций, выход которого соеди- щ нен с третьим входом пятого элемента И, выход которого подключен к второму входу первого элемента ИЛИ, третий выход дешифратора этапов соединен с первым входом четвертого эле- д 5 мента ИЛИ, вторым входом третьего элемента ИЛИ и третьим входом второго элемента ИЛИ, четвертый выход дешифратора этапов подключен к второму входу четвертого элемента ИЛИ и третьему входу третьего элемента ИЛИ, первый выход первого коммутатора соединен с первым входом четвертого элемента И и входом синхронизатора, выход которого соединен с первым вхо 35 дом шестого элемента И, первым вко- до.1 пятого элемента ИЛИ и единичным входом второго триггера, выход которого подключен к первому входу седьмого элемента И, выход которого сое О динен с тактовым входом первого регистра сдвига, выход которого соединен с вторым входом пятого элемента ИЛИ, первыми входами восьмого, девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого и пятнадцатого элементов И, второй выход первого коммутатора соединен с нулевым входом второго триггера и входом первого сдвигового регистра, управляющий вход которого подключен к выходу пятого элемента ИЛИ, выход синхронизатора соединен с первым входом шестого элемента ИЛИ, выход которого соединен с55 входом второго сдвигового регистра, выход которого подключен к первому входу седьмого элемента ИЙИ, второй вход которого соединен с выходом 38 6шестого элемента И, второй вход которого объединен с первым входом шестнадцатого элемента И, вторым входомчетырнадцатого элемента И и подключен к четвертому выходу дешифратора этапов, выход третьего элемента ИЛИподключен к вторым входам тринадцатого элемента И и восьмого элемента И,выход которого соединен со счетнымвходом третьего триггера, единичныйвыход которого подключен к первымвходам семнадцатого, восемнадцатогоэлементов И, вторым входом десятого,одиннадцатого, пятнадцатого, шестнадцатого элементов И и третьему входу четырнадцатого элемента И, выходы второго и третьего элементов И соединены соответственно с единичным и нулевым входами третьего триггера, нулевой выход которого подключен к второму входу девятого элемента И и к третьему входу тринадцатого элемента И,выход которого соединен с первым входом восьмого элемента ИЛИ, второйвход которого является четвертым входом блока управления, второй выходдешифратора этапов соединен с вторымвходом восемнадцатого элемента И итретьим входом девятого элемента И,выход которого подключен к первомувходу девятого элемента ИЛИ, второй вход которого соединен с выходом десятого элемента И, третий вход которого объединен с вторым входом семнадцатого элемента И, первым входом первого коммутатора и подключен к выходу четвертого элемента ИЛИ, пятый выходдешифратора этапов соединен с вторымвходом двенадцатого элемента И, выходкоторого соединен с третьим входомдевятого элемента ИЛИ и является пятнадцатым выходом блока управления,выходы семнадцатого, восемнадцатогоэлементов И и девятого элемента ИЛИсоединены соответственно с первым,вторым и третьим входами второго коммутатора, первый и второй выходы которого являются соответственно двенадцатым и тринадцатым выходами блока управления, первый выход дешифратора этапов является третьим выходомблока управления и подключен к входутретьего элемента НЕ, выход которогосоединен с первым входом девятнадцатого элемента И второй вход которогоподключен к выходу четвертого элемен.а Й, второй вход которого подключенк выходу четвертого элемента НЕ, входкоторого соединен с выходом шестнад7 1086 цатого элемента И, выход которого является вторым выходом блока управ" ления, а выход девятнадцатого элемента И является первым выходом блока управления, третий выход первого коммутатора соединен с единичным входом четвертого триггера, единичный выход которого подключен к третьему входу пятнадцатого элемента И, выход которого соединен с нулевым входом четвертого триггера и вторым входом шес" того элемента ИЛИ, третий вход которого соединен с выходом четырнадцатого элемента И, управляющие входы синхронизатора, второго сдвигового регистра и второй вход седьмого элемента И объединены и являются третьим входом блока управления, выход восьмого элемента ИЛИ соединен с вторым входом первого коммутатора и входом третьего сдвигового регистра, выход которого подключен к первому входу десятого элемента ИЛИ и единичному входу пятого триггера, единичный вы" ход которого соединен с первым входом двадцатого элемента И, выход которо" го подключен к тактовому входу четвертого сдвигового регистра, выход которого подключен к третьему входу первого коммутатора и первым входом двадцать первого, двадцать второго,30 двадцать третьего и двадцать четвертого элементов И, первый выход первого коммутатора соединен с нулевым входом пятого триггера и управляющим входом четвертого сдвигового регистра, вход которого подключен к выходу десятого элемента ИЛИ, второй вход которого соединен с первыми входами двадцать пятого, двадцать шестого, двадцать седьмого, двадцать вось" 4 О мого, двадцать девятого элементов И, вторым входом двадцать третьего элемента И и подключен к единичному выходу шестого триггера и образует восьмой выход блока управления, нулевой выход шестого триггера подключен к первому входу тридцатого элемента И, второму входу двадцать второго элемента И и является седьмым выходом блока управления, выход третьего 5 О элемента ИЛИ соединен с вторым входом двадцать четвертого элемента И, выход которого подключен к счетному входу шестого триггера, единичный и нулевой входы которого соединены 55 с выходами соответственно второго . и третьего элементов И, второй выход дешифратора этапов соединен с вторы- . 438 8ми входами двадцать пятого, тридцатого и двадцать шестого элементов И,первый выход дешифратора итерацийсоединен с третьим входом двадцатьпятого и тридцатого элементов И ивходом пятого элемента НЕ, выход которого подключен к третьему входудвадцать шестого элемента Я, выходкоторого соединен с первым входомодиннадцатого элемента ИЛИ, второйвход которого объединен с первым входом двенадцатого элемента ИЛИ и подключен к выходу двадцать пятого элемента И, выход тридцатого элемента Исоединен с вторым входом двенадцатогоэлемента ИЛИ, выход четвертого элемента ИЛИ подключен к второму входудвадцать седьмого элемента И, третьему входу двадцать третьего элемента Ии входу шестого элемента НЕ, выходкоторого подключен к третьему входудвадцать второго элемента И, выходкоторого подключен к первому входутринадцатого элемента ИЛИ, второйвход которого соединен с выходомдвадцать третьего элемента И, третийвыход дешифратора итерацийявляетсяшестью выходом блока управления и соединен с вторым входом двадцать восьмого элемента И, выход которого является девятым выходом блока управления, четвертый выход дешифратораэтапов подключен к второму входудвадцать девятого элемента И, выходкоторого является десятым выходомблока управления, выходы одиннадцатого, двенадцатого и тринадцатого элементов КОИ и выход двадцать седьмогоэлемента И соединены соответственнос четвертым, пятым, шестым и седьмымвходом второго коммутатора, второйвыход двадцатого элемента И и тактовый вход третьего сдвигового регистра объединены и образуют третий входблока управления, первый, второй,третий и четвертый выходы дешифратора итерации являются четырнадцатымвыходом блока управления, выход первого триггера соединен с четвертымвходом первого коммутатора и восьмымвходом второго коммутатора и является одиннадцатым выходом блока управления, первый выход дешифратора этапов является третьим выходом блокауправления, выходы четвертого и седьмого элементов ИЛИ являются четвертым выходом блока управления, выхододиннадцатого элемента И, выходывторого и третьего сдвиговых регистров и выход восьмого элемента ИЛИ образуют пятый выход блока управления, а пятый и шестой входы первого коммутатора являются соответственно первым и вторым входами блока управ ления.На фиг. 1 представлена схема процессора; на фиг, 2 - 10 - соответственно арифметический блок, формирователь адресов постоянной памяти, формирователь адресов (оперативной памяти), блок управления, узел этапов, узел управления считыванием, узел управшвния записью, входной и выходной коммутаторы. 15Процессор быстрого преобразования Фурье содержит арифметический блок 1, блоки (оперативной) памяти 2, 3, блок,постояннойпамяти 4, формирователь адресов (постоянной памяти) 5, 20 формирователи адресов (оперативной памяти) 6, 7, блок управления 8, четыре элемента 2 И-ИЛИ 9-12, два элемента И 13 и 14, два элемента ИЛИ 15 и 16, два сумматора по модулю 2 17 и 18, элементы НЕ 19 и 20, информационные входы 21, 22, тактовый вход 23, вход синхронизации приема чисел 24, информационные выходы процессора 25, 26, выход синхронизации 30 выдачи чисел 27, выходы 28-41 блока 8, выход 42 элемента НЕ 19, выходы 43-44 формирователей 6 и 7 соответственно.На фиг. 2 представлена функциональная схема арифметического блока 1, который соответствует вычислительному устройству прототипа и содержит регистры 45 реальной и 46 мнимой частей первого числа иэ пары 40 обрабатываемых комплексных чисел, регистры 47 и 48 реальной и мнимой частей комплексного весового коэффициента, матричные умножители 49-52, сумматоры 53, 54, регистры 55 реаль ной и 56 мнимой частей второго числа из пары обрабатываемых комплексных чисел, сумматоры 57-60, регистры 61, 62 хранения реальной части соответственно первого и второго комплексного 5 О результата вычислений и регистры 63, 64 хранения мнимой части соответственно первого и второго комплексного результата вычислений.На фиг. 3 представлена, функцио , нальная схема формирователя адресов постоянной памяти 5, который содержит счетчик адреса 65 на в разрядов,элемент НЕ 66, группу элеменуов 2 ИИЛИ 67- 67На фиг, 4 представлена функциональная схема формирователя адресов(оперативной памяти) 6 (7), которыйсодержит регистр адреса на е разрядов, состоящий из триггеров 681- 68 ,элемент И на (м) вход 69, элемент ИЛИ на (в) вход 70, двухвходовые элементы И 71, 72, двухвходовые элементы ИЛИ 73 - 73элемен 1 п-фты НЕ 741 - 74 двухвходовой элемент И 75, две группы трехвходовыхэлементов И 761 - 76., И 771.77 и, двухвходовые элементы ИЛИ 78,79 - 79 щ, сумматоры по модулю 280, - 80 , мультиплексоры 81., - 81Фдля выдачи кода адреса.На фиг. 5 представлена структурная схемаблока управления 8, который содержит узел этапов 82, раскрытый на фиг. 6, узел управления считыванием 83, раскрытый на фиг. 7,узел управления записью 84, раскрытый на фиг. 8, входной коммутатор 85,раскрытый на фиг. 9, и выходнойкоммутатор 86, раскрытый на фиг. 10,На фиг. 6 представлена функциональная схема узла этапов 82. Расположение входа и выходов. узла соответствует расположению их на фиг. 5.Узел содержит счетчик этапов 87,дешифратор этапов на пять выходов 88,счетчик итераций 89, дешифратор итераций на в выходов 90, триггер 91,элементы НЕ 92 и 93, элементы И 94 -97 (трехвходовой) элемент И 98,(двухвходовые) элементы ИЛИ 99 и 100и (трехвходовые) элементы ИЛИ 101и 102. На фиг. 7 представлена функциональная схема узла управления считыванием 83. Расположение входов и выходов узла соответствует расположению их на фиг. 5, Узел содержит синхронизатор 103, триггеры 104 - 106, сдвиговые регистры (на 4 разряда) 107 и 108, выполняющие роль элементов задержки, (двухвходовые) элементы И 109-117, (двухвходовые) элементыИЛИ 118 - 120, (трехвходовые) элементы И 121 " 125, (трехвходовые) элементы ИЛИ 126 и 127 и элемен" ты НЕ 128 и 129.На фиг, 8 представлена функциональная схема узла управления записью 84, Расположение входов и выходов узла соответствует расположениюих на фиг. 5. Узел содержит сдвиговые регистры 130 и 131 (на 4 разряда), выполняющие роль элементов задержки, триггеры 132 и 133, (двухвходовые) элементы И 134 - 139 (двухвходовые) 5 элементы ИЛИ 140-143, элементы НЕ 144 и 145, (трехвходовые) элементы И 146 - 150;На фиг9 представлена функциональная схема входного коммутатора, который содержит элементы 2 ИИЛИ 151-155, (трехвходовые) элементы И 156 и 157, (двухвходовые) элементы ИЛИ 158 и 159 и элемент НЕ 160. Расположение выходов соответствует расположению их на фиг, 5.На фиг. 10 представлена функциональная схема выходного коммутатора 86, который содержит (двухвходовые) элементы И 161 и 162, элементы 2 ИИЛИ 163-168 и элемент НЕ 169. Расположение входов коммутатора 86 соответствует расположению их на фиг. 5.Для пояснения работы процессора рассмотрим реализуемый в нем алгоритм быстрого преобразования Фурье (БПФ).Входная последовательность Я, где 1 =О, 1, 2, ,М, преобразуется в комплексную последовательность 30 У), где 1 =О, 1, 2й/7-1, путемпредставления каждой пары со; седних отсчетов комплексным числом, причем четные отсчеты Ьо,5 5,1 -Дя 7) считаются реальными, а нечет ные (5, 53, б) - мнимыми частями комплексных чисел. Вычисление коэффициентов фурье от преобразованной последовательности заключается в вычислении промежуточных коэф фициентов по базовым формулам алгоритма БПФ:А;(3)= А; (1)+А; (к) Фм, (1)А; (к) =А(1) -А; (к) ад, (2) где 1 - номер текущей итерации, 451 1, 2, 3 щ, т= Во( И,%М - значение комплсксного весового коэффициента.Значениеравно двоичной инверсии кода номера зоны вычислений в итера ции. Так, для двоичного кода 61, О 7, й ,щ, а, двоично-инверсный код будетц, а, а 7, а. Код номера зоны представляется е-разряд. - ным двоичным кодом. 55Номера зон на итерациях будут:с1=0 для первой итерации;1=0,1 для второй итерации;( 1 =0,1,2,3М/1-1 для последнейитерации.Так как преобразованнаяпоследовательность стала в два раза короче исходной, то количество итераций для вычисления будет на единицу меньше, а емкость оперативной памяти сокращается вдвое. Соответственно сокращается время вычисления на каждой итерации в два раза.После вычисления промежуточных ко-. эффи.иентов производится вычисление коэффициентов Фурье по формулам:А +А А -А1 И/2-а 1 МР+,- фМ (51К И/7- В 1 с ММ- М 6 . . ЮМ(4.1. где 1 = Г 1;к =1, 2, ,(М);А и А, 1, - промежуточные коэффициейты, вычисленные по формулам (1) и (2).Вычисление по формулам (3) выполляется в два этапа. На первом производится вычисление выраженийАА М А- АМ- -( зом.Перед вычислением коэффиц Фурье в блок оперативной пам вводится последовательность енто ти 3 одных и (б 121После вычисления выражений (5) выполняется второй этап, заключающийся в вычислении коэффициентов Фурье по формулам (3) и (4), аппаратная реализация которых такая же, как и базовых формул (1) и (2). Отличие заключаетеяв формировании адресов весовых коэффициентов %,( и операндов.Следует отметить, что вычисления по формулам (1) - (4) позволяют определить только М/2 коэффициентов Фурье, Однако для спектрального анализа этого вполне достаточно, так как вторая половина спектра симметрична относительно первой.Время вычисления коэффициентов по формулам (3) и (4) равно времени вычисления по базовым формулам (1) и (2) на двух любых итерациях.Процессор работает следующим обра

СмотретьЗаявка

3442140, 24.05.1982

ПРЕДПРИЯТИЕ ПЯ Г-4677

ВЕРШКОВ ВИТАЛИЙ ЭММАНУИЛОВИЧ, ВЕТОХИН ЮРИЙ ИВАНОВИЧ, ГОЛУБЕВА АЛЛА ВСЕВОЛОДОВНА, ПАРФЕНОВ НИКОЛАЙ СЕРГЕЕВИЧ, ПРОКОШЕНКОВ АНАТОЛИЙ ТИМОФЕЕВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: быстрого, преобразования, процессор, фурье

Опубликовано: 15.04.1984

Код ссылки

<a href="https://patents.su/25-1086438-processor-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Процессор быстрого преобразования фурье</a>

Предыдущий патент: Устройство для выполнения быстрого преобразования фурье

Следующий патент: Устройство для обработки статистических данных о работе аппаратуры вычислительных машин и систем

Случайный патент: Стенд для испытания цепных конвейеров и цепных передач