Система оптимизации режимов работы объекта

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

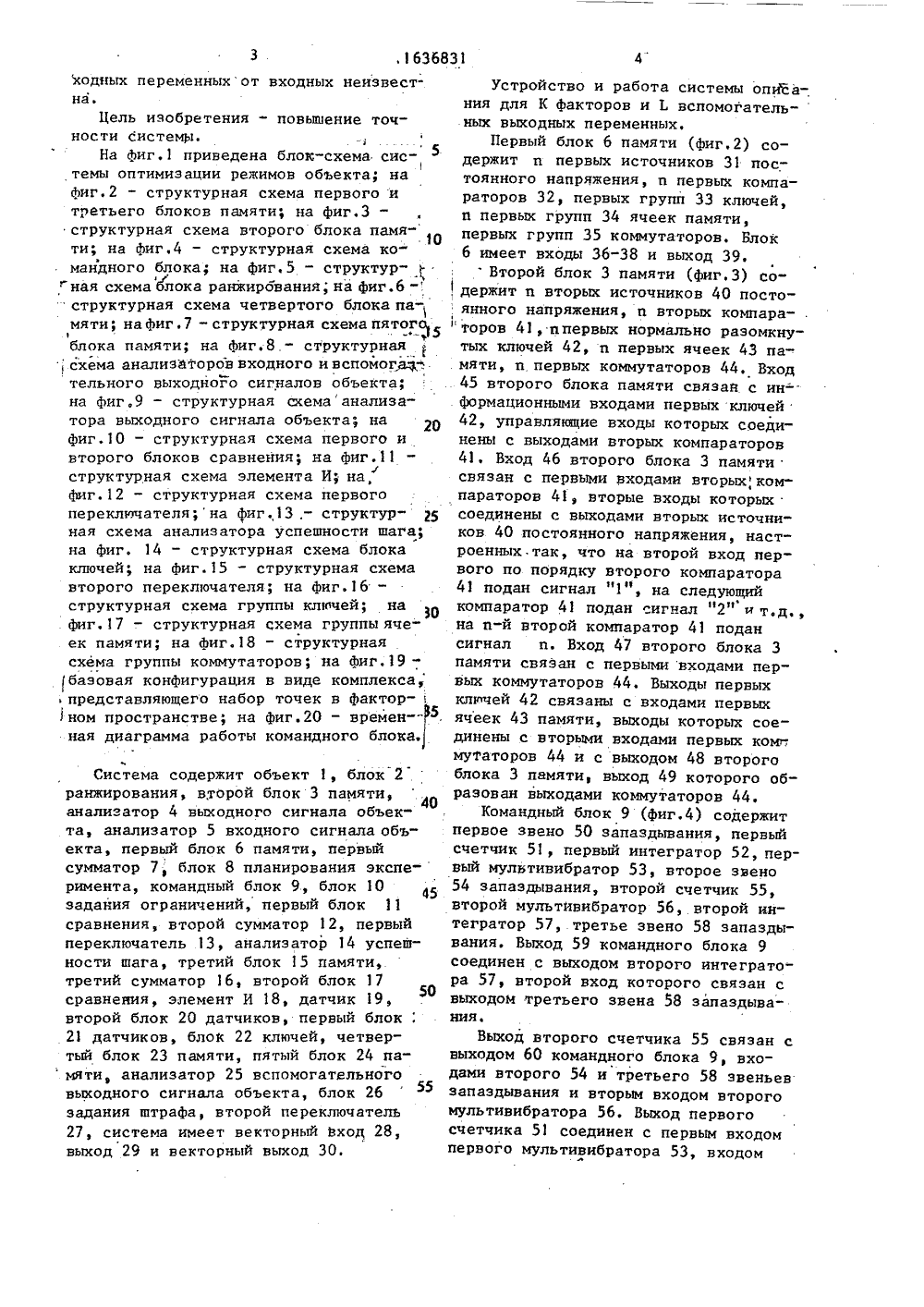

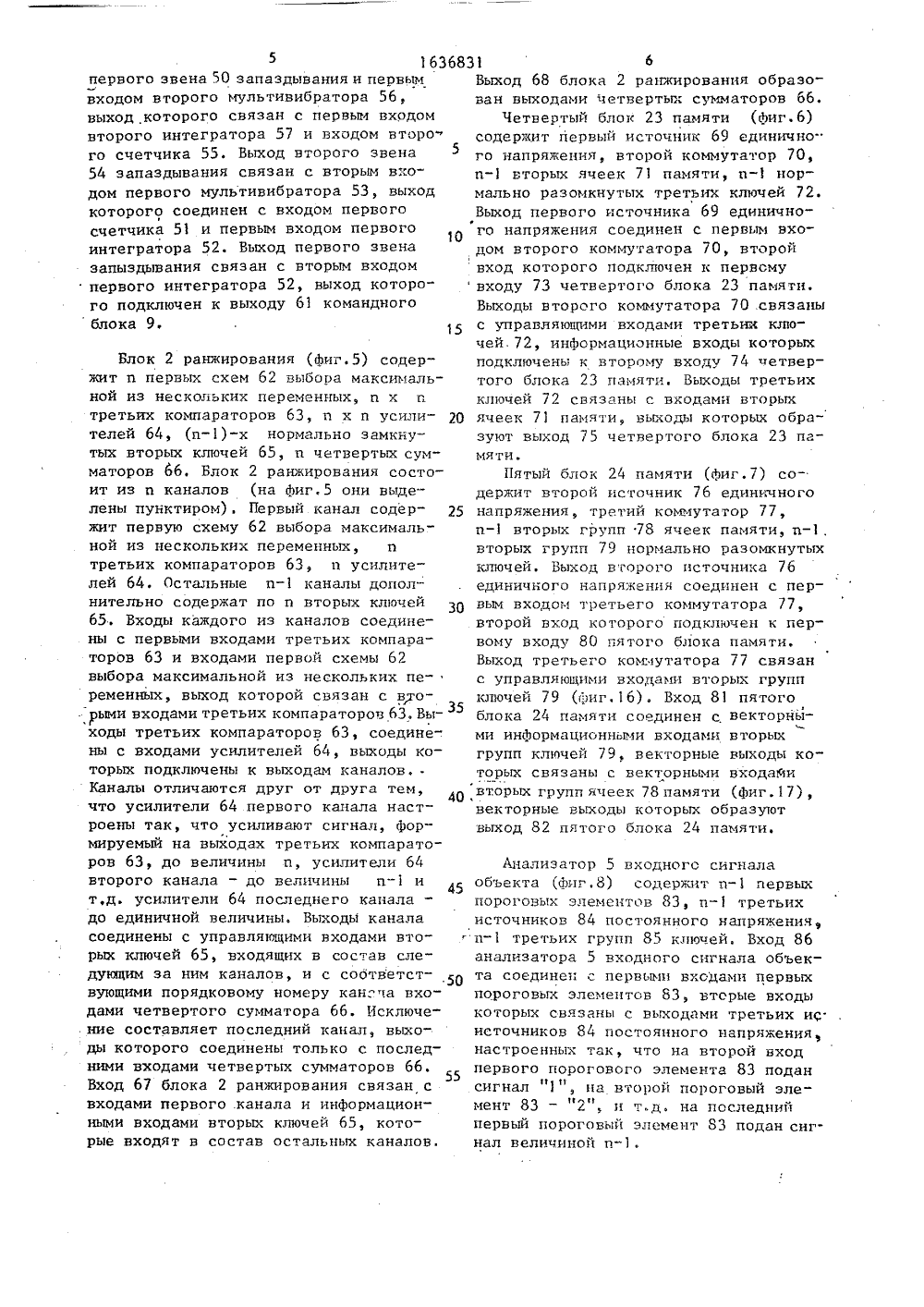

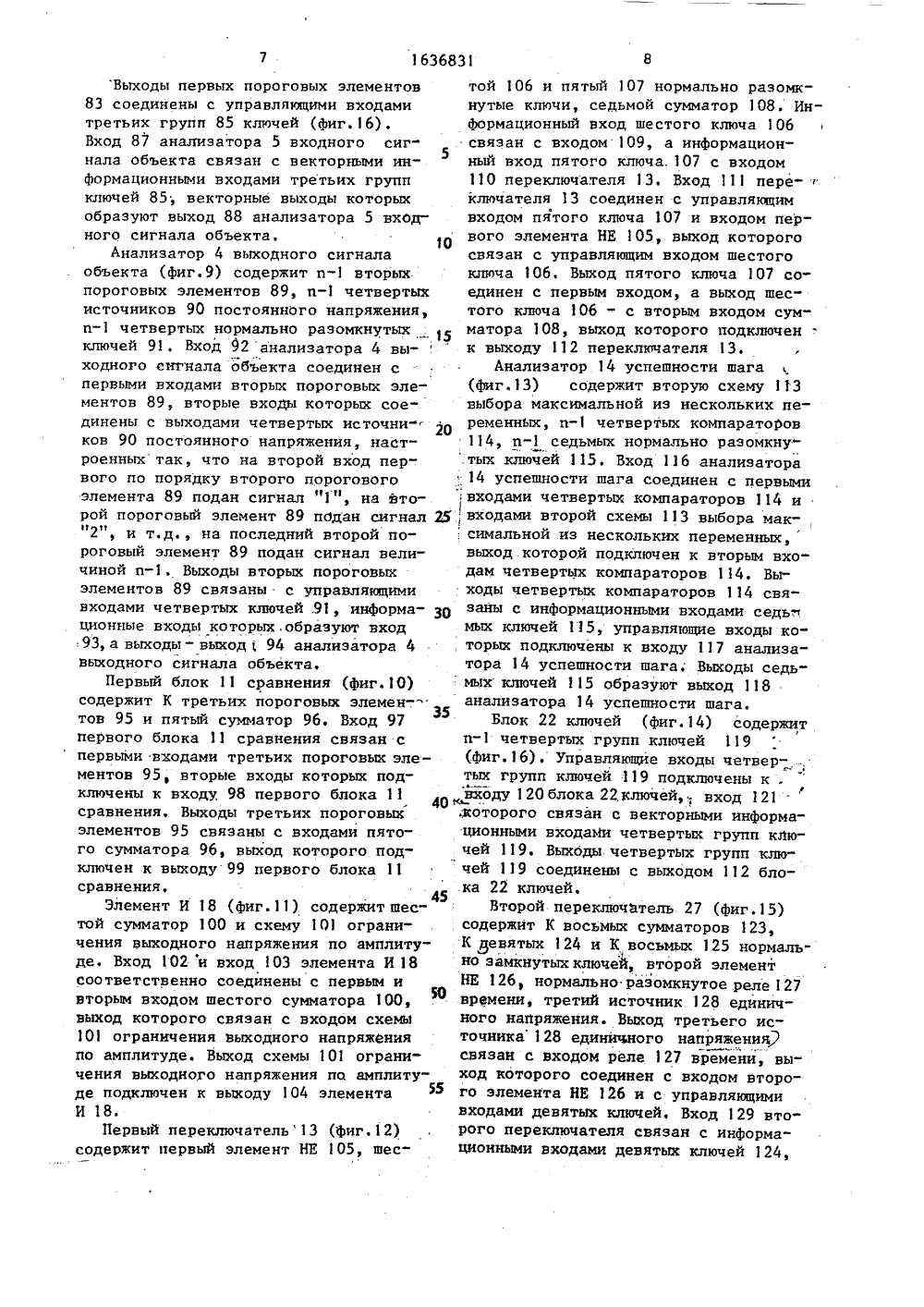

(19 51) 5 С 05 В 13/00 ачен и икс ыбирать на значения движение к раничениям,ска. В сис кии и дзеиногорски т О, 1972.о СССР00, 1984,ет макшности 1 спомогат ательные техничесен ны ограничвия (Факт ных есохас объекта у ошибкой Е тся две яемая и има с ди ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(54) СИСТЕМА ОПТИМИЗАЦИИ РЕЖИМОВ РАБОТЫ ООЬЕКТА,для поиска и поддержания оптимальныхрежимов работы многомерных стохасти:ческих объектов, для которых существуют ограничения на факторы и вспомо гательные выходные переменные, а факторы реализуются с ошибкой, дисперси которой соизмерима с дисперсией Факторов, Цель изобретения - повьппение точности системы. Введение операций сравнения оценок успешности шага, вы бора числа М 1 худших опытов, соотИзобретение относится ккой кибернетике и предназнпоиска и поддержания оптимажимов работы многомерных ских объектов управления, оследующими свойствами: имеювыходные переменные, управл етствующих максимальномуфакторов на вход объектаия М 1 опытов позволяетчередной шаг оптимизациФакторов, обеспечивающихели при приближении к ото повышает точность по темУ введены блок ранжирования, блокключей, анализатор успешности шага,второй и первый блоки датчиков, четвертый и пятый блоки памяти, блок задания штрафа, второй переключатель.В четвертом блоке памяти записываютс значения оценок успеппности шага приразличном числе худших опытов. Анализатор успешности шага выделясимальное значение оценки успешага, информация о нем поступает навторой вход блока ключей, В пятомблоке памяти записаны рассчитанныедля разного числа худших опытов значения факторов на очередной шаг оптимизации. Блок ключей пропускает свыхода пятого блока памяти на первыйвход второго переключателя рассчитанные значения факторов, соответствующих максимальному значению оценки успешности шага. Эти значения черезвторой переключатель поступают навход объекта. 20 ил,льные; на выходные и вспом выходные переменные наложе ения; управляющие воздейст ры Х, подаваемые на вход равления, реализуются с причем дисперсия Е соиэме персией Х; зависимость вы 21 1636831 2296, на выходе которого также формируется сигнал нулевого уровня, поступающий на выход 99 первого блока 11. сравнения,Аналогичным образом происходит про.верка на ограничения рассчитанногозначения У" "+ во втором блоке 17сравнения. Величины ограничений наУ (1 = 1, Ь) Формируются на выходах 10всп,1второй группы задатчиков, состоящей .из К задатчиков, и поступают со второ.го векторного выхода этого блока навход второго блока 17 сравнения, Надругой вход векторного блока 17 срав 15нения с выхода третьего сумматора 16ВСП ЯМ.поступает рассчитанное значение УЦ = 1, Ь). На выходе второго блока17 сравнения Формируется сигнал выполнения или невыполнения ограничений.20В случае выполнения ограничений сигнал имеет нулевой уровень.Сигналы с выходов 99 блоков 11 и 17 )сравнения (фиг.10) поступают на первый 102 и второй 103 входы элемента И 25(Фиг,11), откуда подаются на входышестого сумматора 100. С выхода шестого сумматора 100 сигнал подается навход схемы 101 ограничения выходногонапряжения по амплитуде, с выхода которой поступает на выход 1 04 элементаИ 18. С выхода 104 элемента И :18разрешающий сигнал нулевого уровня поступает на управляющий вход111 первого переключателя 13 (фиг.12),35откуда подается на вход первого элемента НЕ 105. С выхода первого элемента НЕ 105 сигнал подается на уп -равляющий вход шестого ключа 106, наинФормационный вход которого с вхо-., 40да 109 первого переключателя 13 подан сигнал оцейки успешности шагафщ), поступивший с выхода второгосумматора 12. Если сигнал на третьемвходе 111 первого переключателя 13имеет нулевой уровень, то шестой ключ106 открывается и пропускает на второй вход седьмого сумматора 108 сигнал о значении оценки успешности шага Я(ш ). На первом входе пятого суме50матора 108 сигнал отсутствует, таккак пятый ключ 107 закрыт. На выходеседьмого сумматора 108 формируется,сигнал, равный по величине Я(щ), поданный на второй вход седьмого сумматора 108. С выхода 112 первого перег.ключателя 1 3 величина Я(щ) поступает на вход 74 четвертого блока 23 памяти (Фиг.6), на вход 73 которого с выхода 59 командного блока 9 (фиг,4)подается сигнал величиной щ. Сигналвеличиной щ с входа 73 четвертогоблока 23 памяти (фиг.6) подается науправляющий вход второго коммутатора70, на первый вход которого с выходапервого источника 69 единичного напряжения подается сигнал единичнойвеличины, При наличии сигнала величиной щ на управляющем входе второгокоммутатора 70, последний открывается по выходу, порядковый номер кото-,;рого соответствует величине управляющего сигнала. Сигнал единичной вели-.чины с выхода гервого источника 69единичного напряжения через один изоткрытых выходов второго коммутатора70 поступает на управляющий вход од-,ного из третьих ключей 72 и открываетего. Таким образом, при поступлении,сигнала величиной щ 1 на первый вход73 четвертого блока 23 памяти происходит открытие щ-го третьего ключа72, через который на вход щ-й второйячейки 71 памяти подается величинаоценки успешности шага Я(щ), поступающая со второго входа 74. ВеличинаЯ(щ) записывается в щ-й второйячейке 71 памяти при. закрытии щ-готретьего ключа 72, которое происходитпри поступлении на вход 73 четвертогоблока 23 памяти очередного сигналапоследовательности щ . При этом происходит открытие следующего третьегоключа 72, через который в следующейвторой ячейке памяти 21 записываетсязначение оценки успешности шага наочередном шаге оптимизации Ц(ш ),Таким образом, в пятом блоке 24памяти записаны (и) рассчитанныхНМзначений Х , В четвертом блоке 23памяти, в случае выполнения ограничений задаваемых блокам 10 задания ог-.раничений, записаны величины оценокуспешности шагана всех шагах оптимизации,Если рассчитанные значения ХЮна выходе первого сумматора 7 илиспрогнозированные значения У ф "на выходе третьего сумматора 16 неудовлетворяют наложенным на них ограничениям, то на выходе элемента И 18формируется запрещающий сигнал; первый переключатель 13 открывается повторому входу и закрывается по первому. По второму входу первого переключателя 13 в щ-ю ячейку четвертогоблока 23 памяти с выхода блока 26 за24 ности сигналов тп = 1,2,3(п), и расчета в системе оптимизации всех ивариантов шагов оптимизации . в .; ячейках памяти пятого блока 24 памяти записаны ирассчитанных значениййнфакторов Х, а в ячейках памяти четвертого блока 23 памяти записаны соответствующие им оценки успешности, шага с учетом ограничений, На третьем выходе командного блока 9 формируг ется сигнал, поступающий на вход ана. - лизатора 14 успешности шага, в котором выбирается наибольшая иэ всех оценок Я. Сигнач о выбранном значениипоступает на векторный вход блока 22 ключей, на другой вход которого с выхода пятого блока 24 памяти поданы все рассчитанные значения Х. На выходблока 22 ключей поступает знай+чение Х , которое соответствует выбранному наибольшему Я, Это значениеЯФ 1Х через вход второго переклк 1 чателя 27 поступает на вход объекта 1, где реализуется с ошибкой Е, На втором выходе командного блока 9 формируется последовательность сигналов 1,2,3 п. Начинается следующий шаг оптимизации, реализуемый аналогично первому,Это происходит следующим образом.После генерации последовательности сигналов ш, = 1,2,3(п) вторым мультивибратором 56 командного блока 9 (Фиг.4) второй счетчик 55, настроенный по модулю (п), обнуляется и Формирует на выходе сигнал, который подается на входы второго 54 и третьего 58 звеньев запаздывания, второй вход второго мультивибратора 56, вы-: ход 60 командного блока 9 (см.фиг.20). Этот сигнал останавливает второй мультивибратор 56, через второе звено 54 запаздывания запускает первый мульти- вибратор 53, а через третье звено 58 запаздывания обнуляет второй интегратор 57, Первый мультивибратор 53 с ,периодичностью Ю начинает генерировать и импульсов, которые подаются на вход первого счетчика 51 и первый вход первого интегратора 52, с выхода которого последовательность сигналов 2,3,ц поступает на выход 61 командного блока 9 (временная диаграмма работы командного блока приведена на Фиг.20), С выхода 60 командного блока 9 сигнал, сформированный на выходе второго счетчика 55, поступает на вход 117 анализатора 14 успешности шага (Фиг,13), на вход 16 которого с 23 1636831да 1 дия штрафа записывается штраф, заве-,домо наихудший иэ всех возможных значенийЭто происходит следующим образом.Если на ш 1-м шаге оптимизации рассчитанное значение Х , поступающее61ца вход 98 первого блока 11 сравнения(Фиг.16), превышает по величине огра.ничения на входе 9, то на выходахтретьих пороговых элементов 96 Форми"руются сигналы, отличные: от нуля,Эти сигналы поступают на входы пятогосумматора 96, на выходе которого формируется результирующий, отличный отнуля, сигнал, поступающий ца выход 99блока 11 сравнения,Лдалогичдым образом происходит проверка ограничений д " и Формированиейэапрещад 1 щего сигьдала ц случае их цевыпопц.ния во втором блоке 17 сравнения.Отличддые от нуля сит палы с выходов99 блоков 11 и 17 сравнения (Фид,10)поступают ца входы 100 и 103 элемента 25Р (Фиг 11) откуда подаются на Входышестого сумматора 100. Результирующийсигнал с выхода шестого сумматор 100поступает иа вход схем 10. ограциче";,ния .выходноо напряжения цо амплиту-,де,1 а выходе которой Формируется за.прещающий сигнал стандартной величины,Этот сигнал поступает ца выход 104элемента И 18, откуда подается ца вход111 первого переключателя 13 (Фиг,.12).С входа 111 сигнал подается на входпервого элемента НЕ 105 и управляющийвход пятого ключа 107, который открывается и пропускает с входа 110 первого переключателя 13 на первый входседьмого сумматора 108 сигнал о зцачении штрафа, Зеличина штрафа подается на вход 110 первого переключателя13 с выхода блока 10 задания штрафа,где формируется на выходе задатчика,входящего в состав этого блока. Шестой ключ 106 закрыт и поэтому на втором входе седьмого сумматора 108 сигнал отсутствует. На выходе седьмогосумматора 108 формируется сигнал, рав"ный по величине сигналу на его первом5 Овходе. Этот сигнал подается на вход112 первого переключателя 13, откудапоступает на вход 74 четвертого блока23 памяти (Фиг,б), где происходитзапись значения штрафа в дп-й второиячейке памяти.После Формирования на первом выходе командного блока 9 последователь 26163683125(фиг.6) поданы все рассчитанные значе 4ния оценок успешности шага Ч, С входа11 6 анализатора 14 успешности шага(фиг.13) величины Я поступают на вхо 5ды второй схемы 113 выбора максимальной из нескольких переменных и на первые входы четвертых компараторов 114.,:На выходе второй схемы 113 выбора мак симальной из нескольких переменныхформируется сигнал, равный по величи-.не наибольшему значению оценки успешности шага (1, Этот сигнал подается навторые входы четвертых компараторовИ 4, на выходе одного из которых, присовпадении по величине сигналов на.первом и втором входах, формируетсясигнал, поступающий на вход одного изседьмых ключей 115. Сигнал с входа117 анализатора успешности шага посту,пает науправляющие входы седьмых ключей 115, которые открываются, и сигнало наибольшем значении О проходит навыход 118, С выхода 118 анализатора 2514 успешности шага сигнал поступаетна вход 120 блока 22 ключей (фиг.14),откуда подается на управляющий входодной из четвертых групп 11 9.ключейЭтот сигнал поступает на управляющиевходы десятых ключей 132 (фиг,16),которые входят в состав четвертыхгрупп ключей, Одна из четвертых групп.,11 9 ключей открывается и пропускаетс входа 121 на выход 122 блока 22ключей рассчитанное значение Х , со 1 ю 35ответствующее выбранномув анализаторе 14 успешности шага значению Я. Выбранное значение Х " с выхода 122 блоНф 1ка 22 ключей подается на вход 130 вто-,4рого переключателя 27 (фиг.15), откудачерез открытые восьмые ключи 125 поступает на первые входы восьмых сумма,торов 123, на вторых входах которыхсигнал отсутствует, так как девятыеключи 124 закрыты, На выходах восьмыхсумматоров 123 формируются сигналы,равные по величине сигналам на их пер.вых входах .С выходов восьмых сумматоров 123 значение Х" поступает на выл+ход 131 второго переключателя 27, откуда подается на вход объекта 1, Най 1входе объекта 1 значение Х реализуется с ошибкой Е, и начинается следующий этап оптимизации, реализуемыйаналогично первому,55.формула изобретенияСистема оптимизации режимов работыобъекта, содержащая датчик, блок задания ограничений, первый, второй итретий блоки памяти, первый, второйи третий сумматоры, первый и второйблоки сравнения, командный блок, анализатор выходного сигнала объекта,анализатор входного сигнала объекта,первый переключатель, блок планирования эксперимента и элемент И, причемпервый выход объекта связан с входомдатчика, выход которого связан с первым входом второго блока памяти, первый выход которого связан с первымвходом второго сумматора и первымвходом анализатора выходного сигналаобъекта, выход которого связан с вторым входом второго сумматора, выходкоторого связан с первым входом первого переключателя, выход первого бло. -ка памяти связан с первым входом пер-.вого сумматора и первым входом анализатора входного сигнала объекта, вы-.ход которого связан с вторым входомпервого сумматора, выход которого,связан с первым входом первого блокасравнения, второй вход которого связан с первым выходом блока заданияограничений, а выход - с первым входом элемента И, выход которого связан с управляющим входом первого переключателя, а второй вход - с выхо=,.дом второго блока сравнения, первыйвход которого связан с вторым выходомблока задания ограничений, а второйвход - с выходом третьего сумматора,первый вход которого связан с выходомтретьего блока .памяти, первый выходкомандного блока связан с первымивходами анализаторов входного и выходного сигналов объекта, а второйвыход с вторым входом второго и первыми входами первого и третьего блоков памяти, о т л и ч а ю щ а я с ятем, что, с целью повьппения точностисистемы, в нее введены первый и второй блоки датчиков, четвертый и пятый блоки памяти, блок ранжирования,блок ключей, блок задания штрафа, анализатор вспомогательного выходногосигнала объекта, второй переключательи анализатор успешности шага, первыйвход которого связан с выходом четвертого блока памяти, а второй вход - стретьим выходом командного блока,первый выход которого связан с первыми входами четвертого, пятого блоковпамяти и анализатора вспомогательноговыходного сигнала объекта, второй входпятого блока памяти связан с выходомпервого сумматора, а выход - с первым входом блока ключей, второй вход которого связан с выходом анализатора успешности шага, а выход - с первым5 входом второго переключателя, второй вход которого связан с выходом блока планирования эксперимента, выход второго переключателя связан с входом объекта, второй вход четвертого бло-. ка,памяти связан с выходом первого переключателя, второй вход которого связан с выходом блока задания штрафа, первый выход командного блока связан с первым входом анализатора вспомогательного выходного сигнала об ет;.т., вход первого блока датчиков связан с входом объекта, а вы ход с вторым входом первого блока памяти, третий вход которого связан с выходом блока ранжирования и соответственно с третьим и вторым входами второго и третьего блока памяти, выход которого связан также с вторым1входом анализатора вспомогательного выходного сигнала объекта, выход которого связан с вторым входом третьего сумматора, вход блока ранжирования связан с вторым выходом второго блока памяти, третий вход третьего блока памяти связан с выходом второго бло-.:. ка датчиков, вход которой связан с вторым выходом объекта.ходных переменныхот входных неизвестна.Цель изобретения - повышение точности системь 1,На фиг.1 приведена блок-схема системы оптимизации режимов объекта; нафиг,2 - структурная схема первого итретьего блоков памяти; на фиг.З -структурная схема второго блока памя-ти; на фиг,4 - структурная схема командного блока; на фиг,5 - структур- .гная схема блока ранжирования; на фиг.6 -структурная схема четвертого блока памяти; на фиг,7 - структурная схема пятогблока памяти; на фиг.8,- структурная; схема анализаторов входного и вспомога"тельного выходного сигналов объекта;на фиг.9 - структурная схемаанализатора выходного сигнала объекта; нафиг.10 - структурная схема первого ивторого блоков сравнения; на фиг,11структурная схема элемента И; на,фиг,12 - структурная схема первогопереключателя;на фиг,13,- структурная схема анализатора успешности шага;на фиг. 14 - структурная схема блокаключей; на фиг.15 - структурная схемавторого переключателя; на фиг.16 -структурная схема группы ключей; нафиг. 17 - структурная схема группы ячеек памяти; на фиг,18 - структурнаясхема группы коммутаторов; иа фиг,191 базовая конфигурация в виде комплексапредставляющего набор точек в фактор 1 ном пространстве; на фиг.20 - времен 5,ная диаграмма работы командного блока,Система содержит объект 1, блок 2ранжирования, второй блок 3 памяти,анализатор 4 выходного сигнала объекта, анализатор 5 входного сигнала объекта, первый блок 6 памяти, первыйсумматор 7, блок 8 планирования эксперимента, командный блок 9, блок 10задания ограничений, первый блок 11сравнения второй сумматор 12, первыйпереключатель 13, анализатор 14 успешности шага, третий блок 15 памяти,третий сумматор 16, второй блок 17сравнения, элемент И 18, датчик 19,50второй блок 20 датчиков, первый блок .21 датчиков, блок 22 ключей, четвертый блок 23 памяти, пятый блок 24 памяти, анализатор 25 вспомогательноговыходного сигнала объекта, блок 26задания штрафа, второй переключатель27, система имеет векторный Вход 28,выход 29 и векторный выход 30,Устройство и работа системы описания для К факторов и Ь вспомогательных выходных переменных,Первый блок 6 памяти (фиг,2) содержит и первых источников 31 постоянного напряжения, и первых компараторов 32, первых групп 33 ключей,и первых групп 34 ячеек памяти,первых групп 35 коммутаторов. Блок6 имеет входы 36-38 и выход 39.Второй блок 3 памяти (фиг.З) содержит и вторых источников 40 посто янного напряжения, и вторых компара- ." торов 41, ипервых нормально разомкнутых ключей 42, и первых ячеек 43 памяти, и первых коммутаторов 44. Вход45 второго блока памяти связан с ин-.формационными входами первых ключей42, управляющие входы которых соединены с выходами вторых компараторов41, Вход 46 второго блока 3 памятисвязан с первыми входами вторыхкомпараторов 41, вторые входы которыхсоединены с выходами вторых источников 40 постоянного напряжения, настроенных.так, что на второй вход первого по порядку второго компаратора41 подан сигнал "1", на следующийкомпаратор 41 подан игнал "2"т.д.,на и-й второй компаратор 41 подансигнал и. Вход 47 второго блока 3памяти связан с первыми входами нервых коммутаторов 44. Выходы первыхключей 42 связаны с входами первыхячеек 43 памяти, выходы которых соединены с вторыми входами первых коммутаторов 44 и с выходом 48 второгоблока 3 памяти, выход 49 которого образован выходами коммутаторов 44.Командный блок 9 (фиг.4) содержитпервое звено 50 запаздывания, первыйсчетчик 51, первый интегратор 52, первый мультивибратор 53, второе звено54 запаздывания, второй счетчик 55,второй мультивибратор 56, второй интегратор 57,.третье звено 58 запаздывания. Выход 59 командного блока 9соединен с выходом второго интегратора 57, второй вход которого связан свыходом третьего звена 58 запаздыванияаВыход второго счетчика 55 связан свыходом 60 командного блока 9, входами второго 54 и третьего 58 звеньевзапаздывания и вторым входом второгомультивибратора 56. Выход первогосчетчика 51 соединен с первым входомпервого мультивибратора 53, входом1636831 ход оставитель В,Пилишкред Л. Сердокова орректор О. Крав едактор С.Патрушев з 816 Тираж 477 Подписное Государственного комитета по изобретениям и открытиям 113035, Москва, Б, Раушская наб., д. 4/5 НИИПИ КНТ СССР ьский комбинат "Патент", г. Ужгород, ул, Гагарина, 1 оизводственно-и5163683первого звена 50 запаздывания и первымвходом второго мультивибратора 56,выход которого связан с первьпл входомвторого интегратора 57 и входом второго счетчика 55. Выход второго звена 554 запаздывания связан с вторым входом первого мультивибратора 53, выходкоторого соединен с входом первогоФсчетчика 51 и первым входом первогоинтегратора 52. Выход первого звеназапыздывания связан с вторым входомпервого интегратора 52, выход которого подключен к выходу 61 командногоблока 9,15 Блок 2 ранжирования (фиг,5) содержит и первых схем 62 выбора максимальной из нескольких переменных, и х г, третьих компараторов 63, и х и усили телей 64, (и)-х нормально замкнутых вторых ключей 65, и четвертых сумматоров 66. Блок 2 ранжирования состоит из и каналов (на фиг,5 они выделены пунктиром). Первый канал содержит первую схему 62 выбора максимальной из нескольких переменных, и третьих компараторов 63, и усилителей 64. Остальные иканалы дополнительно содержат по и вторых ключей 65. Входы каждого из каналов соединены с первыми входами третьих компараторов 63 и входами первой схемы 62 выбора максимальной из нескольких переменных, выход которой связан с вторыми входами третьих компараторов 63. Вы 35 ходы третьих компараторов 63, соединены с входами усилителей 64, выходы которых подключены к выходам каналов, .Каналы отличаются друг от друга тем, что усилители 64 первого канала настроены так, что усиливают сигнал, формируемый на выходах третьих компараторов 63, до величины и, усилители 64 второго канала - до величины ии45 т,д. усилители 64 последнего канала до единичной величины. Выходы канала соединены с управляющими входами вторых ключей 65, входящих в состав следующим за ним каналов, и с соответствующими порядковому номеру кано а входами четвертого сумматора бб. Исключе.ние составляет последний канал, выходы которого соединены только с последними входами четвертых сумматоров 66. Вход 67 блока 2 ранжирования связан с входами первого .канала и информационными входами вторых ключей 65, которые входят в состав остальных каналов. 1 6Выход 68 блока 2 ранжирования образован выходами четвертых сумматоров 66.Четвертый блок 23 памяти (фиг.б) содержит первый источник 69 единично" го напряжения, второй коммутатор О, ивторых ячеек 71 памяти, инормально разомкнутых третьих ключей 72Выход первого источника 69 единичного напряжения соединен с первым входом второго коммутатора 70, второй вход которого подключен к первому входу 73 четвертого блока 23 памяти. Выходы второго коммутатора 70 .связаны с управляющими входами третьик ключей.72, информационные входы которых подключены к второму входу 74 четвертого блока 23 памяти, Выходы третьих ключей 72 связаны с входами вторых ячеек 71 памяти, выходы которых образуют выход 75 четвертого блока 23 памяти.Пятый блок 24 памяти (фиг.7) содержит второй источник 76 единичного напряжения, третий коммутатор 77, ивторых групп 78 ячеек памяти, и, вторых групп 79 нормально разомкнутых ключей. Выход второго источника 76 единичного напряжения соединен с первым входом третьего коммутатора 77, второй вход которого подключен к первому входу 80 пятого блока памяти, Выход третьего коммутатора 77 связан с управляющими входами вторых групп ключей 79 (фиг.16). Вход 81 пятого3 блока 24 памяти соединен с,векторными информационными входами вторых групп ключей 79, векторные выходы которых связаны с векторными входами вторых групп ячеек 78 памяти (фиг.17), векторные выходы которых образуют выход 82 пятого блока 24 памяти. Анализатор 5 входного сигнала объекта (фиг.8) содержит ипервых пороговых элементов 83, итретьих источников 84 постоянного напряжения, итретьих групп 85 ключей. Вход 86 анализатора 5 входного сигнала объекта соединен с первыми входами первых пороговых элементов 83, вторые входы которых связаны с выходами третьих ис источников 84 постоянного напряжения, настроенных так, что на второй вход первого порогового элемента 83 подан сигнал "1", на второй пороговый элемент 83 - "2", и т.д. на последний первый пороговый элемент 83 подан сигнал величиной и.1636831Выходы первых пороговых элементов той 106 и пятый 107 нормально разомк соединены с управляющими входами нутые ключи, седьмой сумматор 108. Интретьих групп 85 ключей (фиг.16). формационный вход шестого ключа 106 Вход 87 анализатора 5 входного сиг- связан с входом 109, а информационнала объекта связан с векторными ин- ныи вход пятого ключа. 107 с входом5Формационными входами третьих групп 110 переключателя 13. Вход 11 пере" ключей 85; векторные выходы которых ключателя 13 соединен с управляющим образуют выход 88 анализатора 5 вход- входом пятого ключа 107 и входом перного сигнала объекта, вого элемента НЕ 05, выход которогоАнализатор 4 выходного сигнала связан с управляющим входом шестого объекта (фиг,9) содержит ивторых. ключа 106, Выход пятого ключа 107 сопороговых элементов 89, ичетвертых единен с первым входом, а выход шесисточников 90 постоянного напряжения, того ключа 106 - с вторым входом сумичетвертых нормально разомкнутых 15 матора 108, выход которого подключен . ключей 91. Вход 92 анализатора 4 вы-к выходу 112 переключателя 13, ходкого сигнала объекта соединен с Анализатор 14 успешности шага первыми входами вторых пороговых эле- (фиг,13) содержит вторую схему 13 ментов 89, вторые входы которых сое" выбора максимальной из нескольких пединены с выходами четвертых источни Ременных, ичетвертых компараторов ков 90 постоянного напряжения, наст, иседьмых нормально разомкнуроенных так, что на второй вход пер- тых ключей 115. Вход 116 анализатора вого по порядку второго порогового 14 успешности шага соединен с первыми элемента 89 подан сигнал "1 ", на вто- входами четвертых компараторов 114 и рой пороговый элемент 89 подан сигнал Ж, входами второй схемы 113 выбора мак- "2", и т,д на последний второй по- , симальной из нескольких переменных,роговый элемент 89 подан сигнал вели- выход которой подключен к вторым вхочиной п. Выходы вторых пороговых дам четвертых компараторов 114. Выэлементов 89 связаны с управляющими ходы четвертых компараторов 114 свявходами четвертых ключей,91, информа заны с информационными входами седь т ционные входы которых, образуют вход мых ключей 115, управляющие входы ко,а выходы- выход94 анализатора 4 торых подключены к входу 117 анализа- выходного сигнала объекта. тора 14 успешности шага. Выходы седьПервый блок 11 сравнения (фиг. 1 О) мых ключей 115 образуют выход 118 содержит К третьих пороговых элемен-." анализатора 14 успешности шага, тов 95 и пятый сумматор 96, Вход 9735Блок 22 ключей (фиг.14) содержит первого блока 11 сравнения связан с ичетвертых групп ключей 119 первыми входами третьих пороговых эле- (фиг.16), Управляющие входы четвер- ментов 95, вторые входы которых под- тых групп ключей 119 подключены к . ключены к входу 98 первого блока 11 входу 120 блока 22 ключей,; вход 121 . сравнения, Выходы третьих пороговых .которого связан с векторными информаэлементов 95 связаны с входами пято- ционными входами четвертых групп клюго сумматора 96, выход которого под- чей 119. Выходы четвертых групп клюключен к выходу 99 первого блока 11 чей 119 соединены с выходом 112 блосравнения, 45 ка 22 ключей.Элемент И 18 (фиг.11) содержит шес- Второй переключатель 27 (фиг.15) той сумматор 100 и схему 101 ограни- . содержит К восьмых сумматоров 123, чения выходного налряжения по амплиту- К девятых 124 и К восьмых 125 нормальде. Вход 102 и вход 03 элемента И 18 но замкнутыхключей, второй элемент соответственно соединены с первым и . НЕ 126, нормально разомкнутое реле 127 вторым входом шестого сумматора 1 00, времени, третий источник 128 единичЮвыход которого связан с входом схемы ного напряжения. Выход третьего ис ограничения выходного напряжения точника 1 28 единичного напряжения) по амплитуде. Выход схемы 101 ограни- связан с входом реле 127 времени, вычения выходного напряжения па амплиту- ход котоРого соединен с входом второде подключен к выходу 104 элемента 55 го элемента НЕ 126 и с управляющими И 18. входами девятых ключей. Вход 129 втоПервый переключатель 13 (фиг.12) , Рого переключателя связан с информасодержит первый элемент НЕ 05, шес- ционными входами девятых ключей 124, 9 163683выходы которых соединены с вторымивходами восьмых сумматоров 123. Выход второго элемента НЕ 1 26 связан суправляющими входами восьмых ключей115, информационные входы которых подключены к входу 130 второго переключателя 27. Выходы восьмых ключей 125связаны с первыми входами сумматора123, выходы которых образуют выход 13110второго переключателя 27,Группа ключей (Фиг.16), входящаяв состав блоков 5, 6, 15, 22, 24, 25,содержит К нормально разомкнутых десятых ключей 132, управляющие входы которых соединены с входом 133 группыключей, Информационные входы десятыхключей 132 образуют вход 134, а выходы - выход 135 группы ключей.Группа ячеек памяти (фиг.17)., входящая в состав блоков 6, 15, 24, содержит К третьих ячеек 136 памяти,входы которых образуют вход 137, авыход - выход 138 группы ячеек памяти, 25Группа коммутаторов (Фиг.18), входящая в состав блоков б и 15, содер,жит К четвертых коммутаторов 139,вторые входы которых подключены к,первому входу 140 группы коммутаторов. Первые входы четвертых коммутаторов 139 образуют второй векторныйвход 141, а выходы четвертых коммута торов - К векторных выходоь 142 группы коммутаторов,Блок 10 задания ограничений содержит две группы задатчиков, перваясодержит К задатчиков, вторая - 1. задатчиков. Выходы первой группы задатчиков образуют первый выход, выходывторой группы - второй выход блока 10задания ограничений.Третий блок 15 памяти устроен и. работает аналогично первому блоку бпамяти,.45Второй блок 17 сравнения устроени работает аналогично первому 11 блоку сравнения.Второй блок 20 датчиков содержит1 датчиков, входы которых образуютвход, а выходы - выход второго "лока20 датчиков. Датчик 19 реализован аналогично,Первый блок 21 датчиков содержит Кдатчиков, входы которых образуют вход,55а выходы первого блока 21 датчиков,Анализатор 25 вспомогательного выход- .ного сигнала объекта устроен и работает аналогично анализатора 5 входного 1 10сигнала объекта. Блок 8 планированияэксперимента содержит К задатчиков,выходы которых подключены к выходублока 8 планирования эксперимента,Блок 26 задания штрафа содермп задатчик, выход которого связан с входом первого переключателя 13.Работу системы рассмотрим на примере задачи поиска минимума целевойфункции,В исходном состоянии в третьихячейках 136 памяти (Фиг,17) первыхгрупп 33 ячеек памяти первого 6 итретьего 15 блоков памяти (фиг.2),вторых групп 78 ячеек памяти пятогоблока 24 памяти (фиг,7) записаны нули, В первых ячейках 43 памяти второго блока 3 памяти (фиг.З) и вторыхячейках 71 памяти четвертого блока 23памяти (Фиг.б) записапы нули, Первыегруппы 33 кличей первого 6 и третьего 15 блоков памяти (Фиг.2), вторыегруппы 79 кличей пятого блока 24 памяти (Фиг.7), третьи группы 85 ключейанализатора 5 (Фиг,8) и анализатора25, четвертые группы 119 ключей блока22 ключей (фиг,14) закрыты. Первыеключи 42 второго блока 3 памяти(фиг.З), третьи ключи 72 четвертогоблока 23 памяти б, четвертые ключи91 анализатора 4 (Фиг,9), пятый 107 .и шестой 106 ключи первого переключателя 13 (фиг.12), седьмые ключи 115анализатора 14 успешности шага(Фиг.5), и девятые 124 ключи второгопереключателя 27 (Фиг,15) открыты.На выходах первого 53 и второго 56мультивибраторсв, первого 51 и второго 55 счетчиков, первого 50, второго54 и третьего 58 звеньев запаздывания, первого 52 и второго 57 интеграторов, соответственно, и на выходахкомандного блока 9 (фиг,4) нули. Второй переключатель 27 (Фиг. 15) открытпо второму и закрыт по первому входуеОдновременность пуска блоков сис"темы обеспечивается подачей электропитания на блоки в один момент времеНИ аВ момент пуска блок 8 планирования эксперимента Формирует заданныеначальные значения факторов Х 1- 1,К, где К - размерность простран 1636831 12ства факторов. С выхода блока 8 пла- нирования эксперимента через второй вход второго переключателя 27 сигнал о заданных значениях факторов поступа. 5 ет на вход объекта 1, где реализуется с ошибкой 2. Одновременно в момент пуска на втором выходе командного блока 9 с периодичностью Й формируются сигналы величиной 1,2,3 ,.п, где10 п К+1 и задается заранее, исходя из свойств объекта, С второго выхода командного блока 9 сигналы поступают на входы первого б, второго 3 и третьего 15 блоков памяти, где записываются сигналы, приходящие соответственно с первого блока 21 датчиков, датчика 19 и второго блока 20 датчиков; В первом блоке 6 памяти записываются значения входного воздействия Х ; + 2 ( щ 1, К; 1 = 1,и) соответствуйщее ему значение основной выходной У;,и вспомогательной выходной У;(З = ),Ь) переменных записываютсяьспсоответственно во втором 3 и третьем 25 15 блоках памяти. Это происходит следующим образом.В момент пуска на выходах задатчиков, входящих в состав блока 8 планирования эксперимента, формируются сиг. 30 нелы о значениях входных воздействий, которые подаются на вход 129 второго переключателя 27 (фиг,15), где через открытые девятые ключи )24 и восьмые сумматоры 123 поступают на выход 13), С выхода 131 второго переключателя 2735 сигналы о значениях входных воздействий поступают на вход объекта 1, где реализуются с ошибкой 2, поступающей с входа 28 системы.40Реализованные входные воздействия Х+2 измеряются первым блоком 21 датчиков и поступают на вход 36 первого блока 6 памяти (фиг.2), Полученные . значения основной выходной переменной 45 Т на выходе объекта 1 измеряются дат" чиком 19 и поступают на вход 45 второго блока 3 памяти (фиг.З). Полученные значения вспомогательной выходной переменной 1 на выходе объекта 1 изфймеряются вторым блоком 20 датчиков и поступают на вход третьего блока 15 памяти.Одновременно с этим в момент пуска первый мультивибратор 53 командного блока 9 (фиг.4) начинает генерироватьи единичных импульсов с периодично" стью(пК+1, К - число факторов. и - выбирается заранее с учетом . свойств объекта оптимизации). Единичные импульсы подаются на первый входпервого интегратора 52, на выходе которого формируется последовательностьсигналов величиной 1,2,3и, которая".,подается на выход 61 командного блока 9(временная диаграмма работы командногоблока 9 приведена на фиг.20). С выхода 61 командного блока 9 последовательность сигналов поступает на входы37 первого 6 и третьего 15 блоков па д.мяти (фиг.2), и на вход 46 третьегоблока 15 памяти (фиг,З). С входа 37первого блока в памяти (фиг.2) последовательность сигналов величиной 1,2,Зп поступает на первые входы первых компараторов 32, на вторйе входыкоторых с выходов первых источников31 постоянного напряжения поданы сигналы определенной величины. Причем спервого по порядку первого источника31 постоянного напряжения подан сигнал "1", со второго - "2", и т,д., споследнего первого источника 31 постоянного напряжения подан сигнал величиной п. При совпадении по величинезначений сигналов, поступающих на входы первых компараторов 32 с входа 37первого блока 6 памяти и с выходовпервых источников 31 постоянного напряжения, на выходе первого компаратора 32, на входах которого значениясовпали, формируется сигнал подаваемый на управляющий вход одной из первых групп 33 ключей. С управляющеговхода первой группы 33 ключей сигналпоступает на управляющие входы десятых ключей 132 (фиг.16), открывая их,Таким образом, появление последовательности сигналов 1,2,3 п на входе 37 первого блока 6 памяти (фиг.2)вызывает поочередное открытие первыхгрупп 33 ключей. Через информационныйвекторный вход открытой первой группы33 ключей с входа 36 первого блока бпамяти на векторный вход одной из первых групп 34 ячеек памяти поступаютсигналы о значениях входных воэдейст"вий в х-м опыте. Эти сигналы послезакрытия первой группы 38 ключей записываотся в ячейках 136 памяти(фиг.)7), входящий в состав первыхгрупп 34 ячеек памяти,Аналогичным образом происходитзапись значений вспомогательной выход.ной переменной Т1),п в третьемблоке 15 памяти. Эти значения поступают через вторую группу 20 датчиковс выхода 30 объекта 1 на вход третьего блока 15 памяти.Поступающая на вход 46 второго блока 3 памяти последовательность сигналов 1,2,3 и подается на первые вхо 5ды вторых компараторов 41, На вторыевходы вторых компараторов 41 с выходов вторых источников 40 постоянногонапряжения поданы сигналы величинойот 1 до и, таким же образом как и свыходов первых источников 31 постоян, ного напряжения первого блока 6 памяти (фиг,2). При совпадении величинсигналов на входах второго компаратора 4 (Фиг,З) на его выходе Формируется управляющий сигнал, который открьвает один из первых клочей 42. Таким образом, появление последовательности сигналов величиной 1,2,3 и20на входе 46 второго блока 3 памятивызьвает,поочередное открытие первь 1 хключей 42. Сигнал о величине основнойвыходной переменной У, в х-м опыте/с входа 45 второго блока 3 памяти проходит через открытый 1-й первый ключ42 на вход первой ячейки 43 памяти,где записывается. Это происходит призамыкании первого ключа 42 при появлении на входе 46 второго блока 3 памяти очередного сигнала.Таким образом, в первых группах 34ячеек памяти первого 6 (Фиг.2) и .третьего 15 блоков памяти и в первыхячейках 43 памяти второго блока 3 памяти (Фиг.З) записаны величины соот-;,ветственно входных воздействий Х, (1=1, К), выходной вспомогательной переменной У; Ц = 1, 1,) и выходной1основной переменной У-; в и опытах,1, и,40С выхода втарого блока 3 памятисигналы о записанных значениях основной выходной переменной поступаютна вход блока 2 ранжирования, гденаблюдения упорядочиваются по возрас 45танию.Это происходит следующим образом,С выхода 48 второго блока 3 памяти (фиг.З) сигналы о значениях У поступают на вход 67 блока 2 ранжирования (Фиг,5), откуда подаются навходы первого канала и на информационные входы вторых ключей 65, входя -щих в состав остальных каналов. В пер.вом канале блока 2 ранжирования сигналы поступают на входы первой схемы62 выбора максимальной из несколькихпеременных и на первые входы третьих компараторов 63. Навыходе первой схемы 62 выбора максимальной иэ нескольких переменных Формируется сигнал, равный по величине наибольшему по значению сигналу на входах этой схемы.Этот сигнал поступает на вторые входы третьих компараторов 63. При совпадении величин сигналов на входах третьего компаратора 63, порядковый номер которого соответствует порядковому номеру наибольшего значения У в исходной последовательности наблюдений, на выходе последнего Формируется единичный сигнал. Этот сигнал поступает на вход усилителя 64, где усиливается до величины и. Таким образом, на одном иэ выходов первого канала блока 2 ранжирования формируется сигнал величиной и, на остальных выходах этого канала сигналы равны нулю. Сигналы с выходов первого канала поступают на первые входы четвертых сумматоров 66 и на управляющие входы вторых ключей 65 второго канала. При этом второй ключ 65, порядковый номер которого соответствует порядковому номеру наибольшей величины У в исходной последовательности, закрывается, так как на его управляющем входе присутствует3 отличный от нуля сигнал. Далее во втором канале блока 2 ранжирования про-, исходит выбор второй по значению величины У. Выбор осуществляется аналогично работе первого канала, В результате на одном иэ выходов второго канала блока 2 ранжирования Формируется сигнал вепичиной п, на остальных выходах этого канала сигналы равны нулю, Сигналы с выходов второго канала поступают на вторые входы четвертых сумматоров 66 и па управляющие входы вторых ключей 65 третьего канала. Далее в остальных каналах производится выбор третьей, четвертой и т.д, по значению величины У. Таким образом, на входы четвертых сумматоров 66 поданы нули и сигналы, величины которых характеризуют положение выходной переменной У. в итоговой упорядоченной по возрастанию последовательности. На выходах четвертых сумматоров 66 формируются сигналы, определяющие. положение У; в ранжированной последовательности, причем совпадает с порядковыми номерами четвертых сумматоров 66 и соответственно с порядковыми номерами Ув исходной последовательности наблюдений. С выходов четвертых сумматоров бб ранжировочная последователь-. " ность поступает на выход 68 блока 2 ранжирования.С выхода.68 блока 2 ранжирования ранжировочная последовательность пос 5 тупает на входы первого 6, второго 3 и. третьего 15 блоков памяти, после3 чего на выходыблоков записанные сигна" лы подаются упорядочена;10Это происходит следующим образом.Ранжировочная последовательность с выхода 68 блока 2 ранжирования поги дается на вход 38 первого блока 6 па" мяти (фиг,2). Сигналы на этом входе являются управляющими для четвертых коммутаторов 139 (фиг.18), входящих в состав первых групп 35 коммутато- . ров, Четвертые коммутаторы 139 открываются по выходу, порядковый номер которого соответствует величине сигнала, поступающего на первый вход группы 35 коммутаторов (фиг.2) с входа 38 первого блока 6 .памяти. Таким образом, происходит упорядочение зна чений входных воздействий Х, в соответствии с ранжировочной последовательностью. Упорядоченная последовательность Х поступает на вход 39 первого блока 6 памяти.Аналогичным образом происходит упорядочение значений вспомогательных выходных переменных У" в третьемепблоке 15 памяти. 30- 35Ранжировочная последовательность,поступающая с выхода 68 блока 2 ранжирования (фиг.5), поступает на вход47 второго блока 3 памяти (фиг,3),откуда подается на первые входы пер-;, 40вых коммутаторов 44, Первые коммута-:;торы 44 открываются по выходам, по-.ирядковые номера которых соответствуютвеличинам сигналов, поступающих .ндпервые входы первых коммутаторов 44.Таким образом, происходит упорядочение основной выходной переменной У,по возрастанию. Упорядоченная последовательность Т, поступает на выход49 второго блока 3 памяти.,После формирования на выходах блоков памяти упорядоченного массива .наблюдений на выходе командного бло-ка 9 с периодичностью , , Ф,Ь формируется последовательность, сигналовш - 1,2,3(и), второй переключатель 27 закрывается по второму и открывается по первому входу.Это происходит следующим образом. После генерации и импульсов первым мультивибратором 53 (фиг.4) первый счетчик, настроенный по модулю и, обнуляется и формируетна выходе сигнал, который поступает на пер-, вые управляющие входы первого 53, второго 56 мультивибраторов и на вход первого звена 50 запаздывания, Этот сигнал останавливает первый мульти-: вибратор 53, запускает второй мульти- вибратор 56 и через первое звено 50 запаздывания поступает на второй вход первого интегратора 52 и обнуляетего. Второй мультивибратор 56 с пе-,: риодичностью , 3 ф)генерирует иимпульсов, которые подаются на вход второго счетчика 55 и первый вход второго интегратора 57. На выходе второго интегратора 57 формируется последовательность сигналов ш = 1,2,3(ит 1), которая поступает на выход 59 командного блока 9 (временная диаграмма работы командного блока 9 приведе" на на фиг.20).После генерации и импульсов первым мультивибратором 53 командного блока 9 (фиг,4) срабатывает нормально разомкнутое реле 127 времени второго переключателя 27 (фиг15), настроенного на время срабатывания и,Ф. После замыкания нормально разомкнутого контакта реле 127 времени с выхода третьего источника 128 единичного напряжения на вход второго элемента НЕ 126 и на управляющие входы девятых ключей 124 поступает единичный управляющий сигнал. Этот сигнал закрывает девятые ключи 124 и, проходя через второй элемент НЕ 126, поступает на управляющие входы восьмых ключей 125, которые открываются по информационным входам. Таким образом, второй переключатель 27 закрыт по второму и открыт по первому входам.Последовательность сигналов ш1,2,3(и) поступает на входы четвертого 23 и пятого 24 блоков памяти, на входы анализаторов 5,4 и 25На входы анализатора 5, анализатора 4 и анализатора 25 с выходов соответствующих блоков памяти поступают сигна-. лы упорядоченных значений входной, выходной и вспомогательной выходной переменных, Эти же сигналы поступают соответственно на первый 7, второй 12и третий 16 сумматоры. На выходах анализаторов 5,4 и 25 формируются сигналы о первых ш упорядоченных эначе 1636831 1820 ниях соответственно входной, выходнойи вспомогательной выходной перемен-,ных, которые поступают на входы сум- .маторов 7, 12 и вход сумматоре 16 соответственно.5Это происходит следующим образом.С выхода 39 первого блока 6 памяти (фиг,2) упорядоченные значения входных воздействий Х,. поступают на вход 87 анализатора 5 (фиг.8) . на10 , первый вход 86 которого с первого выхода 59 командного блока (фиг.4) подается последовательность сигналов щ 1 = 1,2,3(и). Последователь-: ность щ 1 поступает на первые входы первых пороговых элементов 83, на вторые входы которых с выходов третьих источников 84 постоянного напряжения подаются сигналы определенной величины, Причем на второй вход первого по,порядку первого порогового элемента 83 подан сигнал "1", на второй пороговый элемент - "2" т,д., на последний по порядку первый порого вый элемент 83 подан сигнал величиной и. Первые пороговые элементы 83 пропускают сигнал, начиная с определенной величины, которая определяется величиной сигнала на его вторых входах. Таким образом, последовательность сигналов щ, = 1,2,3(п) на входе 86 анализатора 5 приводит к тому, что на выходах первых пороговыхэлементов 83 последовательно формируются отличные от нуля сигналы. Эти сигналы поступают на вторые входы третьих групп 85 ключей и являются управляющими для входящих в их состав десятых ключей 132 (фиг.16), Третьигруппы 85 ключей последовательно, по .40мере появления.на входе 86 анализато. ра 5 (фиг.8) сигналов щ = 1,2,3(п),открываются и пропускают с входа 87 на выход 88 по щ 1 первых зйачений упоРядоченных входных )воздействий. 45Аналогичным образом на выходе анализатора 25 формируются сигналы о первых щ значениях вспомогательных выВСПходных переменных )( .1С выхода 49 второго блока 3 памяти 50(фиг.З) упорядоченные значения основной выходной переменной У; поступаютна вход 93 анализатора 4 (фиг.9), навход 92 которого с выходя 59 командного блока 9 (фиг.4) подается последовательность сигналов щ= 1,2,3(п), Эта последовательность поступает на первые входы вторых пороговых элементов 89, на в-.орые входы которых.с четвертых источников 90 постоянного напряжения подаются сигналы опре;,деленной величины. Величины сигналовна выходах четвертых источников 90постоянного напряжения совпадают свеличинами сигналов на выходах соответствующих третьих источников 84 постоянного напряжения анализатора 5(фиг,9) приводит к тому, что на выходах первых щ вторых пороговых зле;ментов 89 формируются отличные от нуля сигналы. Эти сигналы поступают науправляющие входы четвертых ключей91, которые пропускают с входа 93анализатора 4 на его выход 94 щпервых значений 7.С выхода 88 аналцзатора 5 (фиг.8)первые щ значений Х поступают навход первого сумматора 7, на другойвход которого с выхода 39 первогоблока 6 памяти (фиг.2) поданы все изначений входных воздействий Х, Ана-логичным образом с выхода анализатора 25 первые щ значении упорядочен 1ной последовательности К поступаютна вход третьего сумматора 16, на другой вход которого с третьего блокаЬСЙ15 памяти поданы все и значений УС выхода 94 анализатора 4 (фиг.9) первые щх значений упорядоченной последовательности У подаются на вход второго сумматора 12, ня другой вход которого с выхода 49 второго блока 3памяти (фиг.З) поданы все и значе-,:ний У,В первом сумматоре 7 рассчитываются значения факторов Х;(1 = 1, К) наочередном шаге оптимизации11, (и-щ ), - ): Ьп -:Первые щх значений факторов Х пос-.тупаютна второй вход, а все п значений Х - на первый вход первого сумматора 7.В третьем сумматоре 16 рассчитывается прогнозируемое значение вспомогательной выходной переменнной У (1=1,.Ь) на очередном шаге оптимизации:щ(6 СП

СмотретьЗаявка

4639592, 19.01.1989

СИБИРСКИЙ МЕТАЛЛУРГИЧЕСКИЙ ИНСТИТУТ ИМ. СЕРГО ОРДЖОНИКИДЗЕ

МЕЛЬНИК ГРИГОРИЙ БОРИСОВИЧ, КАЛИНОГОРСКИЙ НИКОЛАЙ АЛЕКСЕЕВИЧ, КОРШИКОВ СЕРГЕЙ ВАСИЛЬЕВИЧ, КОТУХОВ ВЛАДИМИР ИЛЬИЧ, ШЕРЫШЕВ ЮРИЙ АЛЕКСАНДРОВИЧ, ТУМАНОВ ВЛАДИМИР ПАВЛОВИЧ, ЧУРИЛОВ АНДРЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G05B 13/00

Метки: объекта, оптимизации, работы, режимов

Опубликовано: 23.03.1991

Код ссылки

<a href="https://patents.su/22-1636831-sistema-optimizacii-rezhimov-raboty-obekta.html" target="_blank" rel="follow" title="База патентов СССР">Система оптимизации режимов работы объекта</a>

Предыдущий патент: Регулятор расхода

Следующий патент: Устройство для стабилизации трехфазного переменного напряжения

Случайный патент: Установка для контроля протибопылевых респираторов