Микропрограммируемый векторный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1594557

Авторы: Вейц, Денисенко, Дятчина, Жуков, Криворучко, Левертов, Малюгин, Прангишвили, Соколов, Сперанская, Шевцов

Текст

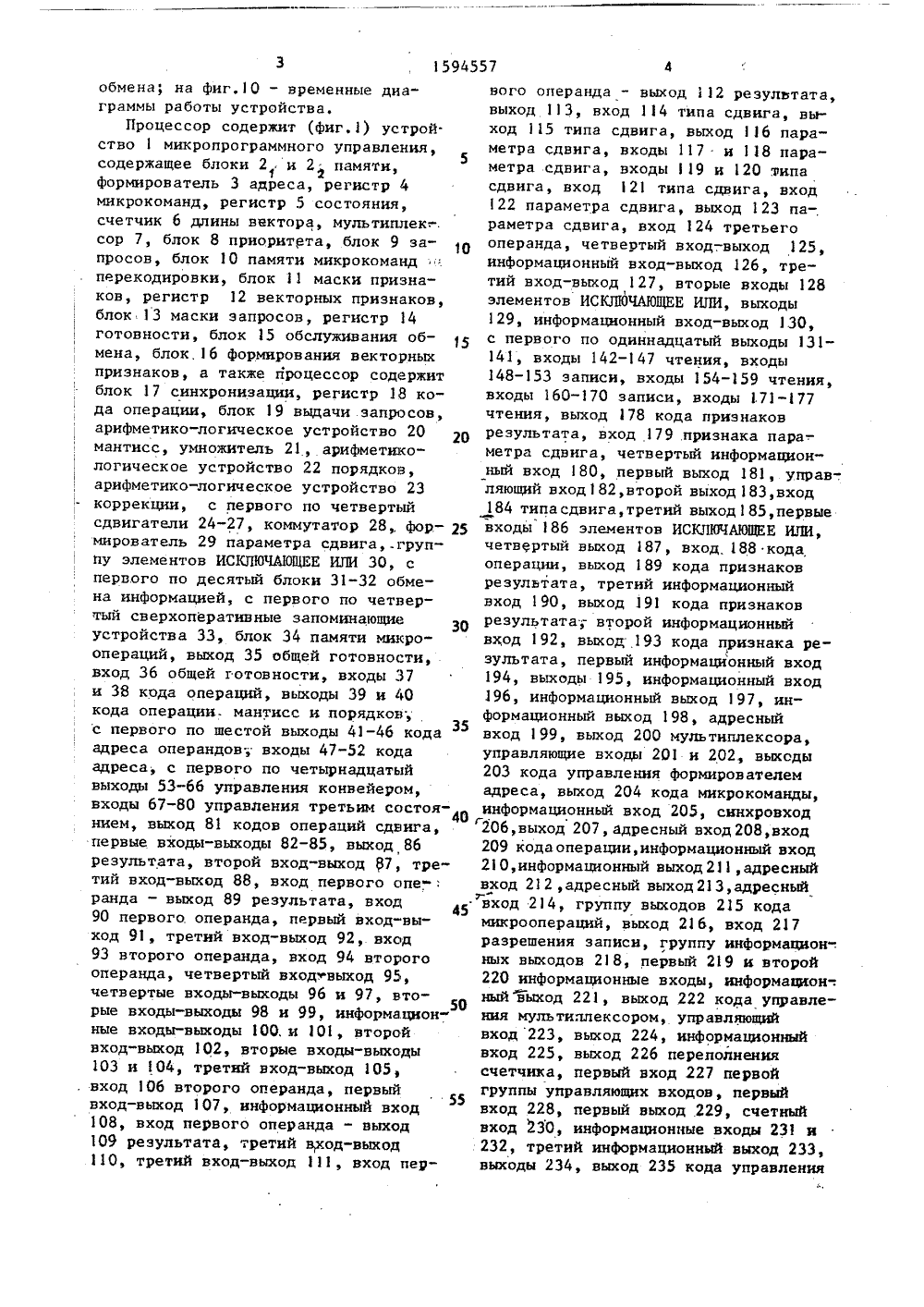

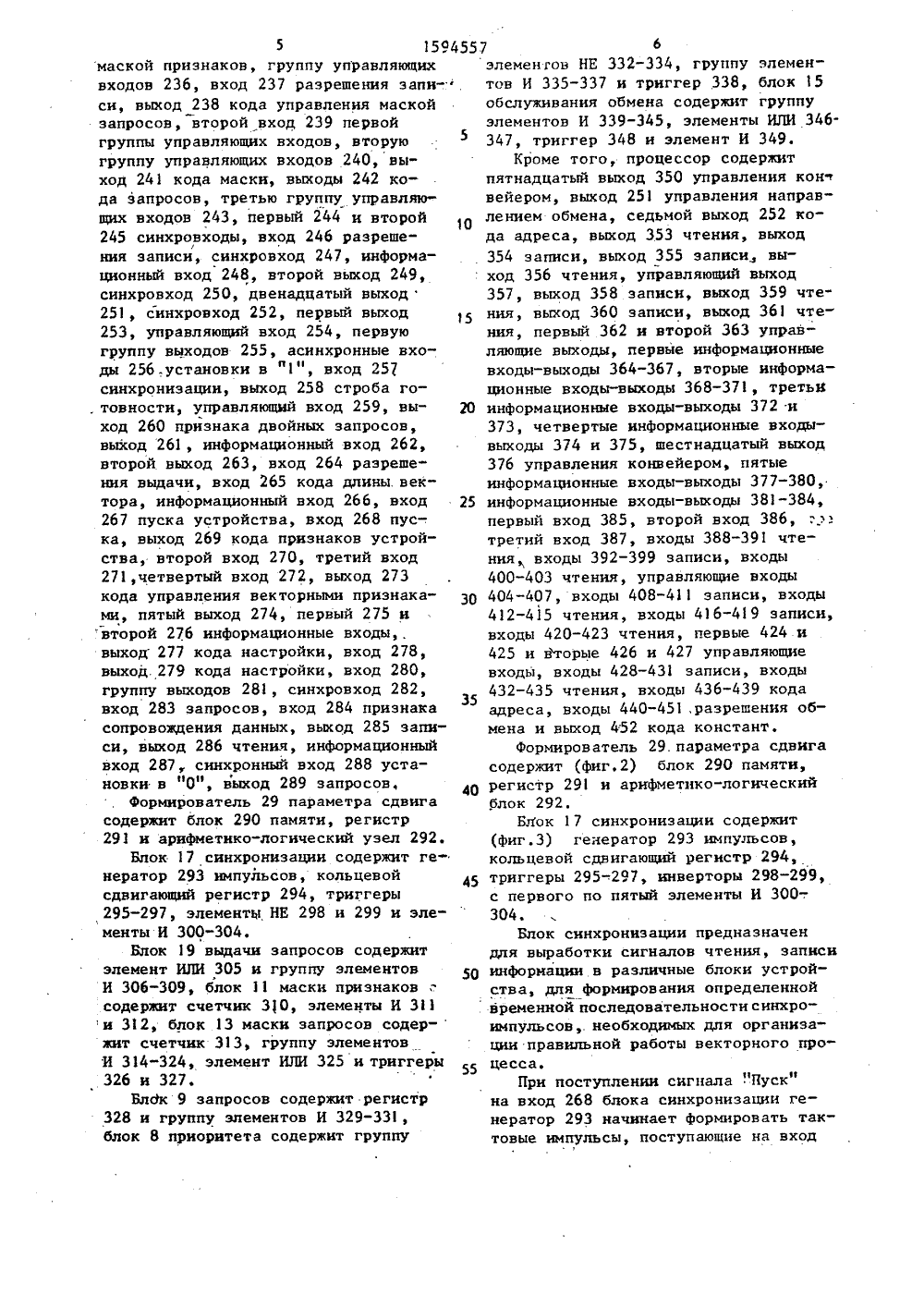

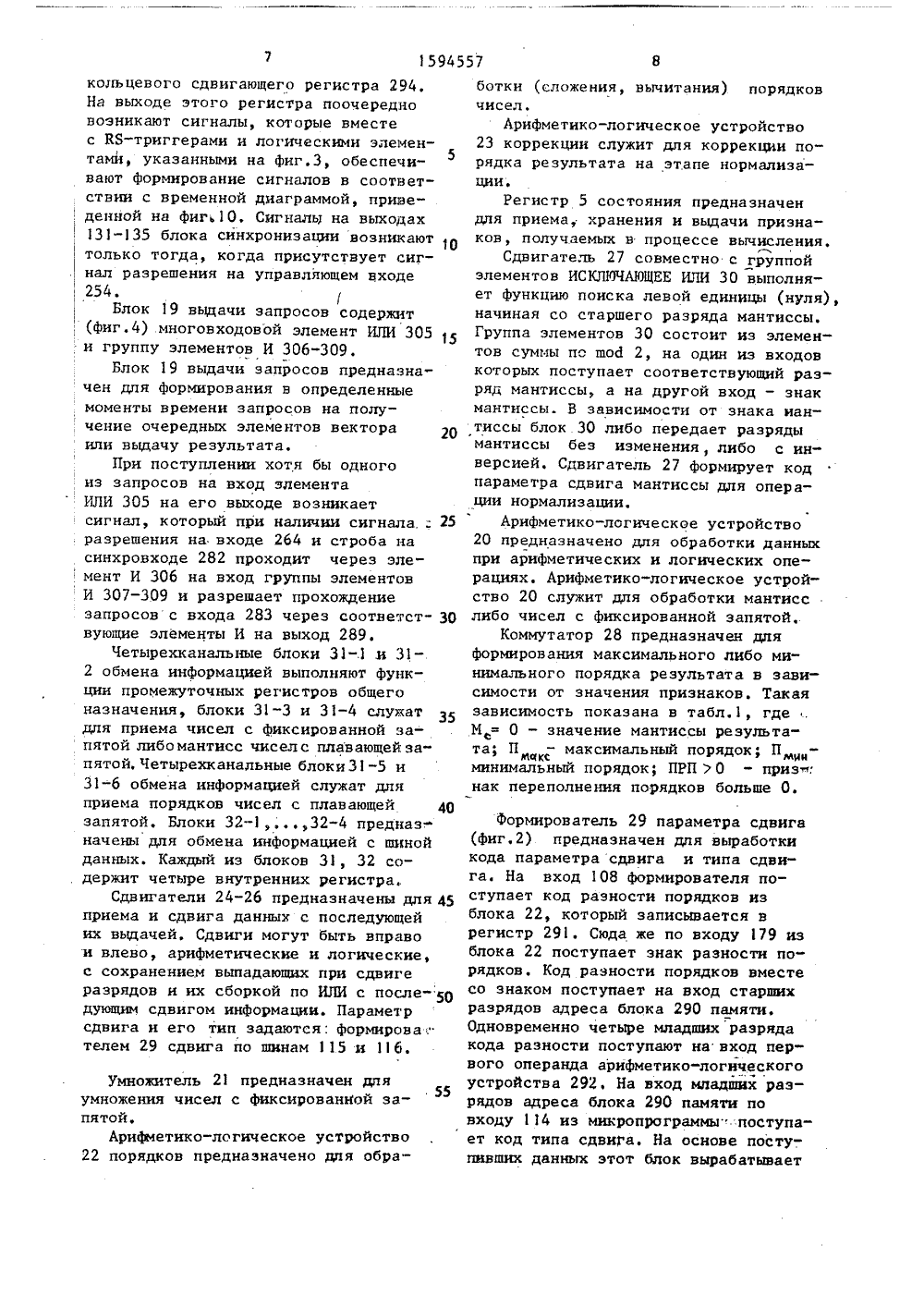

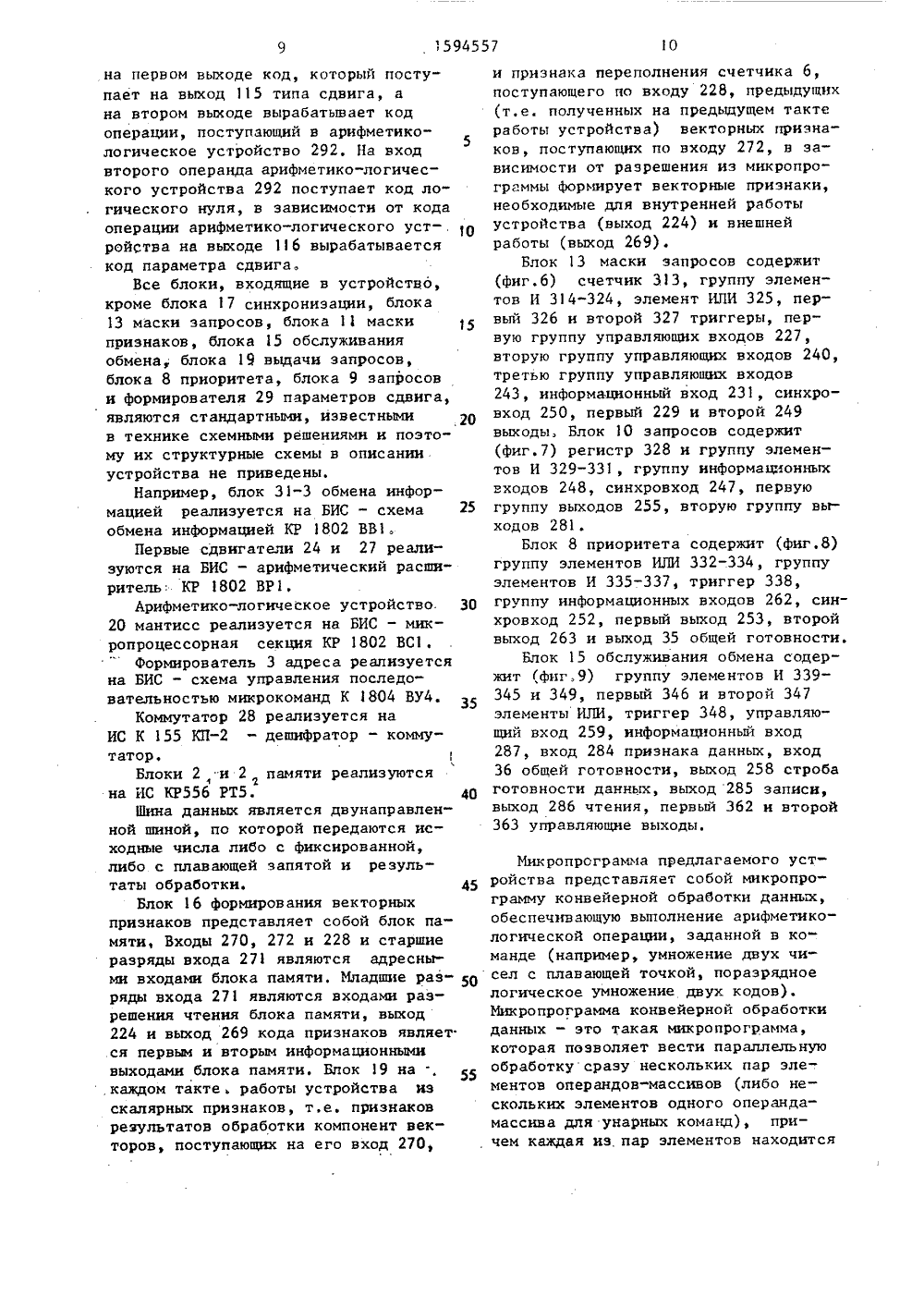

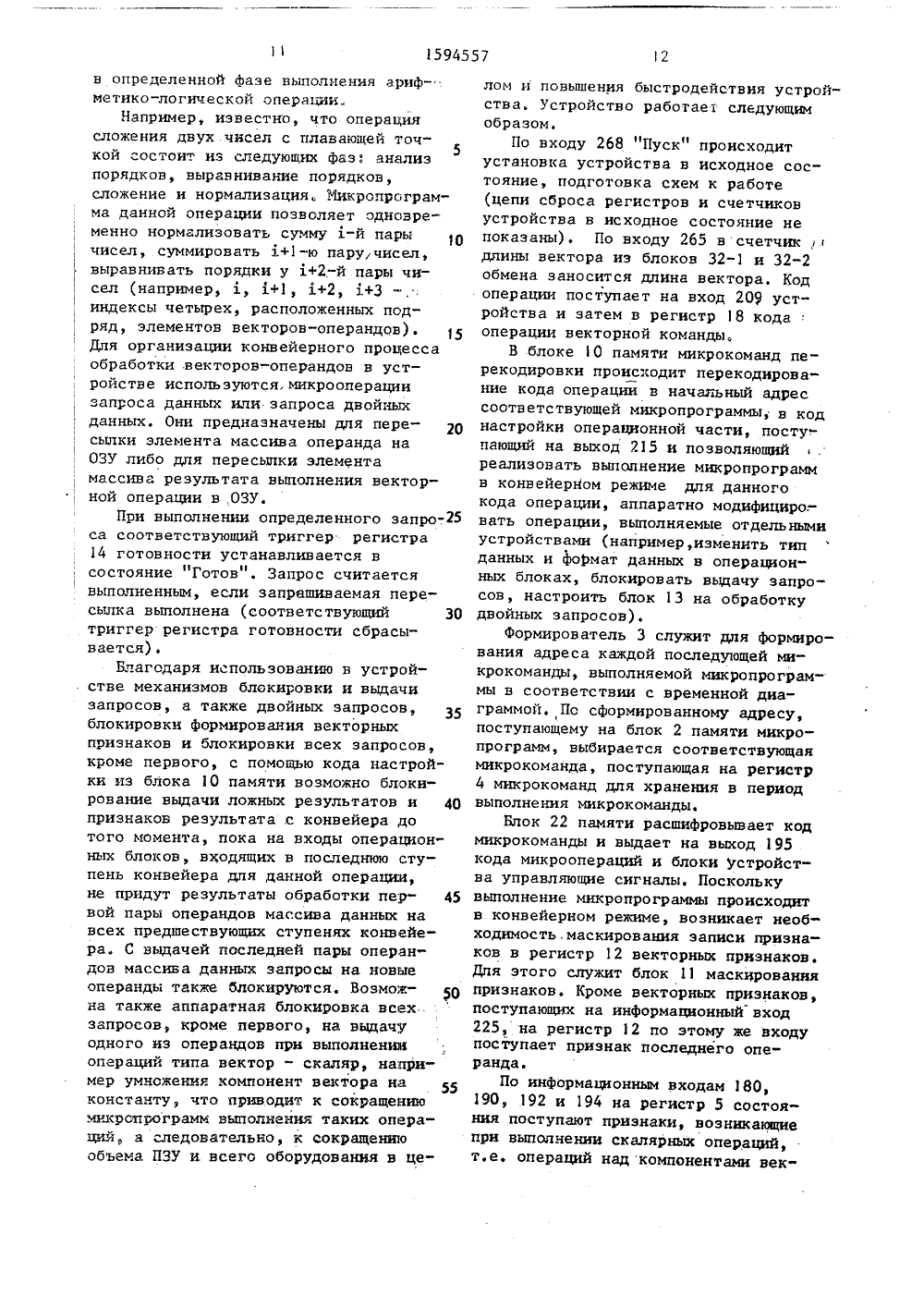

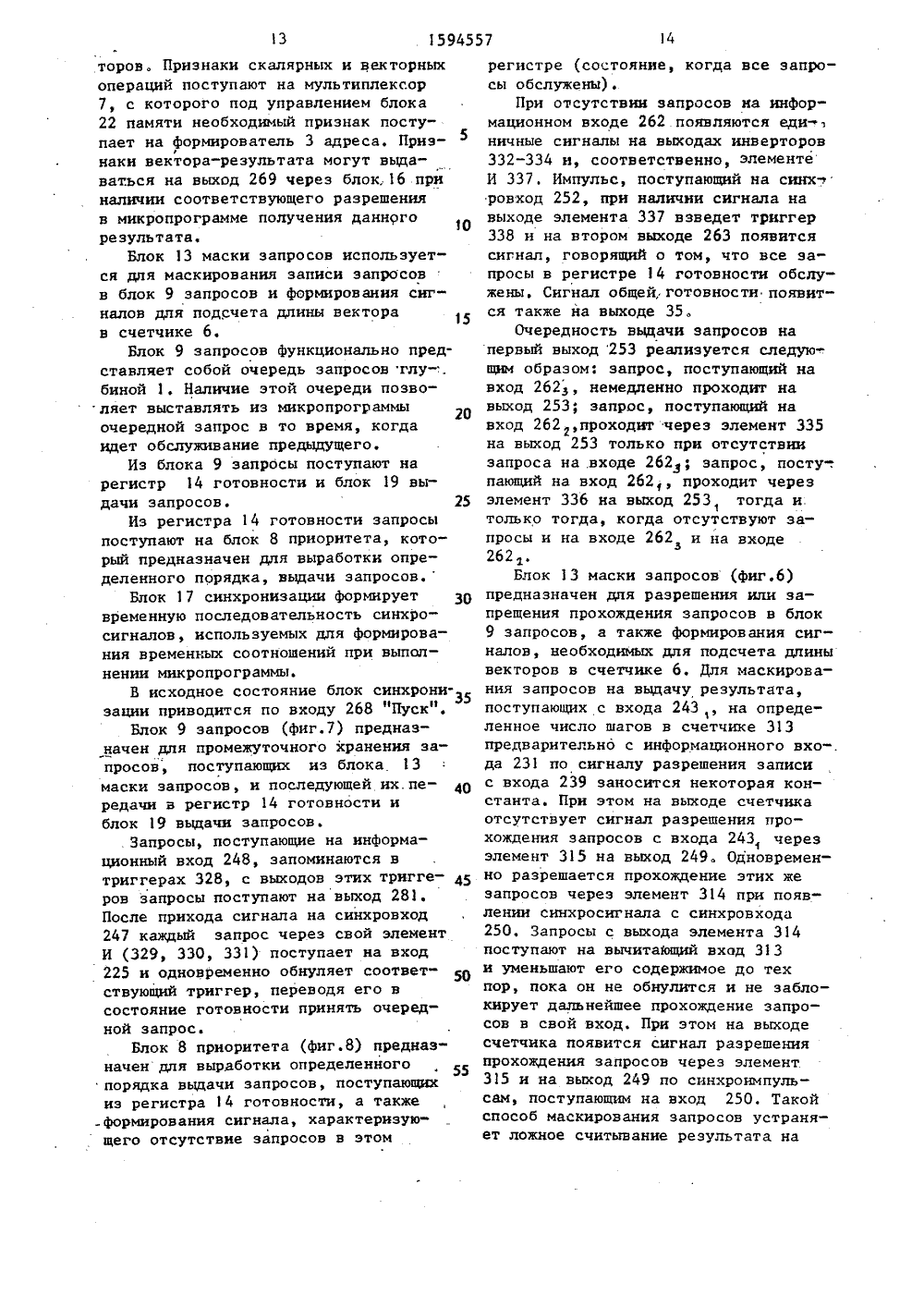

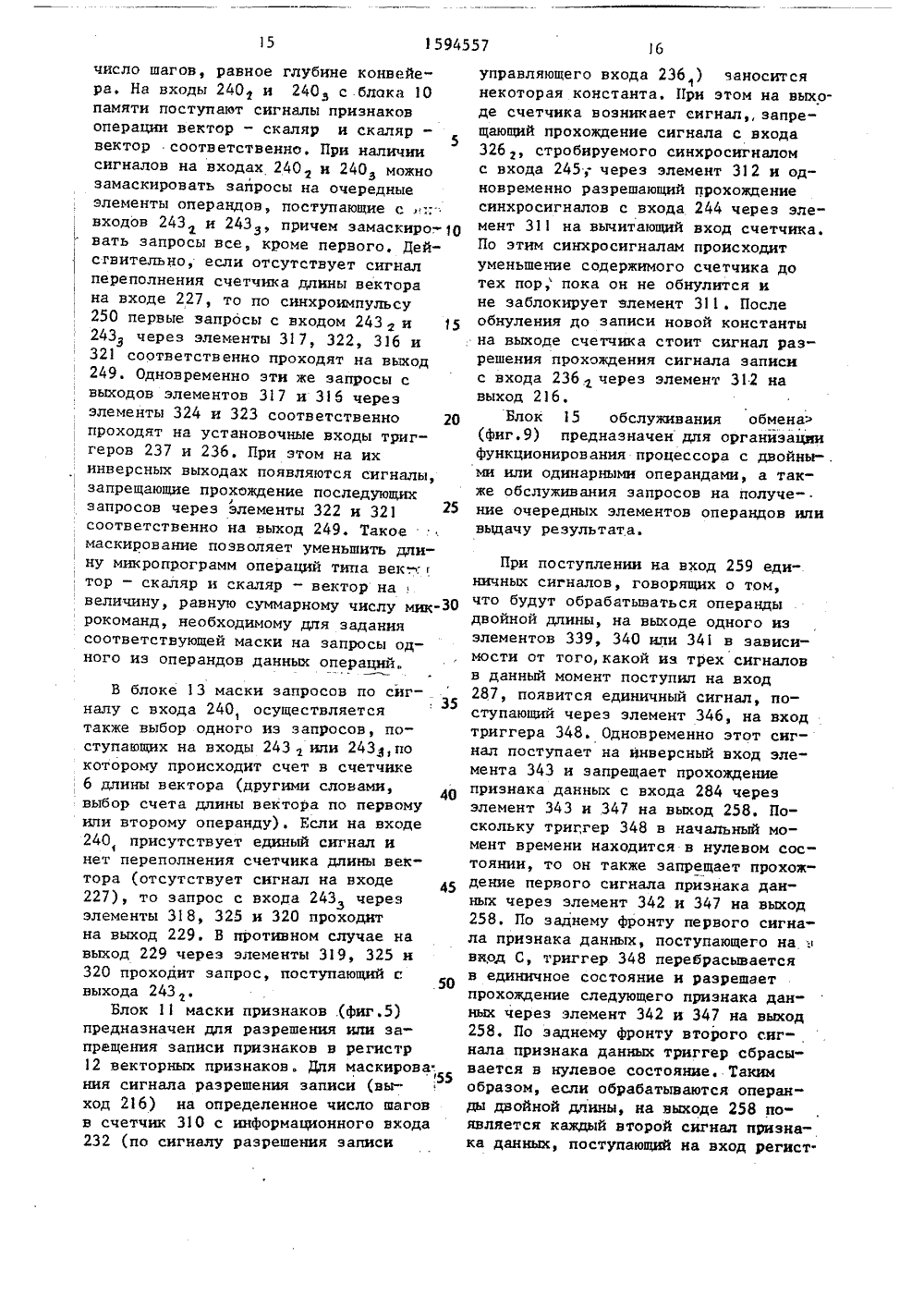

(191 51)5 С 06 Р 15/ ПИОАНИЕ ИЗОБРЕТ ТЕЛЬСТВ ВТОРСНОМ(21) (22) (46) (71) 72 равлена,о,ов,ертов сисорные ср с.3-5,ства гическ о-логидвигатеети к в ычис ыть исорной об ицинской араметКЛЮЧАЮтовформающипера1 еи,стройя управлеими объеком. Цельоизводиства,соотве1 О ип. к памяти микровующими связями ф-лы,табл хема фор а; на фиг мирователя па .3 - структу онизации; на ема блока выд елькой техн сд ожет быть использокторной обработкицинской и визуальАРМ и САПР, длятехнологическими ная сх ике и рой вмед и для ожными ма блока синхр структурная схпросов; на фиг ма блока маски иг.4 - чи заано для бы еофизическ ой ияформа правления- структ иэнаков; рная схена фиг,б ски запроя схема структурна фиг,9- служивания Упр ма труктурная схов; на фиг.7лока запросовая схема блоктруктурная сх бъектами и научным Цель изобретенияводительности. На фиг.1 предстасхема процессора; н периментом.овьппение произка м структурнна фиг.8приоритета блока о ена структурнаяфиг.2 - структур ОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМРИ ГКНТ СССР 4308823 30814.07,823.09.90. Бюл. Р 35Институт проблем уп(57) Изобретение относится лительной технике и может польэовано для быстрой век работки геофизической, мед и визуальной информации дл ния сложными технологическ тами и научным эксперимент изобретения - повышение пр бретение относится к вычислительности. Процессор содержит устроиство микропрограммного управления,содержащее блоки памяти, формирова-.тель адреса, регистр микрокоманд,регистр состояния, счетчик длинывектора, мультиплексор, блок приоритета, блок запросов, блок памятимикрокоманд перекодировки блок маски признаков, регистр векторных признаков, блок маски запросов, регистрготовности, блок обслуживания обмена., блок формирования векторных признаков. Кроме того, процессор содержитблок синхронизации, регистр кода операции, блок выдачи запросов, арифметико-логическое устройство мантисс,умножитель, арифметико-л устройство порядков, ари ческое устройство корре ли, коммутатор, формировате а сдвига, группу элемеЩЕЕ ИЛИ, блоки обмена и верхоперативные запоминства 20 поступают на вход 194 в регистр состояния.Четвертый этап представляет собой операцию поиска левой единицы (нуля) мантиссы результата. Полученный код параметра нормализации мантиссы и он же код параметра коррекции порядка результата с выхода четвертого сдвигателя 27 поступает в выбранный регистр блока 31-2 по входам- выходам 125.Пятый этап - это этап нормализациимантиссы результатаи коррекции порядка. Мантисса результата с выбранного регистра блока 31-1 по входам- выходам 127 поступает в третий сдвига- тель 26 по входам-выходам 126, который в зависимости от значения признака переполнения мантиссы результата микропрограммно настраивается на направление сдвига. Параметр сдвига поступает в третий сдвигатель 26 нашину 122 с входов-выходов 125 блока 31-2 ина шину 184 с регистра признаков25 значения признака переполнения. Резулв тат сдвига с временной задержкой поступает с входов-выходов 126 блока 26 нормализации на входы-выходы 127 блока 31-1. Одновременно с этим выполни ется коррекция порядка результата. При этом код порядка читается с выбранного. регистра блока 31-2 на входы- выходы 111 и далее принимается арифметико-логическим устройством 23 коррек 5 ции по входамгвыхадам 112, а код параметра коррекции читается с другого выбранного регистра блока 31-2 ло входам-выходам 125 на входы-выходы 124арифметика-логического устройства 23 40 коррекции. В зависимости от значения признака переполнения мантиссы арифметико-логическое устройство 23 коррекции микропрограммно.настраивается либо на операцию сложения, либо на 45операцию вычитания, Результат обработки читается по входам .выходам 112 на выбранный регистр блока 31-2 по входам-выходам 111На этом же этапе может быть осу ществлена коррекция порядка результата в зависимости от значения признаков Мс, ПРП 0 (см. табл.1).Шестой этап состоит в пересылкерезультата обработки с выбранных ре гнстров блоков 31 -1 и 31 -2 соответственно для мантиссы и порядка в выбранный регистр блоков 31-3, 31 -5 либо 31-4, 31 -6. 2 ОПри необходимости может быть реализован седьмой этап, когда результат обработки читается на шину данных.Конвейерный режим, сложения чисел с плавающей запятой поясняется табл.2, в которой развернутый цикл обработки одной пары чисел сжат в несколько этапов, в которых осуществляется обработка других пар чисел.Так, на первом этапе или в первой микрокоманде выполняются пересылка числа А из блоков 32-1 и 32-3 в блоки 31-3 и 31 -5, операция сдвига (выравнивание порядка) и операция нормализации. Вторая микрокоманда включает операцию пересылки числа В из блоков 32-2 и 32-4 в блоки 31 -4 и 31-6, операцию суммирования мантисс и пересылку результата обработки с блоков 31 -1 и 31-2 соответственно в блоки 31-3 (31 -4) и 31-5 (31-6). Третья микрокоманда состоит из операций сравнения порядков, поиска левой единицы (нуля) и чтения на шину данных. Таким образом, в каждой микрокоманде одновременно обрабатываются три пары чисел, т.е. глубина конвейера для данной операции равна трем.Умножение, Операция умножения начинается так же, как и сложение, за-, сылкой;поочередно операндов А и В соответствейно в блоки 31 -3, 31 -5 и 31-4,31-6. Далее мантиссы чисел читаются по входам-выходам 88 и 92 блоков 31 -3 н 31 -4 на входы.-выходы 90 и 93 умножителя 21, а порядки - по входам-выходам 105 и 110 блоков 31-5 и 31-6 на входы-выходы 16 и 09 ариф. метико-логического устройства 22 по- - . рядков. Осуществляется операция умно. жения мантисс в умножителе 21 и обработка порядков в арифметико-ло- . гическом устройстве 22.Результат умножения на следующем этапе записывается в блок 31-1 по входам-выходам 87, признаки, сформированные при умножении, записываются в регистр состояния, а результат обработки порядков " в блок 31-2,Следующий этап - операция поиска левой единицы (нуля) с записью кода параметра коррекции в блок 31-2 по входам-выходам 125. Для исходных нормализованных чисел код параметра коррекции равен 1. Следующие этапы такие же, как и для операции сложения чисел с плавающей запятой: нормализация, пересылка и чтение на шинуданных. При этом входы-выходы и функциональные блоки, задействованные на этих этапах, аналогичны и при сложении вВ табл.З показана свертка цикла5 микропрограммы умножения для конвейерной реализации.Реализация других операций ипи микропрограмм основывается на этих двух микропрограммах.Формула изобретения1.Иикропрограммируемый векторный процессор, содержащий устройство микропрограммного управления, арифметико-логическое устройство мантисс, арифметико-логическое устройство коррекции, умножитель, коммутатор, ариф О метико-логическое устройство порядков, первый, второй и третий сдвига- тели, блок синхронизации и регистр кода операций, причем вход кода операций процессора подключен к информа ционному входу регистра кода операций, выход которого соединен с вхо" дом кода команды устройства микропрограммного управления, первая группа разрядов входа логических условий О которого подключена к соответствующим разрядам выхода кода признаков результата арифметико-логнческого устройства мантисс, выход состояний логических условий устройства микропрограммного управления соединен с адресным входом коммутатора, с первого по шестой выходы блока синхронизации - соответственно с первого по шестой входами синхронизации устройства ми О кропрограммного управления, вход запуска процессора подключен к входу запуска блока синхронизации, седьмой выход которого соединен с входами записи арифметико-логических устройств 45 мантисс, коррекции и порядков, с входами записи с первого по третий сдвигателей входами чтения арифметико-логических устройств мантисс, коррекции и порядков и с восьмым выходом блока синхронизации, вход начальной установки устройства микропрограммного управления подключен к входам начальной установки регистра кода операций и процессора. Входы . 55 кода операции и входы управления третьим состоянием арифметико-логических устройств мантисс и порядков, входы управления треть м состоякием с первого по третий сдвигателейи коммутатора соединены соответственно с первого по восьмой выходами кодамикроопераций первой группы устройства микропрограммного управления, первый и второй выходы кода микроопераций второй группы которого подключены к входам настройки арифметико-логических устройств соответственномантисс и порядков, вход управлениятретьим состоянием и вход кода операции арифметико-логического устройства коррекции соединены соответственно с девятым выходом кода микроопераций первой группы и с вторым выходомсостояний логических условий устройства микропрограммного управления,вторая и третья группы разрядовпервого входа логических условийкоторого подключены к выходам кодапризнаков результата арифметико-логических устройств соответственнокоррекции и порядков, вход типа.сдвига третьего сдвигателя соединен стретьим выходом состояний логическихусловий устройства микропрограммногоуправления, выход признака отсутствия запросов которого подключен квходу управления режимом блока синхронизации, о т л и ч а ю щ и й с ятем, что, с целью повышения производительности, он дополнительно содержит с первого по десятый блоки обмена информацией, с первого по четвертый сверхоперативные запоминающиеустройства, четвертый сдвнгатель,блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь параметра сдвига, блокпамяти микроопераций и блок выдачизапросов, причем первый вход блокаэлементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединенс четвертым выходом состояний логических условий устройства микропрограммного управления, Выход запросовкоторого соединен с информационным .входом блока выдачи запросов, синхровход которого соединен с вторым выходом блока синхронизации, вход разрешения выдачи и выход запросов. блокавыдачи запросов подключены соответственно к выходу признака отсутствиязапросов устройства микропрограммного управления и к выходу запросов процессора, входы адреса с первого по шестой блоков обмена информацией соединены соответственно сдесятого по пятнадцатый выходами кода мнкроопераций первой группы устройства микропрограммного управлеНия, с шестнадцатого по двадцатьпервый выходы кода микрооперацийпервой группы которого соединены свходами управления третьим состоянием соответственно с первого по шестой блоков обмена информацией, первые информационные входы и выходыПервого и третьего блоков обмена информацией подключены к информационному входу"выходу арифметико-логиЧеского устройства мантисс и входупервого операнда умножителя; выходрезультата которого соединен с вторым 15информационным входом-выходом перЙого блока обмена информацией, третий информационный вход-выход которого соединен с информационным входом-выходом третьего сдвигателя ивторым входом блока элементов ИСКЛ 10 Ча 10 ЩЕЕ ИЛИ, выход которого соединенс информационным входом-выходом четвертого сдвигателя, вход управлениятретьим состоянием, вход записи и 25цход чтения которогоподключены соотВетственно к двадцать второму выходуйода микроопераций первой группыустройства микропрограммного управления и к седьмому и восьмому выхо. ЗОДам блока синхронизации, девятыйВыход которого соединен с первымиВходами чтения с первого по шестойблоков обмена информацией, входы записи первого и второго блоков обменаинформацией соединены с десятым выходом блока синхронизации, одиннадцатый выход которого соединен с вторыми входами чтения первого и второгоблоков обмена информацией, четвертыйинформационный вход-выход первого блока обмена информацией подключен квторому информационному входу-выходутретьего и к первому информационномуВходу-выходу четвертого блоков обмена информацией, инФормационный входарифметико-логического устройства мантисс соединен с входом второго операнда умножителя и подключен к второму информационному входу-выходу четвертого блока обмена информацией, третий и четвертый информационные входывыходы которого соединены соответст.венно с информационным, входом-выхо.-.дом второго сдвигателя и первым ин"Формационным входом-выходом восьмогоблока обмена информацией, второй информационный вход-выход которого соединен с первым информационным входом-выходом седьмого блока. обменаинформацией и подключен к входу задания кода длины вектора устройствамикропрограммного управления, двадцать третий выход кода микрооперациипервой группы которого соединен спервыми входами записи с третьего пошестой блоков обмена информацией,вторые входы записи которых подключены к двенадцатому выходу блока синхронизащи и первому входу разрешенияблока памяти мнкроопераций, входычтения третьего, пятого и шестого блоков обмена информацией подключены кдвадцать четвертому выходу кода микроопераций первой группы устройствамикропрограммного управления первыйвыход синхронизации запросов которого соединен с входами записи с седьмого по десятый блоков обмена информацией, входы чтения которых и четвертого блока обмена информацией соединены с вторым выходом синхронизациизапросов устройства микропрограммногоуправления, двадцать пятый выход кодамикроопераций первой группы которогоподключен к входу типа сдвига формирователя параметра сдвига, выход типасдвига которого подключен к входамтипа сдвига первого, второго и четвертого сдвигателей, выход параметрасдвига четвертого сдвигателя подключен к входу параметра сдвига третьего сдвигателя, информационному входуарифметико-логического, устройства коррекции и к первому информационномувходу-выходу второго блока обменаинформацией, второй информационныйвход-выход которого подключен кинформационному входу-выходу арифметико-логического устройства коррекциии к выходу коммутатора, третий информационный вход-выход второго сдвигателя подключен к первым информационнымвходам-выходам пятого и шестого блоков обмена информацией, четвертыйинформационный вход-выход второгоблока обмена информацией подключенк информационному входу формирователя параметра сдвига, второму информационному входу-выходу пятого блокаобмена информацией и к информационному входу-выходу арифметико-логического устройства порядков, информационный вход и выход кода признаковрезультата которого соединены соответственно с вторым информационнымвходом-выходом шестого блока. обмена59455 7обмена которого и десятого блока обмена информацией соединены с восемнадцатым выходом кода микроопераций первой группы устройства микропрограммного управления, пятый выход кода микроопераций первой группы которого соединен с вторыми входами разрешения обмена седьмого и восьмого блоков обмена информацией, первые входы записи которых и девятого и десятого блоков обмена информацией подключены к третьему выходу блока памяти микроопераций, четвертый выход которого соединен с первыми входами чтения с седьмого по десятый блоков об-. мена информацией, первые входы режима обмена которых соединены с пятым выходом блока памяти микроопераций, шестой выход которого соединен с вторыми входами записи с седьмого по десятый блоков обмена информацией, вторые входы чтения которых сое динены с седвмым выходом блока памяти микроопераций, восьмой выход которого соединен с третьими входами записи с седьмого по десятый блоков обмена информацией, третьи входы чтения которых соединены с девятым выходом блока памяти микроопераций, второй вход разрешения и адресный вход которого соединены соответственно с восьмым выходом блока синхронизации и двадцать седьмым вьмодом кода микроопераций первой группы устройства микропрограммного управления, девятнадцатый выход кода микро- операций первой группы которого соединен с вторыми входами .разрешения обмена девятого и десятого блоков обмена информацией, второй информационный вход-.выход десятого блока обмена информацией соединен синформационным входом-выходом четвертого сверхоперативного запоминающего устройства и с третьим информационным входом .выходом шестого блока обмена информацией, двадцать восьмой выход кода мнкроопераций первой группы устройства микропрограммного управления подключен к третьим информационным входам-выходам с седьмого по десятый блоков обмена информацией, четвертые информационные входы-выходы которых подключены к информационному входу- выходу процессора, вход признака наличия данных которого подключен к входу признака данных устройства микропрограммного управления, третий вы1594557 28 Т а б л и ц а 1 И О ПРПО Пу 0 кс Пмин+О + Т а блица 2 НормализацияПересылкаЧтение Запись А Выравнив аниепорядковСложениемантиссПоиск левойединицы Запись В Сравнениепорядков Таблица 3 Запись резуль- . ПересыпкататаПоиск левой ЧтениеединицыНормализация Запись А Запись В Умножение Ход синхронизации запросов которого соединен с вторым входом режима обмеНа седьмого и восьмого блоков обмена Информацией, вторые входы режима обмена девятого и десятого блоков обме 5 На информацией соединены с четвертым Выходом синхронизации запросов устройства микропрограммного управления, рервый и второй информационные входы коммутатора подключены к первому и второму входам константы процессора. 2.Процессор по п,1, о т л и " ч а ю щ и й с я тем, что,формирователь параметра сдвига содержит блок памяти, регистр и арифметико-логичессий блок, причем информационный вход Формирователя соединен с младшими разрядами одноименного входа регистра, первый выход которого соединен со старшими разрядами адресного входа блока памяти, младшие разрядыадресного. входа которого соединеныс входом типа сдвига формирователя,вход признака параметра сдвига которого соединен со старшим.:.разрядоминформационного входа регистра, первый выход кода микроопераций блокапамяти соединен с выходом типа сдвига формирователя, выход параметрасдвига которого соединен с выходомрезультата арифметико-логическогоблока, вход кода операции которогосоединен с вторым выходом кода микроопераций блока памяти, второй выход регистра соединен с входом первого операнда арифметико-логического блока, вход второго операнда которого соединен с шиной логическогонуля процессора.557 3 1594 обмена; на фнг.10 - временные диаграммы работы устройства.Процессор содержит (фиг.1) устрой. ствомикропрограммного управления, содержащее блоки 2 и 2 памяти1 й9 формирователь 3 адреса, регистр 4 микрокоманд, регистр 5 состояния, счетчик 6 длины вектора, мультиплек-,. сор 7, блок 8 приоритета, блок 9 запросов, блок 10 памяти микрокоманд перекодировки, блок 1 маски признаков, регистр 12 векторных признаков, блок 1 3 маски запросов, регистр 14 готовности, блок 15 обслуживания обмена, блок,16 формирования векторных признаков, а также процессор содержит блок 17 синхронизации, регистр 1 В кода операции, блок 19 выдачи запросов, арнфметико-логическое устройство 20 20 мантисс, умножитель 21, арифметикологическое устройство 22 порядков,1 арифметнко-логическое устройство 23 коррекции, с первого по четвертый сдвнгатели 24-27, коммутатор 28 фор мнрователь 29 параметра сдвига,.группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 30, с первого по десятый блоки 31-32 обмена информацией, с первого по четверчый сверхоперативные запоминающие30 устройства 33, блок 34 памяти микро- операций, выход 35 общей готовности, вход 36 общей готовности, входы 37 и 38 кода операций, выходы 39 и 40 кода операции. мантисс и порядков; с первого по шестой выходы 41 -46 кода адреса операндов; - входы 47"52 кода адреса, с первого по четырнадцатый выходы 53-66 управления конвейером, входы 67-80 управления третьюч состоянием, выход 81 кодов операций сдвига,40 первые входы-вькоды 82-85, выход 86 результата, второй вход-выход 7, третий вход-выход 88, вход первого операнда - выход 89 результата вхор45 90 первого. операнда, первый вход-выход 91, третий вход-выход 92, вход 93 второго операнда, вход 94 второго операнда, четвертый входвыход 95, четвертые входы-выходы 96 и 97, вторые входы-выходы 98 и 99, информацион 50 ные входы-выходы 100,и 101, второй вход-выход 102, вторые входы-выходы 103 и 104, третий вход-выход 105, . вход 106 второго операнда, первый вход-выход 107, информационный вход 108, вход первого операнда - выход 109 результата, третий вход-выход 110, третий вход-выход 111, вход первого операнда - выход 112 резулвтата,выход 113, вход 114 типа сдвига, вьгход 115 типа сдвига, выход16 параметра сдвига, входы 117 и 118 параметра сдвига, входы19 и 20 шипасдвига, вход 121 типа сдвига, вход122 параметра сдвига, выход 123 параметра сдвига, вход 124 третьегооперанда, четвертый вход-.выход 125,информационный вход-вькод 126, третий вход-выход 127, вторые входы 128элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы29 информационный вход-выход 1.30,с первого по одиннадцатый выходы 131141, входы 142-147 чтения, входы148-153 записи, входы 154-159 чтения,входы 160-170 записи, входы 1.71-77чтения, выход 178 кода признаковрезультата, вход 179 признака пара-.метра сдвига, четвертый информационный вход 80, первый выход 181, управ-.ляющий вход 182,второй выход 183,вход184 типасдвига, третий выход 185,первыевходы 186 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,четвертый выход 87, вход. 188 кодаоперации, выход 189 кода признаковрезультата, третий информационныйвход 190, выход 191 кода признаковрезультата;- второй информационныйвход 192, выход 193 кода признака результата, первый информационный вход194, выходы 195, информационный вход196, информационный вькод 197, информационный выход 198, адресныйвход 1 99, выход 200 мультиплексора,управляющие входы 201 и 202, выходы203 кода управления формирователемадреса, выход 204 кода микрокоманды,информационный вход 205, синхровходг20 б,выход 207, адресный вход 208,вход209 кодаоперации,информационный вход210, информационный выход 211, адресныйвход 212,адресный выход 213,адресныйРвход 24, группу выходов 215 кодамикроопераций, вькод 216, вход 217разрешения записи, группу информацион-,ных выходов 28, первый 219 и второй220 информационные входы, информацион-,ный выход 221, выход 222 кода управления мультиплексором, управляющийвход 223, выход 224, информационныйвход 225, выход 226 переполнениясчетчика, первый вход 227 первойгруппы управляющих входов, первыйвход 228, первый выход 229, счетныйвход 230, информационные входы 231 и232, третий информационный выход 233,выходы 234, выход 235 кода управления1594557 Составитель Ю. ЛанцовТехред М,Дидык Корректор М.Шароши Редактор .С.Пекарь Заказ 2831 Тираж 576 Под ВНИИПИ Государственного комитета по изобретени 113035, Москва, Ж, Раушскаятельский комбинат "Патент", г. Ужгород, ул. Гагарина, 10 изводственн ЯО 1 И ноеи открытиям при ГКНТ СССРб., д, 4/540 5 159455маской признаков, группу управляющихвходов 236, вход 237 разрешения запи-си, выход 238 кода управления маскойзапросов, второй вход 239 первойгруппы управляющих входов, вторуюгруппу управляющих входов 240, выход 241 кода маски, выходы 242 кода запросов, третью группу управляющих входов 243, первый 244 и второй245 синхровходы, вход 246 разрешения записи, синхровход 247, информационный вход 248, второй выход 249,синхровход 250, двенадцатый выход251, синхровход 252, первый выход253, управляющий вход 254, первуюгруппу выходов 255, асинхронные входы 25 б,установки в "1", вход 2 Ясинхронизации, выход 258 строба го. товности, управляющий вход 259, выход 260 признака двойных запросов,выход 261, информационный вход 262,второй выход 263, вход 264 разрешения выдачи, вход 265 кода длины. вектора, информационный вход 266, вход 25267 пуска устройства, вход 268 пуска, выход 269 кода признаков устройства, второй вход 270, третий вход271,четвертый вход 272, выход 273кода управления векторными признаками, пятый выход 274, первый 275 ивторой 276 информационные входы,.выход 277 кода настройки, вход 278,выход 279 кода настройки, вход 280,группу выходов 281, синхровход 282,вход 283 запросов, вход 284 признакасопровождения данных, выход 285 записи, выход 286 чтения, информационныйвход 287, синхронный вход 288 установки в "0", выход 289 запросов,Формирователь 29 параметра сдвигасодержит блок 290 памяти, регистр291 и арифметико-логический узел 292.Блок 17 синхронизации содержит генератор 293 импульсов, кольцевой45сдвигающий регистр 294, триггеры295-297, элементы НЕ 298 и 299 и элементы И 300-304.Блок 19 выдачи запросов содержитэлемент ИЛИ 305 и группу элементовИ 306-309, блок 11 маски признаковсодержит счетчик 30, элементы И 311и 312, блок 13 маски запросов содер-жит счетчик 313, группу элементовИ 314-324, элемент ИЛИ 325 и триггеры326 и 327.Блдк 9 запросов содержит регистр328 и группу элементов И 329-331,блок 8 приоритета содержит группу 7 6элементов НЕ 332-334, группу элементов И 335-337 и триггер 338, блок 15 обслуживания обмена содержит группу элементов И 339-345, элементы ИЛИ 346 347, триггер 348 и элемент И 349.Кроме того, процессор содержит пятнадцатый выход 350 управления кон вейером, выход 25 управления направлением обмена, седьмой выход 252 кода адреса, выход 353 чтения, выход 354 записи, выход 355 записи, выход 356 чтения, управляющий выход 357, выход 358 записи, выход 359 чтения, выход 360 записи, выход 361 чтения, первый 362 и второй 363 управляющие выходы, первые информационные входы-выходы 364-367, вторые информационные входы-выходы 368-371, третьй информационные входы-выходы 372 и 373, четвертые информационные входы- выходы 374 и 375, шестнадцатый выход 376 управления конвейером, пятые информационные входы-выходы 377-380, информационные входы-выходы 381-384, первый вход 385, второй вход 386, г третий вход 387, входы 388-391 чтения входы 392-399 записи, входы 400-403 чтения, управляющие входы 404-407, входы 408-411 записи, входы 412-415 чтения, входы 416-419 записи, входы 420-423 чтения, первые 424 и 425 и вторые 426 и 427 управляющие входы, входы 428-431 записи, входы 432-435 чтения, входы 436-439 кода адреса, входы 440-451,разрешения обмена и выход 452 кода констант.Формирователь 29.параметра сдвига содержит (фнг.2) блок 290 памяти, регистр 291 и арифметика-логический блок 292.Блок 1 7 синхронизации содержит (фиг,З) генератор 293 импульсов, кольцевой сдвигающий регистр 294, триггеры 295-297, инверторы 298-299, с первого по пятый элементы И 300-.304.Блок синхронизации предназначен для выработки сигналов чтения, записи информации в различные блоки устройства, для формирования определенной временной последовательности сннхроимпульсов,. необходимых для организации правильной работы векторного нроцесса.При поступлении сигнала "Пуск" на вход 268 блока синхронизации генератор 293 начинает формировать тактовые импульсы, поступающие на входкольцевого сдвигающего регистра 294, На выходе этого регистра поочередно возникают сигналы, которые вместе с КЗ-триггерами и логическими элементамй, указанными на фнг.3, обеспечивают формирование сигналов в соответствии с временной диаграммой, приведенной на фиг 10, Сигналы на выходах131-135 блока синхронизации возникают 10 , только тогда, когда присутствует сиг- . нал разрешения на управляющем входе , 254.Блок 19 выдачи запросов содержит(фиг.4) многовходовой элемент ИЛИ 305 15и группу элементов И 306-309.Блок 19 выдачи запросов предназначен дпя формирования в определенные моменты времени запросов на получение очередных элементов вектора 20 ипи выдачу результата.При поступлении хотя бы одногоиз запросов на вход элемента ИЛИ 305 на его выходе возникаетсигнал, который при наличии сигнала 25разрешения на входе 264 и строба насннхровходе 282 проходит через эле мент И 306 на вход группы элементов И 307-309 и разрешает прохождениезапросов с входа 283 через соответствующие элементы И на выход 289.Четырехканальные блоки 31-1 в 31 -2 обмена информацией выполняют функции промежуточных регистров общегоназначения, блоки 31-3 и 31-4 служат для приема чисел с фиксированной запятой либо мантисс чисел с плавающей запятой, Четырехканальные блоки 31 -5 н31-6 обмена информацией служат дляприема порядков чисел с плавающей 4запятой, Блоки 32-132-4 предназначены для обмена информацией с шинойданных. Каждый из блоков 31, 32 содержит четыре внутренних регистраСдвигатели 24-26 предназначены для 45приема и сдвига данных с последующейих выдачей, Сдвиги могут быть вправои влево, арифметические и логические,с сохранением выпадающих при сдвигеразрядов и их сборкой по ИЛИ с последующим сдвигом информации. Параметрсдвига и его тип задаются: формирова.телем 29 сдвига по шинам 115 и 116. Умножитель 21 предназначен дляумножения чисел с фиксированяой за 55пятой.Арифметико-логическое устройство22 порядков предназначено дпя обработкн (сложения, вычитания) порядков чисел.Арифметико-логическое устройство 23 коррекции служит для коррекции порядка результата на этапе нормализации.Регистр 5 состояния предназначен для приема, хранения и выдачи признаков, получаемых в процессе вычисления.Сдвигатель 27 совместно с группой элементов ИСКЛИЧАМЩЕЕ ИЛИ 30 выполняет функцию поиска левой еднннцы (нуля), начиная со старшего разряда мантиссы. Группа элементов 30 состоит из элементов суммы пс шой 2, на один из входов которых поступает соответствующий разряд мантиссы, а на другой вход - знак мантиссы. В зависимости от знака иантиссы блок 30 либо передает разряды мантиссы беэ изменения, либо с инверсией, Сдвигатель 27 формирует код параметра сдвига мантиссы для операции нормализации.Арнфметико-логическое устройство 20 предназначено для обработки данных при арифметических и логических операциях. Арифметико-логическое устройство 20 служит для обработки мантисс либо чисел с фиксированной запятой,Коммутатор 28 предназначен для формирования максимального либо минимального порядка результата в зависимости от значения признаков, Такая зависимость показана в табл.1, где М = 0 - значение мантиссы результата; П - максимальный порядок; Пф мксминимальный порядок; ПРП ) 0 - приз: нак переполнения порядков больше О. Формирователь 29 параметра сдвига (фиг,2) предназначен для выработки кода параметра сдвига и типа сдвига. На вход 108 формирователя поступает код разности порядков из блока 22, который записывается в регистр 291. Сюда же по входу 179 из блока 22 поступает знак разности порядков. Код разности порядков вместе со знаком поступает на вход старших разрядов адреса блока 290 памяти, Одновременно четыре младших разряда кода разности поступают на вход первого операнда арифметнко-логического устройства 292, На вход младших разрядов адреса блока 290 памяти по входу 114 из микропрограммы поступает код типа сдвига. На основе поступивших данных этот блок вырабатываетна первом выходе код, который поступает на выход 115 типа сдвига, а на втором выходе вырабатывает код операции, поступающий в арифметикологическое устройство 292. На вход5 второго операнда арифметико-логического устройства 292 поступает код логического нуля, в зависимости от кода операции арифметико-логического уст-. ройства на выходе 116 вырабатывается код параметра сдвига.Все блоки, входящие в устройство, кроме блока 17 синхронизации, блока 13 маски запросов, блока 11 маски признаков, блока 15 обслуживания обмена, блока 19 выдачи запросов, блока 8 приоритета, блока 9 запросов и формирователя 29 параметров сдвига, являются стандартными, известными в технике схемными решениями и поэтому их структурные схемы в описании устройства не приведены.Например, блок 31-3 обмена информацией реализуется на БИС - схема 25 обмена информацией КР 1802 ВВ 1.Первые сдвигатели 24 и 27 реализуются на БИС - арифметический расширитель: КР 1802 ВР 1.Арифметико-логическое устройство. 30 20 мантисс реализуется на БИС - микропроцессорная секция КР 1802 ВС 1.Формирователь 3 адреса реализуется на БИС - схема управления последовательностью микрокоманд К 1804 ВУ 4.Коммутатор 28 реализуется на ИС К 155 КП- дешифратор - коммутатор.Блоки 2,-и 2 памяти реализуются на ИС КР 556 РТ 5. 40Шина данных является двунаправленной шиной, по которой передаются исходные числа либо с фиксированной, либо с плавающей запятой и результаты обработки. 45Блок 16 формирования векторных признаков представляет собой блок памяти, Входы 270, 272 и 228 и старшие разряды входа 271 являются адресными входами блока памяти, Младшие раз ряды входа 271 являются входами разрешения чтения блока памяти, выход 224 и выход 269 кода признаков являет. ся первым и вторым информационными выходами блока памяти. Блок 19 на ,каждом такте . работы устройства иэ скалярных признаков, т.е. признаков результатов обработки компонент векторов, поступающих на его вход 270,и признака переполнения счетчика 6,поступающего по входу 228, предыдущих(т.е. полученных на предыдущем тактеработы устройства) векторных признаков, поступаюших по входу 272, в зависимости от разрешения иэ микропрограммы формирует векторные признаки,необходимые для внутренней работыустройства (выход 224) и внешнейработы (выход 269),Блок 13 маски запросов содержит(фиг.6) счетчик 313, группу элементов И 314-324, элемент ИЛИ 325, первый 326 и второй 327 триггеры, первую группу управляющих входов 227,вторую группу управляющих входов 240,третью группу управляющих входов243, информационный вход 231, синхровход 250, первый 229 и второй 249выходы. Блок 10 запросов содержит(фиг.7) регистр 328 и группу элементов И 329-331, группу информац;юонныхвходов 248, синхровход 247, первуюгруппу выходов 255, вторую группу выходов 281.Блок 8 приоритета содержит (фиг.8)группу элементов ИЛИ 332-334, группуэлементов И 335-.337, триггер 338,группу информационных входов 262, синхровход 252, первый выход 253, второйвыход 263 и выход 35 общей готовности.Блок 15 обслуживания обмена содержит (фиг,9) группу элементов И 339345 и 349, первый 346 и второй 347элементы ИЛИ, триггер 348, управляющий вход 259, информационный вход287, вход 284 признака данных, вход36 общей готовности, выход 258 стробаготовности данных, выход 285 записи,выход 286 чтения, первый 362 и второй363 управляющие выходы. Микропрограмма предлагаемого устройства представляет собой микропрограмму конвейерной обработки данных, обеспечивающую выполнение арифметикологической операции, заданной в команде (например, умножение двух чисел с плавающей точкой, поразрядное логическое умножение двух кодов).Микропрограмма конвейерной обработки данных - это такая микропрограмма, которая позволяет вести параллельную обработку сразу нескольких пар элементов операндов-массивов (либо нескольких элементов одного операнда- массива для унарных команд), причем каждая иэ.пар элементов находитсяв определенной фазе выполнения арифметико-логнческой операции.Например, известно, что операциясложения двух чисел с плавающей точкой состоит из следующих фаз; анализпорядков, выравнивание порядков,сложение и нормализация. Микропрограмма данной операции позволяет одновременно нормализовать сумму х-й парычисел, суммировать +1-ю паручисел,выравнивать порядки у 1+2-й пары чисел (например, 1, 1.+1, +2, 1+3индексы четырех, расположенных подряд, элементов векторов-операндов).Для организации конвейерного процессаобработки, векторов-операндов в устройстве используются,мнкрооперацнизапроса данных или запроса двойныхданных. Они предназначены для пересылки элемента массива операнда наОЗУ либо для пересылки элементамассива результата выполнения векторной операции в,ОЗУ.При выполнении определенного запро-.25са соответствующий триггер регистра14 готовности устанавливается всостояние "Готов". Запрос считаетсявыполненным, если запрашиваемая пересылка выполнена (соответствующий 30триггер регистра готовности сбрасывается).Благодаря использованию в устройстве механизмов блокировки и выдачизапросов, а также двойных запросов,блокировки формирования векторныхпризнаков и блокировки всех запросов,кроме первого, с помощью кода настройки из блока 10 памяти возможно блокирование выдачи ложных результатов и 40признаков результата .с конвейера дотого момента, пока на входы операционных блоковвходящих в последнюю ступень конвейера для данной операции,не придут результаты обработки первой пары операндов массива данных навсех предшествующих ступенях конвейера, С выдачей последней пары операндов массива данных запросы на новыеоперанды также блокируются. Возможна также аппаратная блокировка всех .запросов, кроме первого, на выдачуодного из операндов при выполненииопераций типа вектор - скаляр, например умножения компонент вектора наконстанту, что приводит к сокращениюмикрот рограмм выполнения таких операций, а следовательно, к сокращениюобъема ПЗУ и всего оборудования в це" лом н повышения быстродействия устройства. Устройство работает следующимобразом,По входу 268 "Пуск" происходитустановка устройства в исходное состояние, подготовка схем к работе(цепи сброса регистров и счетчиковустройства в исходное состояние непоказаны). По входу 265 в счетчикдлины вектора иэ блоков 32-1 и 32-2обмена заносится длина вектора, Кодоперации поступает на вход 209 устройства и затем в регистр 18 кодаоперации векторной команды.В блоке 10 памяти микрокоманд перекодировки происходит перекодирование кода операции в начальный адрессоответствующей микропрограммы, в коднастройки операционной части, поступающий на выход 215 и позволяющийреализовать выполнение микропрограммв конвейерном режиме для данногокода операции, аппаратно модифициро. -вать операции, выполняемые отдельнымиустройствами (например, изменить типданных и формат данных в операционных блоках, блокировать выдачу запросов, настроить блок 13 на обработкудвойных запросов),Формирователь 3 служит для формирования адреса каждой последующей микрокоманды, выполняемой микропрограммы в соответствии с временной диаграммой. По сформированному адресу,поступающему на блок 2 памяти микропрограмм, выбирается соответствующаямикрокоманда, поступающая на регистр4 микрокоманд для хранения в периодвыполнения микрокоманды.Блок 22 памяти расшифровывает кодмикрокоманды и выдает на выход 195кода мнкроопераций и блоки устройства управляющие сигналы. Посколькувыполнение микропрограммы происходитв конвейерном режиме, возникает необходимость,маскирования записи признаков в регистр 12 векторных признаков.Для этого служит блок 11 маскцрованияпризнаков, Кроме векторных признаков,поступающих на информационный вход225, на регистр 12 по этому же входупоступает признак последнего операнда.По информационным входам 180,190, 192 и 194 на регистр 5 состояния поступают признаки, возникающиепри выпопнении скалярных операций,т.е. операций над компонентами век"торов. Признаки скалярных и векторныхопераций поступают на мультиплексор7, с которого под управлением блока22 памяти необходимый признак поступает на формирователь 3 адреса, ПриэРнаки вектора-результата могут вьдаваться на выход 269 через блок. 16 приналичии соответствующего разрешенияв микропрограмме получения данногорезультата.Блок 13 маски запросов используется для маскирования записи запросовв блок 9 запросов и формирования сигналов для подсчета длины вектора15в счетчике 6.Блок 9 запросов функционально представляет собой очередь запросов глу-биной 1. Наличие этой очереди позво.ляет выставлять из микропрограммыочередной запрос в то время, когдаидет обслуживание предыдущего,Из блока 9 запросы поступают нарегистр 14 готовности и блок 19 выдачи запросов, 25Из регистра 14 готовности запросыпоступают на блок 8 приоритета, который предназначен для выработки определенного порядка, выдачи запросов.Блок 17 синхронизации формируетвременную последовательность синхросигналов, используемых для формирования временкых соотношений при выполнении микропрограммы.В исходное состояние блок синхронизации приводится по входу 268 "Пуск".Блок 9 запросов (фиг.7) предназначен для промежуточного хранения запросов, поступающих из блока 13маски запросов, и последующей их.передачи в регистр 14 готовности иблок 19 вьдачи запросов.. Запросы, поступающие на информационный вход 248, запоминаются втриггерах 328, с выходов этих триггеров запросы поступают на выход 281,После прихода сигнала на синхровход247 каждый запрос через свой элементИ (329, 330, 331) поступает на вход225 и одновременно обнуляет соответствующий триггер, переводя его всостояние готовности принять очередной запрос.Блок 8 приоритета (фиг.8) предназначен для выработки определенногопорядка вьдачи запросов, поступающихиз регистра 14 готовности, а такжеформирования сигнала, характеризующего отсутствие запросов в этом регистре (состояние, когда все запросы обслужены).При отсутствии запросов на информационном входе 262 появляются еди ничные сигналы на выходах инверторов 332-334 и, соответственно, элементе И 337. Импульс, поступающий на синх-. ровход 252, при наличии сигнала на выходе элемента 337 взведет триггер 338 и на втором выходе 263 появится сигнал, говорящий о том, что все запросы в регистре 14 готовности обслужены. Сигнал общей,. готовности появится также на выходе 35.Очередность выдачи запросов на первый выход 253 реализуется следуют щим образом: запрос, поступающий на вход 262 З, немедленно проходит на выход 253; запрос, поступающий на вход 262,проходит через элемент 335 на выход 253 только при отсутствии запроса на входе 262, запрос, посту-. пающий на вход 262 , проходит через элемент 336 на выход 253, тогда и только тогда, когда отсутствуют запросы н на входе 262 и на входе 262 .Блок 13 маски запросов (фиг.6) предназначен для разрешения ипи запрещения прохождения запросов в блок 9 запросов, а также формирования сигналов, необходимых для подсчета длины векторов в счетчике 6. Для маскирования запросов на выдачу результата, поступающих с входа 243 на определенное число шагов в счетчике 313 предварительно с информационного вхо-. да 231 по сигналу разрешения записи с входа 239 заносится некоторая константа. При этом на выходе счетчика отсутствует сигнал разрешения прохождения запросов с входа 243 через элемент 315 на выход 249. Одновременно разрешается прохождение этих же запросов через элемент 314 при появлении синхросигнала с синхровхода 250, Запросы с выхода элемента 314 поступают на вычитающий вход 31 3 и уменьшают его содержимое до тех пор, пока он не обнулится и не заблокирует дальнейшее прохождение запросов в свой вход. При этом на выходе счетчика появится сигнал разрешения прохождения запросов через элемент.315 и на выход 249 по синхроимпульсам, поступающим на вход 250. Такой способ маскирования запросов устраняет ложное считывание результата начисло шагов, равное глубине конвейера, На входы 240 и 240 з с блака 1 О памяти поступают сигналы признаков операции вектор - скаляр и скаляр - вектор соответственно. При наличии5 сигналов на входах 240 и 240 з можно замаскировать запросы на очередные элементы операндов, поступающие с- входов 243 и 243 з, причем замаскиро-. 10 вать запросы все, кроме первого. Дейсгвительно, если отсутствует сигнал переполнения счетчика длины вектора на входе 227, то по синхроимпульсу 250 первые запросы с входом 243и 15 243 з через элементы 31 7, 322, 316 и 321 соответственно проходят на выход 249. Одновременно эти же запросы с выходов элементов 317 и 316 через элементы 324 и 323 соответственно 20 проходят на установочные входы триггеров 237 и 236. При этом на их инверсных выходах появляются сигналы, запрещающие прохождение последующих запросов через элементы 322 и 321 соответственно на выход 249, Такое маскирование позволяет уменьшить длину микропрограмм операций типа векс тор - скаляр и скаляр - вектор на величину, равную суммарному числу микрокоманд, необходимому для задания соответствующей маски на запросы одного из операндов данных операцийВ блоке 13 маски запросов по сигналу с входа 240, осуществляется также выбор одного из запросов, поступающих на входы 243или 243,по которому происходит счет в счетчике 6 длины вектора (другими словами, выбор счета длины вектора по первому или второму операнду). Если на входе 240, присутствует единый сигнал и нет переполнения счетчика длины вектора (отсутствует сигнал на входе 227), то запрос с входа 243 з через элементы 31 8, 325 и 320 проходит на выход 229. В противном случае на выход 229 через элементы 319, 325 и 320 проходит запрос, поступающий с выхода 243Блок 11 маски признаков .(фиг.5) предназначен для разрешения или запрещения записи признаков в регистр 12 векторных признаков. Дпя маскирова".55 ния сигнала разрешения записи (выход 216) на определенное число шагов в счетчик 310 с информационного входа 232 (по сигналу разрешения записи управляющего входа 2361) заносится некоторая константа. При этом на выходе счетчика возникает сигнал запрещающий прохождение сигнала с входа 326 , стробируемого синхросигналом с входа 245; через элемент 312 и одновременно разрешающий прохождение синхросигналов с входа 244 через элемент 311 на вычитающий вход счетчика. По этим синхросигналам происходит уменьшение содержимого счетчика до тех пор, пока он не обнулится и не заблокирует элемент 311 . После обнуления до записи новой константы на выходе счетчика стоит сигнал разрешения прохождения сигнала записи с входа 236, через элемент 312 на выход 216.Блок 15 обслуживания обмена (фиг.9) предназначен для органиэации функционирования процессора с двойны- . ми или одинарными операндами, а также обслуживания запросов на получе-. ние очередных элементов операндов или выдачу результата. При поступлении на вход 259 еди" ничных сигналов, говорящих о том, что будут обрабатываться операнды двойной длины, на выходе одного из элементов 339, 340 или 34 в зависимости от того, какой из трех сигналов в данный момент поступил на вход 287, появится единичный сигнал, поступающий через элемент 346, на вход триггера 348. Одновременно этот сигнал поступает на инверсный вход элемента 343 и запрещает прохождение признака данных с входа 284 через элемент 343 и 347 на выход 258. Поскольку триггер 348 в начальный момент времени находится в нулевом состоянии, то он также запрещает прохождение первого сигнала признака данных через элемент 342 и 347 на выход 258. По заднему фронту первого сигнала признака данных, поступающего на : вкод С, триггер 348 перебрасывается в единичное состояние и разрешает прохождение следующего признака данных через элемент 342 и 347 на выход 258, По заднему фронту второго сигнала признака данных триггер сбрасывается в нулевое состояние. Таким образом, если обрабатываются операнды двойной длины, на выходе 258 появляется каждый второй сигнал признака данных, поступающий на вход регист.1594557 45 50 55 17ра готовности. Если же для какого-либо сигнала запроса отсутствует ссответствующий сигнал признака операндадвойной длины (цепь 259), то на выходе элемента 346 будет,присутство-.:5вать нулевой сигнал, разрешающийпрохождение первого сигнала признакаданных с входа 284 через элементы343 и 347 на выход 258.Блок 15 обеспечивает также формирование сигналов чтения (выдачи) результата или записи (приема) операндов. Если на вход элемента 341 пошине 287 поступает единичный сигнал,соответствующий запросу на выдачурезультата, то на выходе элемента344 по сигналу признака данных с входа 284 возникает сигнал чтения, по ступающий на выход 286. Если же навходе элемента 241 отсутствуетединичный сигнал, то по сигналампризнака данных на выходе элемента345 возникают сигналы записи соответствующего операнда, поступающие 25на вход 285, Кроме того, по сигналам,формируемым на выходах 362 и 363,обеспечивается одновременная записьинформации во все блоки 32 обменас шины данных либо раздельная запись 30сначала в блоки 32-1 и 32-2, а затемв 32-3 и 32-4. Это позволяет обрабатывать слова двойного формата,Таким образом, благодаря блоку 15обслуживания обмена обеспечиваетсяуправление операндами и результатомкак одинарной, так и двойной длины,а также обеспечивается возможностьработы устройства с магистралью обмена данными для многопроцессорных 40устройств и уменьшение разрядностикода признаков управления запросами.Рассмотрим работу на примерах сложения и умножения чисел с плавающейзапятой, поскольку они являются ос-.новными для остальных операций. Сложение, По шине данных в блоки 32 обмена информацией записываются последовательно числа, подлежащие обработке. При этом иантиссы чисел поступают соответственно в блоки 32-1 и 32-2, а порядки - в блоки 32-3 и 32-4. По сигналам из микрокоманды данные последовательно переписываются в соответствующие блоки 31-3,.;,31 -6. Цикл операции сложения чисел с плавающей запятой состоит из нескольких этапов. На первом этапе выполняется обра-.ботка порядков, т.е. сравнение порядков. Порядки чисел с блоков 31-6 и31-5 по входам-выходам 105 и 11 О поступают на входы-выходы соответственно 106 и 109 арифметико-логическогоустройства 22 порядков, которое настраивается микропрограммно на операцию вычитания. Результат операциив виде разности исходньг порядковпоступает с входов-выходов 109 свременной задержкой на вход 108 формирователя 29 параметра сдвига, Взависимости от знака разности порядков включается в работу сдвигатель 24либо 25 и формируется код параметрасдвига вправо мантиссы числа с меньшим порядком,На втором этапе выполняетсясдвиг мантиссы числа с меньшим порядком вправо, т,е. операция выравнивания порядков. Направление сдвига задается микрокомандой. На этом же этапе осуществляется пересыпка наибольщего порядка в один из регистров блока 31-5. Пересыпка осуществляется через арифметико-логическоеустройство 22 порядков, которое настранваетая на передачу кода либо свходов-выходов 109, либо с входоввыходов 106. Если наибольший порядоксодержится в регистре блока 31-6,то он через арифметико-логическоеустройство 22 по входам-.выходам 105,109 и 110 поступает в заданный регистр блока 31-5. В случае наибольшего порядка в блоке 31-5 передачаего осуществляется по входам-.выходам 110, 109 и обратно 109, 110. 1Третий этап представляет собой сложение мантисс. Для этого мантиссы двух операндов читаются с блоков.31 - 3 и 31-4 по входам-выходам 88 и 92.на соответствующие входы-выходы 89 и 94 арифметико-логического устройства 20, которое микропрограммно настроено на операцию сложения. Результат операции с временной задержкой поступает по входам-выходам 89 на заданный регистр блока 31-1 по входам- выходам 91. Сдновременно с этим выб-: ранный наибольший порядок, хранящийся в блоке 31-5, читается с него по входам-выходам 110 на выбранный регистр блока 31-2 по входам-выходам 107, Сформированные признаки с выходов 193 арифметико-логического устрой

СмотретьЗаявка

4308823, 14.07.1987

ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ

ВЕЙЦ АЛЕКСАНДР ВЕНИАМИНОВИЧ, ДЯТЧИНА ИРИНА ФЕДОРОВНА, ЖУКОВ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ, КРИВОРУЧКО ВИТАЛИЙ ФЕДОРОВИЧ, МАЛЮГИН ВЛАДИМИР ДМИТРИЕВИЧ, СОКОЛОВ ВЛАДИМИР ВЛАДИМИРОВИЧ, СПЕРАНСКАЯ ИРИНА ВЛАДИМИРОВНА, ШЕВЦОВ СЕРГЕЙ ВАЛЕНТИНОВИЧ, ПРАНГИШВИЛИ ИВЕРИ ВАРЛАМОВИЧ, ЛЕВЕРТОВ ЯКОВ АНАТОЛЬЕВИЧ, ДЕНИСЕНКО СЕРГЕЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: векторный, микропрограммируемый, процессор

Опубликовано: 23.09.1990

Код ссылки

<a href="https://patents.su/20-1594557-mikroprogrammiruemyjj-vektornyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммируемый векторный процессор</a>

Предыдущий патент: Многоканальное устройство управления доступом к общей магистрали

Следующий патент: Устройство для исследования связности графа

Случайный патент: Кильблочная постель судоподъемного устройства