Счетный триггер с логическим счить1ванием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

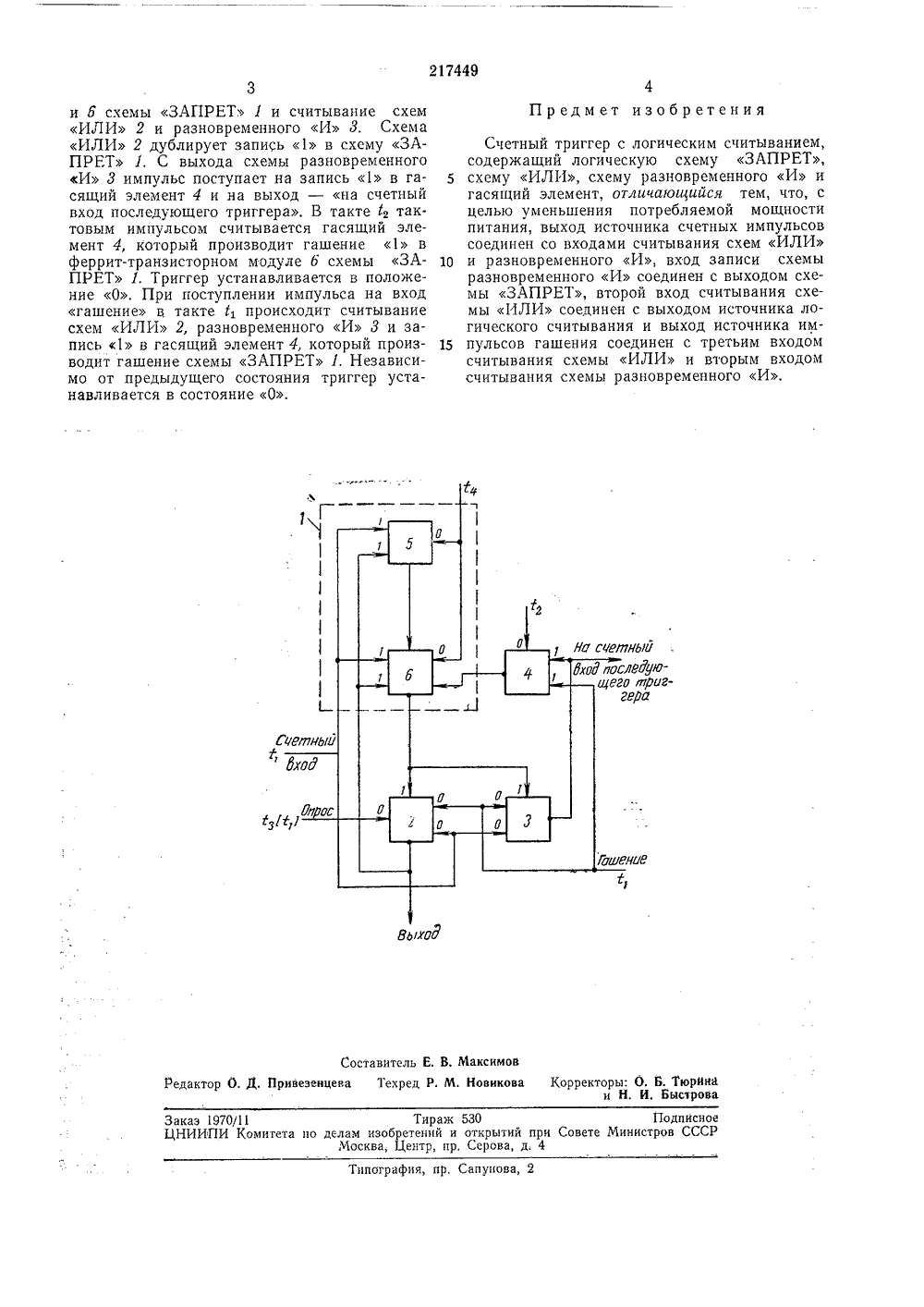

Саюа Соватскиа Социалистических Республик1Йаесо,оен-.:,д авт. свидетельстваависимоеаявлено 2 21 а 1, 36/18 062320/26-2 11.196 с присоединением заявкиМПК Н 031 с ПриоритетОпубликовано 07,7.1968, Бюллетень16Дата опубликования описания 19.И 1.1968 Комитет пс деламбретений и открытийи Совете 1 т 1 ипнстрсвСССР ДК 621.374.3(088,8) Авторыизобретения. С. Миронов и Э. А. Баканович аявитель Центральный научно-исследовательский и проектно-технологический институт организации и техники управления ЧЕТНЫЙ ТРИГГЕР С ЛОГИЧЕСКИМ СЧИТЫВАНИЕМ е пнчертеже изображена функциональная четного триггера с логическим считысхема сванием.Она содержит сИЛИ 2, схему рсящий элемент 4,из двух феррит-трпричем коллектортером модуля б.соединен со входа2 и разновременновыполненный на ф хему ЗЛГ 1 РЕТ 1,азновременного И 3Схема ЗАПРЕТ 1 санзисторных модулеймодуля 5 соединен сВыход схемы ЗЛПРми записи 1 схемго И 3. Счетный треррит-транзисторных схему и гаостоит 5 иб, эмит- ЕТ 1 ИЛИ иггер, модуИзвестен счетный триггер с логическим считыванием, содержащий логическую схему ЗАПРЕТ, схему ИЛИ, схему разновременного И и гасящий элемент,Предложенный триггер отличается от известных тем, что выход источника счетных импульсов соединен со входами считывания схем ИЛИ и разновременного И, вход записи схемы разновременного И соединен с выходом схемы ЗАПРЕТ, второй вход считывания схемы ИЛИ соединен с выходом источника логического считывания и выход источника импульсов гашения соединен с третьим входом считывания схемы ИЛИ и вторым входом считывания схемы разновременного И. Это позволяет уменьшить потребление мощности питания. лях, работает при четырехтактном цикл тания следующим образом.С приходом первого импульса на счетныйвход в такте 1, происходит запись 1 в мо 5 дули 5 и б схемы ЗАПРЕТ 1 и считываниесхем ИЛИ 2 и разновременного И 3. В такте 1 е тактовым импульсом считывается гасящий элемент 4, но так как в него не была записана 1, не происходит гашения схемы 10 ЗЛПРЕТ 1. В такте 1 (или 11) осуществляется считывание схемы ИЛИ 2 логическим сигналом опрос (при считывании в такте 1 а считывание триггера и поступление счетного импульса производятся в разных циклах), но 15 так как 1 не была записана в схему ИЛИ2, на выходе не будет импульса. В такте 14 тактовым импульсом считывается схема ЗАПРЕТ 1 и 1 записывается в схему ИЛИ 2 и разновременное И 3. Триггер устанав ливается в положение 1 и остается в такомсостоянии до прихода очередного сигнала опроса или прихода счетного импульса. При очередном считывании логическим сигналом опрос в такте 1 а (или 1,) кодовый импульс 25 1 регенерируетв замкнутой цепи, образованной схемами ЗАПРЕТ 1 и ИЛИ 2. и триггер снова устанавливается в положение 1. При этом на выходе появляется импульс, С приходом второго импульса на счет ный вход происходит запись 1 в модули 5217449 Предмет изобретения йЫлЕУуюи лОаггра Составитель Е. В. Максимов едактор О, Д. Привезенцева Техред Р. М. Новикова Корректоры: О. Б. Тюрина и Н. И, Быстроваж 530 и открытий при Совете р, Серова, д. 4 каз 1970/11 Тир НИИПИ Комигета по делам изобретени Москва, Центр, Подписноестров СССР Типография, пр, Сапунова, 2 и Ю схемы ЗАГ 1 РЕТ 1 и считывание схем ИЛИ 2 и разновременного И 3. Схема ИЛИ 2 дублирует запись 1 в схему ЗАПРЕТ 1. С выхода схемы разновременного И 3 импульс поступает на запись 1 в гасящий элемент 4 и на выход - на счетный вход последующего триггера. В такте 1, тактовым импульсом считывается гасящий элемент 4, который производит гашение 1 в феррит-транзисторном модуле 6 схемы ЗАПРЕТ 1. Триггер устанавливается в положение 0. При поступлении импульса на вход гашение в такте 1, происходит считывание схем ИЛИ 2, разновременного И 3 и запись 1 в гасящий элемент 4, который производит гашение схемы ЗАПРЕТ 1, Независимо от предыдущего состояния триггер устанавливается в состояние 0. Счетный триггер с логическим считыванием,содержащий логическую схему ЗАПРЕТ, 5 схему ИЛИ, схему разновременного И игасящий элемент, отличающийся тем, что, с целью уменьшения потребляемой мощности питания, выход источника счетных импульсов соединен со входами считывания схем ИЛИ 10 и разновременного И, вход записи схемыразновременного И соединен с выходом схемы ЗАПРЕТ, второй вход считывания схемы ИЛИ соединен с выходом источника логического считывания и выход источника им пульсов гашения соединен с третьим входомсчитывания схемы ИЛИ и вторым входом считывания схемы разновременного И.

СмотретьЗаявка

1062320

Центральный научно исследовательский, проектно технологический, институт организации, техники управлени

В. С. Миронов, Э. А. Баканович

МПК / Метки

МПК: H03K 21/10

Метки: логическим, счетный, счить1ванием, триггер

Опубликовано: 01.01.1968

Код ссылки

<a href="https://patents.su/2-217449-schetnyjj-trigger-s-logicheskim-schit1vaniem.html" target="_blank" rel="follow" title="База патентов СССР">Счетный триггер с логическим счить1ванием</a>

Предыдущий патент: Устройство для передачи и приема сообщений использованием разностной фазово-импульсноймодуляции

Следующий патент: Универсальный логический элемент

Случайный патент: 411905