Интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

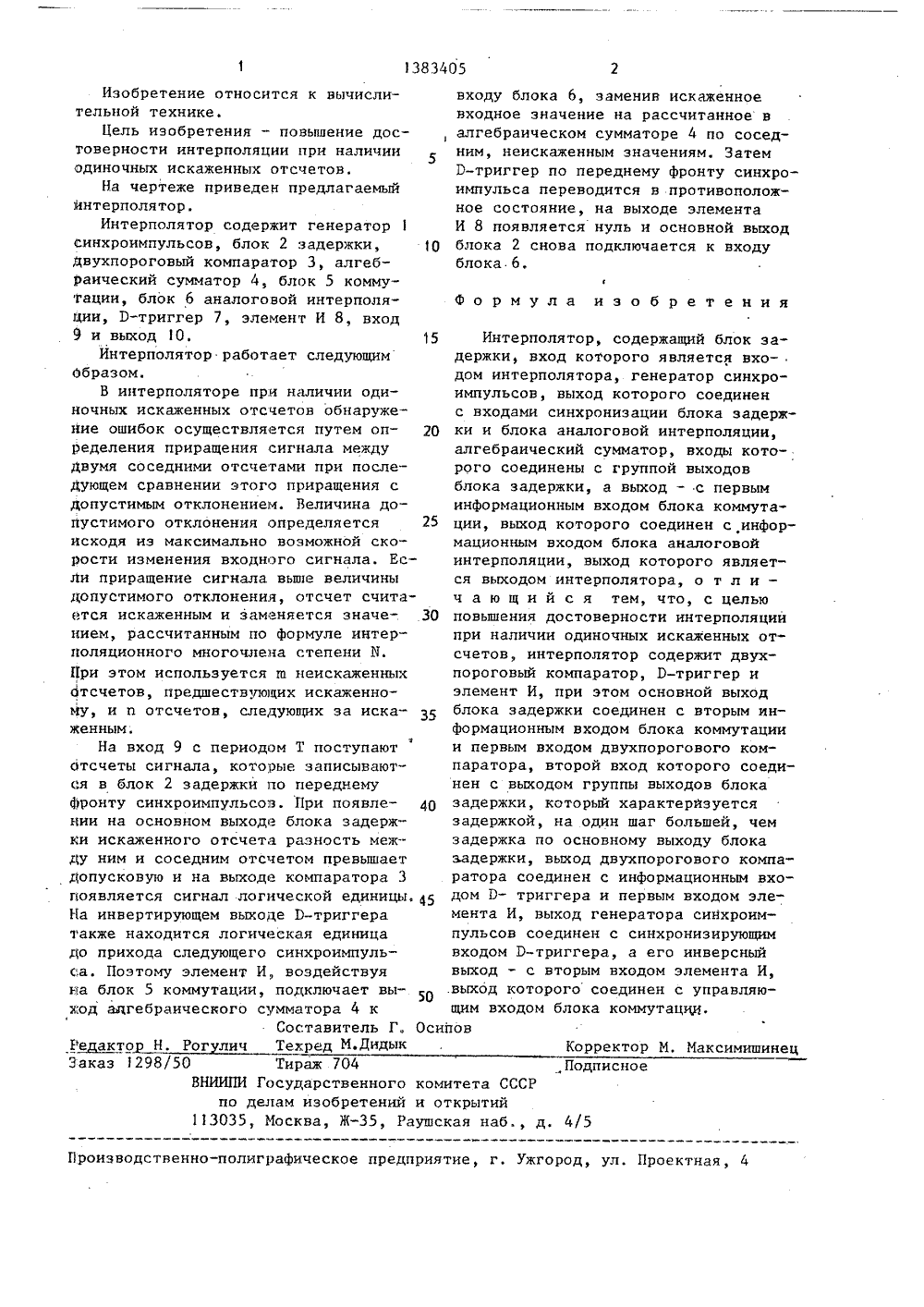

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИК А д 4 С 06 О 7/ УДАРСТВЕННЫЙ НОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ ИОТНРЫТИЙ ПИС ИЗОБРЕТЕ 1;с ЬСТВ О.А. Белоконь, Пленсак тельство ССС 7/30, 1980. льство СССР О 7/30, 1982 АВТОРСКОМУ СВ(57) Изобретение относится к вычислительной технике, Цель изобретения -повышение достоверности интерполяциипри наличии одиночных искаженных отсчетов. Интерполятор содержит генератор 1 синхроимпульсов, блок задержки 2, двухпороговый компаратор 3,алгебраический сумматор 4, блок 5коммутации, блок 6 аналоговой интерполяции, Р-триггер 7, элемент И 8,вход 9, выход 10. При появлении искаженного входного значения, отклонение которого от соседнего превышаетдопуск, установленный компаратором,оно заменяется усредненным значениемрассчитанным по соседним значениям.1 ил1 1383405 2 5 1 О Осипов Е я.Н,у, т,т И,а Заказ 1298/50 Тираж 704 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Корректор М. Максимишинец Подписное Изобретение относится к вычислительной технике.Цель изобретения - повышение достоверности интерполяции при наличииодиночных искаженных отсчетов.На чертеже приведен предлагаемыйинтерполятор,Интерполятор содержит генератор 1синхроимпульсов, блок 2 задержки,двухпороговый компаратор 3, алгебраический сумматор 4, блок 5 коммутации, блок 6 аналоговой интерполяции, Э-триггер 7, элемент И 8, вход9 и выход О,Йнтерполятор работает следующимОбразом.В интерполяторе при наличии одиночных искаженных отсчетов обнаружение ошибок осуществляется путем определения приращения сигнала междуДвумя соседними отсчетами при послеДующем сравнении этого приращения сДопустимым отклонением. Величина допустимого отклонения определяетсяисходя из максимально возможной скорости изменения входного сигнала. ЕсЛи приращение сигнала выше величиныдопустимого отклонения, отсчет считается искаженным и заменяется значением, рассчитанным по формуле интерполяционного многочлена степени И.Ири этом используется ш неискаженныхОтсчетов, предшествующих искаженноМу, и и отсчетов, следующих за искаженным.На вход 9 с периодом Т поступаютотсчеты сигнала, которые записываются в блок 2 задержки по переднемуФронту синхроимпульсов. При появлении на основном выходе блока задержки искаженного отсчета разность между ним и соседним отсчетом превышаетдопусковую и на выходе компаратора 3появляется сигнал логической единицы.На инвертирующем выходе В-триггератакже находится логическая единицадо прихода следующего синхроимпульса. Поэтому элемент И воздействуяна блок 5 коммутации, подключает выход ацгебраического сумматора 4 кСоставитель Г 15 20 25 30 35 40 5 50 входу блока 6, заменив искаженноевходное значение на рассчитанное валгебраическом сумматоре 4 по соседним, неискаженным значениям. ЗатемЭ-триггер по переднему фронту синхроимпульса переводится в противоположное состояние, на выходе элементаИ 8 появляется нуль и основной выходблока 2 снова подключается к входублока.б,Формула изобретения Интерполятор, содержащий блок задержки, вход которого является входом интерполятора, генератор синхроимпульсов, выход которого соединен с входами синхронизации блока задержки и блока аналоговой интерполяции, алгебраический сумматор, входы которого соединены с группой выходов блока задержки, а выход - с первым информационным входом блока коммутации, выход которого соединен с информационным входом блока аналоговой интерполяции, выход которого является выходом интерполятора, о т л и - ч а ю щ и й с я тем, что, с целью повышения достоверности интерполяции при наличии одиночных искаженных отсчетов, интерполятор содержит двух- пороговый компаратор, Э-триггер и элемент И, при этом основной выход блока задержки соединен с вторым информационным входом блока коммутации и первым входом двухпорогового компаратора, второй вход которого соединен с выходом группы выходов блока задержки, который характерйзуется задержкой, на один шаг большей, чем задержка по основному выходу блока задержки, выход двухпорогового компаратора соединен с информационным входом 0- триггера и первым входом элемента И, выход генератора синхроимпульсов соединен с синхронизирующим входом В-триггера, а его инверсный выход - с вторым входом элемента И, .выход которого соединен с управляющим входом блока коммутацид.

СмотретьЗаявка

4085744, 07.07.1986

СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО "МОДУЛЬ" ВИННИЦКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

МАРЦЕНЮК ВАЛЕРИЙ ПАНТЕЛЕЙМОНОВИЧ, БЕЛОКОНЬ ОЛЕГ АНАТОЛЬЕВИЧ, ПИЛИПЧАК ВАЛЕРИЙ ИВАНОВИЧ, ПЛЕНСАК ОЛЕГ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор

Опубликовано: 23.03.1988

Код ссылки

<a href="https://patents.su/2-1383405-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор</a>

Предыдущий патент: Логарифмический преобразователь

Следующий патент: Устройство для определения прогнозных оценок случайного процесса

Случайный патент: Устройство для резки бобин ленточного материала