Перестраиваемый микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 983713

Авторы: Благодарный, Плахтеев, Тимонькин, Ткаченко, Харченко

Текст

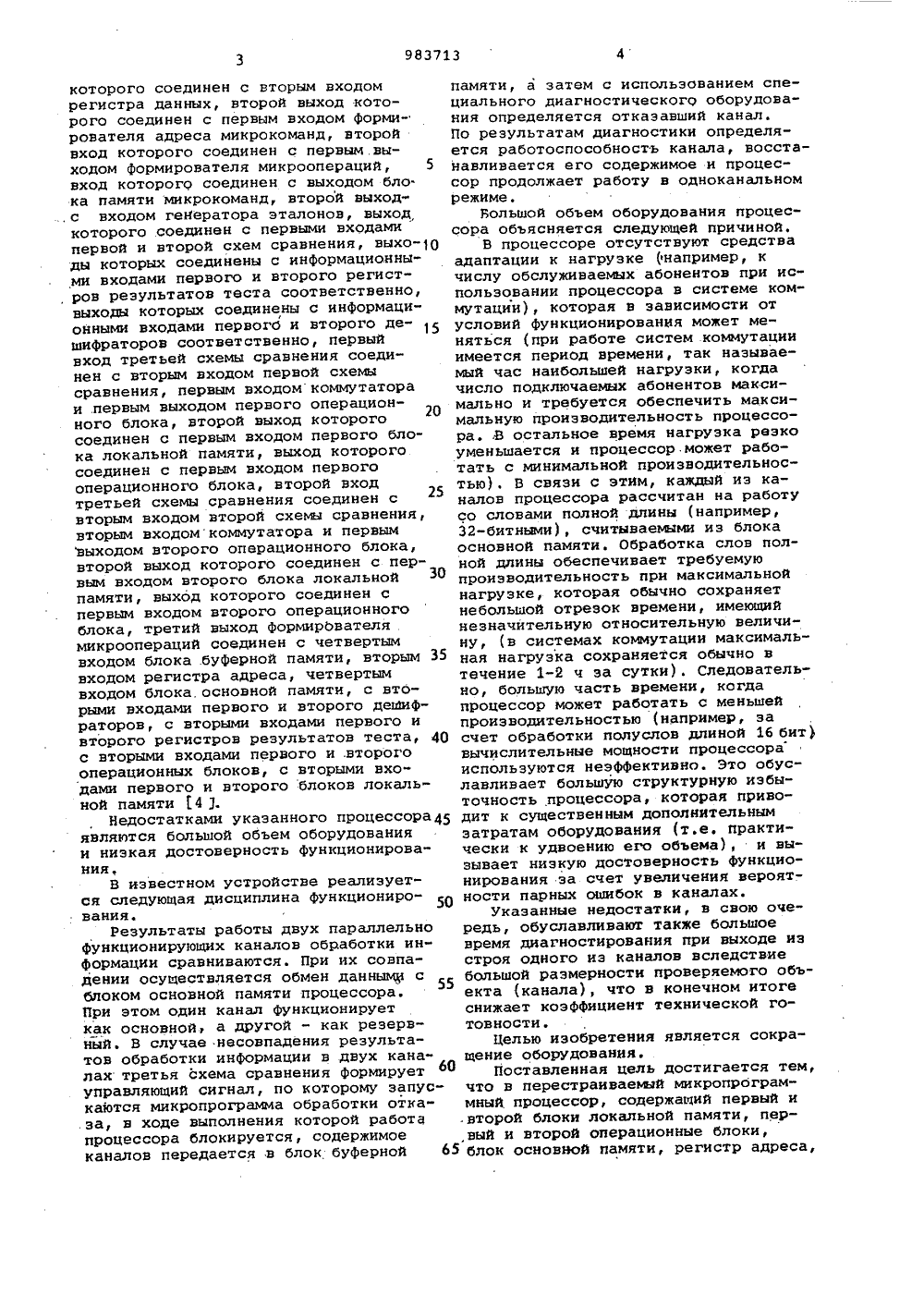

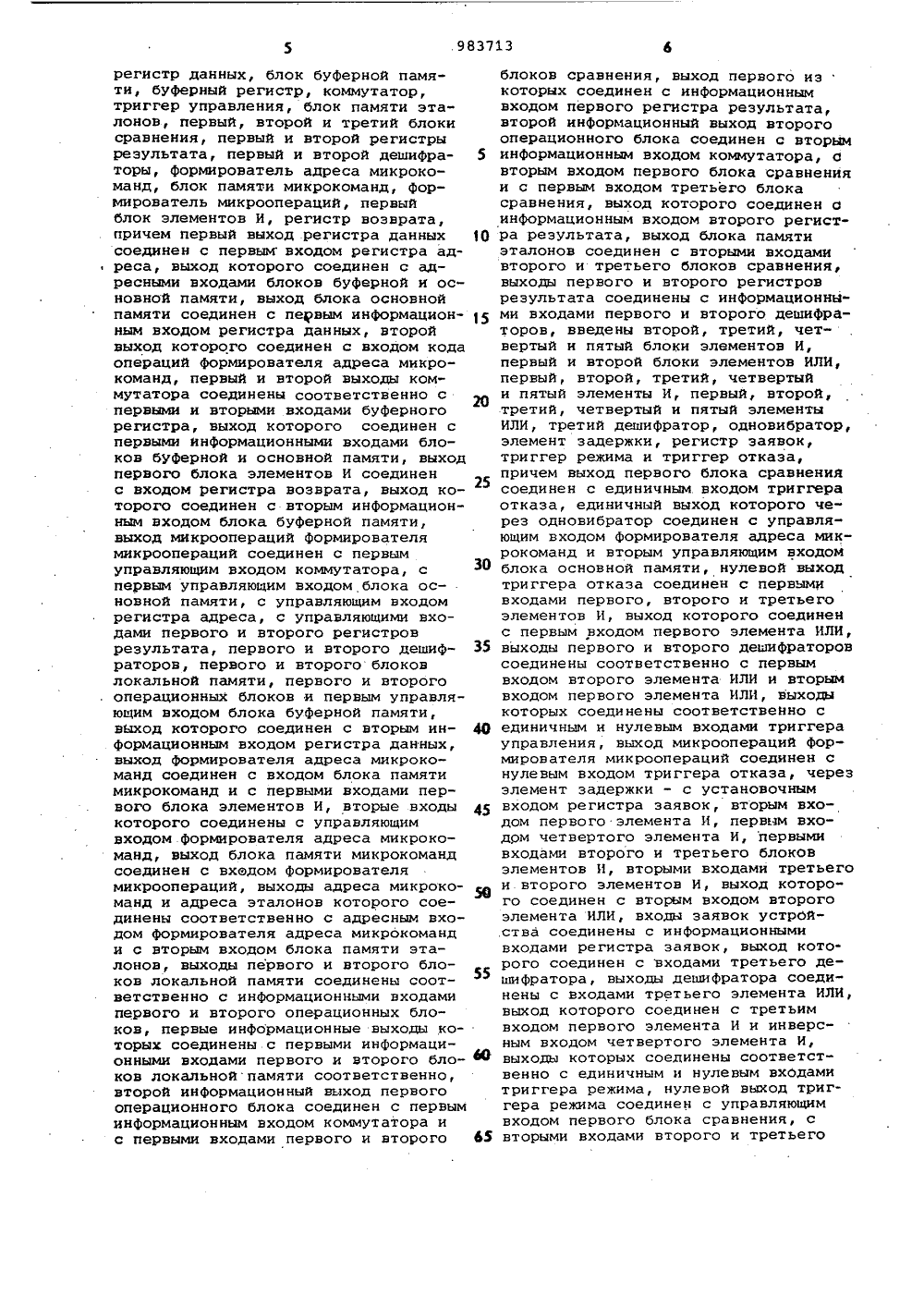

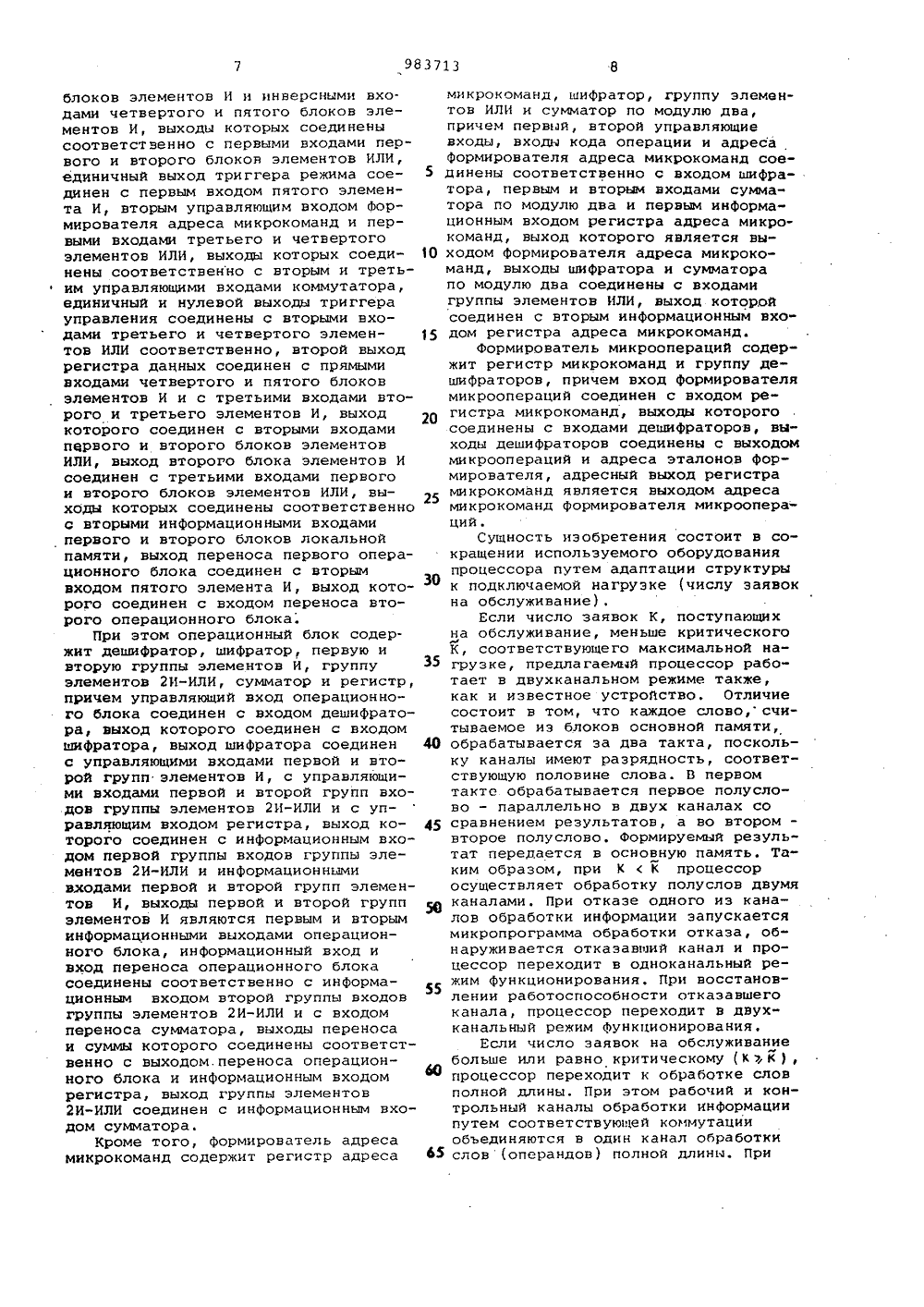

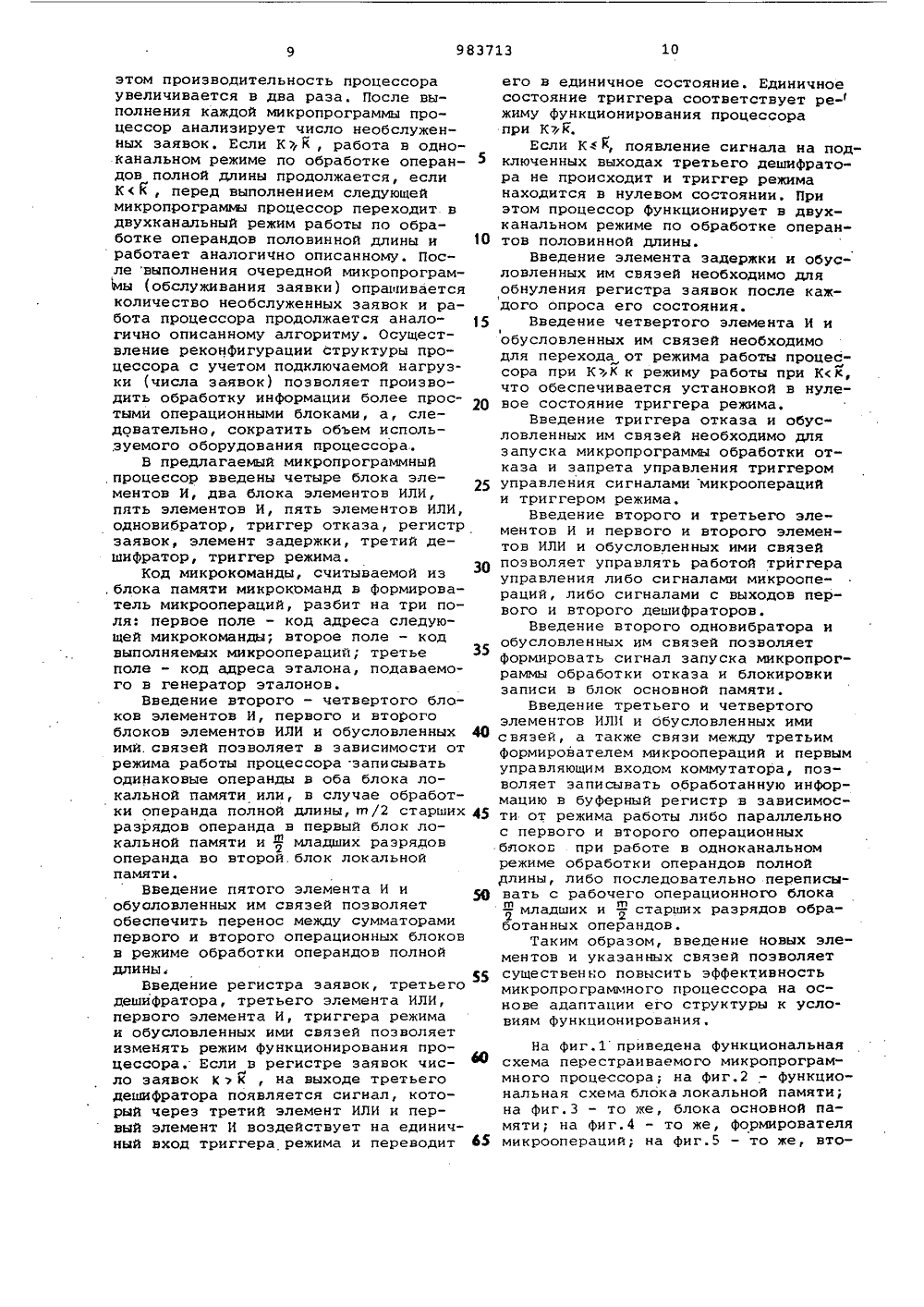

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоцивлистическикреспублик и 983713(22) Заявлено 12,05,81 (21) 3287646/18-24с присоединением заявки Ио -(088.8) Государственный комитет СССР по делам изобретений и открытий(54) ПЕРЕСТРАИВАЕИЫЙ МИКРОПРОГРАММНЫЙ ПРОЦЕССОР Изобретение относится к цифровой,, вычислительной технике и может быть использовано при проектировании быстродействующих адаптивных вычислительных систем с микропрограммным управлением.Известны микропрограммные процес соры с самодиагностикой, содержащие дублированные блоки обработки инфор. ,мации и локальной памяти, блок микропрограммного управления и блок основной памяти 1 3 - 1.3Недостатками известных процессоро 1 являются большой объем оборудования, связанный с необходимостью: дополнительного резервирования на уровне устройств для обеспечения их работо способности, при отказ ах, и. з начитель-, ные простои оборудования, связанные с тем, что процессоры рассчитаны на обработку информации в часы наибольшей нагрузки и малоэффективны (не нагружены обработкой инФормации) при функционировании в остальное время.Наиболее близким техническим решением к предлагаемому устройству является микропрограммный процессор содержащий первый и второй блоки локальной памяти, первый и второй операционные блоки, блок основной памяти, регистр данных, регистр адреса, блок буферной памяти, буферныйрегистр, коммутатор, триггер управления, генератор эталонов, первуютретью схеуи .сравнения, первый и второй регистры результатов теста, первый и второй дешифраторы, формирователь адреса микрокоманд, блок памяти 10 микрокоманд, Формирователь микроопераций, первый блок элементов И, регистр возврата, причем первый выходрегистра данных соединен с первымвходом регистра адреса, выход которого соединен с первым входом блокабуферной памяти и первым входом блока основной памяти, выход которогосоединен с первым входом регистраданных, второй вход - с выходом буФерного регистра, первый и второйвходы которого соединены с первым ивторым выходами коммутатора соответственно, и вторым входом блока буферной памяти, третий вход - с первымвходом первого блока элементов И,второй вход которого соединен с выхо.дом Формирователя адреса микрокоманди входом блока памяти микрокоманд,а выход - с входом регистра возврата, выход которого соединен с третьимвходом. блока буферной памяти, выходступает либо через первый (второй)вход второй группы элементов И группы81 элементов 2 И-ИЛИ на сумматор 82,либо через первую группу 84 элементов И на второй вхыод 87 операционных блоков, либо через вторую группу85 элементов И на первый выход 86опеРационных блоков 14.Назначение основных функциональных элементов блока буферной памяти(Фиг,6) состоит в следующем,Накопитель 94 предназначен дляхранения содержимого первого блока 5локальной памяти, первого операционного блока 12, второго, блока 6 локальной памяти, второго операционного блока 14 при выполнении микропрограммы обработки отказа,Первый регистр 107 предназначендля. хранения содержимого регистра 9адреса на время выполнения микропрограммы обработки отказа. Второй регистр 103 предназначен для сохраненияадреса микрокоманды, перед выполнением которой в процессоре был обнаружен отказ на время выполнения микропрограммы обработки отказа.Первый 97 и второй 99 элементы Ипредназначены для записи и считывания информации из накопителя 94.Первый 102 и третий 106 блоки элементов И предназначены для записи информации во второй 103 и первый 107регистры информации с первого 101 ивторого 105 входов блока 15 буферной,памяти,Второй блок 93 элементов И предназначен для управления записью информации с второго входа 90 блока 15буферной памяти на второй вход накопителя 94., Четвертый 108 и пятый 104блоки элементов И предназначены дляуправления выдачей информации с первого 107 и второго 103 регистров наблок 95 элементов ИЛИ по сигналаммикроопераций, поступающим на четвертый 92 вход блока 15 буферной памяти.Блок 95 элементов ИЛИ предназначендля выдачи информации на выход 96блока 15 буферной памяти с выходанакопителя 94 четвертого 108 и пятого104 блоков элементов И. Блок буферной памяти Функционирует следующим образом.1. Режим записи информации, Сигналами микроопераций, поступающими на четвертый вход 92 блока 15 буферной памяти, открывается по второму входу первый 102, второй 93 и третий 106 блоки элементов И и первый элемент И 97.Импульсы записи, поступающие через первый элемент И 97 на третий вход накопителя 94 по адресу, поступающему с первого входа 101 блока 15 буферной памяти на первый вход нако пителя 94, записывают в него информа,рого 103 регистров через открытые по второму входу четвертый 108, либо пятый 104 блоки элементов И и через блок 95 элементов ИЛИ поступает на выход 96 блока 15 буферной памяти.Назначение основных функциональных элементов генератора эталонов (фиг.7) состоит в следующем.Регистр 113 предназначен для хранения и выдачи на выход 114 эталонной комбинации для текущего такта выполнения микропрограммы диагностики и адреса следующей эталонной комбинации на второй вход группы элементов ИЛИ 110.Блок 112 памяти эталонных комбинаций предназначен для хранения эталонных комбинаций для микропрограммы диагностики. Дешифратор 111 - для формирования адреса очередной эталонной комбинации и считывания ее из блока 112 памяти эталонных комбинаций. 30 35 40 45 Блок 31 памяти эталонов функционирует следующим образом,Сигнал микроопераций, поступакщийна вход 109 блока 31 памяти эталонов,поступает через блок 110 элементовИЛИ на информационный и на управляющий входы дешифратора 111. По адресу, сформулированному дешифратором111, из блока 112 памяти эталонныхкомбинаций считывается в регистр 113очередная эталонная комбинация. Операционная часть эталонной комбинациипоступает с регистра 113 на выход 114генератора эталонов, а косвенный адрес следующей эталонной комбинациипоступает с второго выхода регистра113 на второй.вход группы элементов 5 10 15 20 25 5 Ф 55 Ы цию с выхода второго блока 93 элементов И.Информация, поступающая на первый вход 101 блока 15 буферной памяти через открытый по второму входу первый блок 102 элементов И, записывается во второй регистр 103. Информация, поступающая на второй вход 105 блока 15 буферной памяти, записывается в первый регистр 107.2. Режим считывания информации. Сигналы микроопераций, поступающие на четвертый вход блока 15 буферной памяти, открывают по второму входу либо второй элемент И 99, либо четвертый блок 108 элементов И, либо пятый блок И элемента 104. В первом случае импульсы считывания проходят через второй элемент И 99 на четвертый вход накопителя 94 по адресу, поступающему на его первый вход с первого входа 101 блока 15 буферной памяти, считывают информацию из накопителя 94 и через блок 95 элементовИЛИ передают ее на выход 96 блока 15 буферной памяти.Информация с первого 107 или вто 2221983713ИЛИ 110 и через него - на информационный вход дешифратора 111. По сигналу микрооперации, поступающему на управляющий вход дешифратора 111, он возбуждается и Формирует адрес следующей эталонной комбинации.НазнаЧение основных функциональных элементов Формирователя 39 адреса микрокоманд (фиг.8) состоит в следующем.ШиФратор 118 предназначен для формирования адреса первой микрокомандымикропрограммы обработки отказа. Блок 119 элементов ИЛИ - для выдачи старших разрядов адреса очередной микро- команды на регистр 120 с выхода сум 1 О 15 ля 41 микроопераций поступает сигнал, по которому формирователь адреса микрокоманд формирует адрес первой микрокоманды микропрограммы обработки отказа. Это осуществляется следующим образом.Сигнал с четвертого входа 122 заПускает шифратор 118, выходной сигнал которого, являющийся адресом первой микрокоманды микропрограммы обработки отказа, записывается через группу 119 элементов ИЛИ в регистр 120.Процессор работает следующим образом. Работа процессора в режиме пониженной нагрузки.Число заявок в регистре 16 заявок процессора в данном режиме меньше критического (К(К) и сигнал на выходе элемента ИЛИ 18 отсутствует. При выполнении программы обработки заявки 5 матора 121 по модулю два либо с выхода шифратора 118. Регистр 120 используется для хранения адреса очередной микрокоманды и выдачи его на выход 123 Формирователя 39 адреса 20 микрокоманд.формирователь 39 адреса микрокоманд функционирует следующим образом,Код операции с первого входа 115 .поступает на первый вход сумматора 25 121 по модулю два. Если на второй вхбд сумматора 121 по модулю два поступает, сигнал, то модифицированный сумматором код операции с выхода сумматора 121 через блок 119 элементов ЗО ИЛИ поступает на первый вход регистра 120 и через него - на выход 123 формирователя адреса микрокоманд.Если сигнал на третьем входе 117 Формирователя 39 адреса микрокоманд от сутствует, модификация кода операции не производится, он передается через сумматор 121 по модулю два на блок 119 элементов ИЛИ и с его выхода - на первый вход регистра 120.Адрес очередной микрокоманды по ступает на второй вход 116 Формирователя 41 микроопераций и записывается в регистр 120 по второму входу.На .четвертый вход 122 Формироватекоманды считываются из блока 7 основной памяти в регистр 8 данных. Код операции иэ регистра 8 данных поступает на Формирователь 39 .адреса микрокоманд. По выбранному адресу из блока 40 памяти микрокоманд, считывается первая микрокоманда микропрограммы обработки операндов для данной команды. При выполнении микропрограммы обработки операндов формирователь 41 микроопераций вырабатывает управляющие воздействия на входы блоков 1 и 10 элементов И, блоков 5 и 6 локальной памяти, операционных блоков 12 и 14 блока 7 основной памяти, по которым операнды для данной команды считываются из блока 7 основной памяти и через регистр 8 данных последовательно записываются в блоки 5 и 6 локальной памяти.Если в процессоре отсутствуют неисправности, то в каждый момент времени блоки 5 и 6 локальной памяти хранят. одинаковую информацию, В ходе обработки операнды пОловинной длины поступают из блоков 5 и 6 локальной памяти в первый 12 и второй 14 операционные блоки параллельно.и независимо. Для этих блоков формирователем 41 микроопераций задается выполнение одинаковых операций, Результат обработки в зависимости от выполняемой команды записывается по сигналам микроопераций из Формирователя 41 микро- операций либо в первый 5 и второй 6 блоки локальной памяти, либо через коммутатор 20 поступает на буферный регистр 26. Далее из регистра 8 данных считывается в блоки 5 и 6 локальной памяти через коммутатор, состоя-.щий из блоков 1,2,10 и 11 элементов И и блоков 3 и 4 элементов ИЛИ второй операнд и с ним производится аналогичная обработка.При выполнении команды записи обработанной информации в блок 7 основной памяти, информация с буферного регистра 26 сигналом с Формирователя 41 микроопераций передается в блок 7 основной памяти. После этого выбирается из блока 7 основной памяти следующая команда и процессор работает аналогично.Блок 38 сравнения сравнивает результаты обработки данных в первОм12 и втором 14 операционных блоках:при совпадении результатов никакихспециальных действий в процессоре непредпринимается и работа процессора продолжаетсяТаким образом, первым 12 и вторым14 операционными блоками выполняетсяпараллельная обработка одинаковыхданных половинной длины. Триггер 28управления, управляемый сигналамимикроопераций из Формирователя 41микроопераций, через элементы И 46 и983713 23 35 и элементы ИЛИ 30 и 47 разрешаетпрохождение информации через коммутатор 20 на буферный регистр 26 спервого 12 или с второго 14 операционных блоков. Если в первом 12 или втором 14 операционных блоках либо впервом 5 или втором 6 блоках локальной памяти прОисходит отказ, он обнаруживается блоком 38 сравнения иэ-за расхождения в результатах обработки.Сигнал с выхода блока 38 сравненияустанавливает в единичное состояние триггер 42 отказа, сигнал с единичного выхода которого запускает одновибратор 25. Сигнал с его;выхода запрещает запись обработанной информации в блок 7 основной памяти.и инициирует выдачу формирователем 39 адреса микрокоманд начального адреса микропрограммы обработки отказа.Адрес следующей микрокоманды, перед выполнением которой произошел отказ, запоминается в регистре 37 возврата через открытый сигналом с одновибратора 25 блок 36 элементов И,Для микропрограммы обработки отказав блоке 15 буферной памяти предусмотрено три области ячеек, Первая область предназначена для сохраненияадреса микрокоманды, перед выполнением которой в процессоре обнаруженотказ, а также для сохранения содержимого регистра 9 адреса. Вторая область служит для сохранения содержимого первого блока 5 локальной памяти и всех элементов памяти операционного блока 12. Третья область аналогинна второй и используется для сохранения состояния второго блока 6 локальной памяти и операционного блока 14.При выполнении микропрограммы обработки отказа происходит запоминание содержимого регистра 37 возврата и регистра 9 адреса в первой области блока 15 буферной памяти, затем поединичному состоянию триггера 28.управления через коммутатор 20 и буферный регистр 26 во вторую областьблока 15 буферной памяти сигналамииз Формирователя 41 микрооперацийперезаписывается информация из запоминающих элементов операционного блока 12 и содержимое блока 5 локальной памяти. После этого триггер 28 управления устанавливается в нулевое состояние и в третью область блока 15 буферной памяти перезаписывается состояние операционного блока 14 и блока 6 локальной памяти. Таким образом, состояние всех запоминающих элементов процессора сохраняется в блоке 15 буферной памяти, причем, в зависимости от места отказа, неискаженная информация записана либо во вторую, либо в третью область блока 15 буферной памяти. Локализация места отказа выполня ется микропрограммным диагностическим тестом, которому передает управление микропрограмма обработки отказа,Диагностический тест выполняется путем передачи тестовой информации в первый 5 и второй 6 блоки локальной памяти, в первый 12 и второй 14 опе 5 10 15 20 25 30 35 рационные блоки. Из блока 7 основнойпамяти считывается контрольная инФормация на первый 5 и второй 6 блокилокальной памяти. Результаты обработки этой информации в первом 12 и втором 14 операционных блоках раздельно подаются на входы блоков 32 и 43 сравнения. Этими блоками сравнения действительные результаты обработки данных в операционных блоках 12 и 14 сравниваются с ожидаемыми в результате тестирования (эталонными), которые подготавливаются блоком 31 памятиэталонов по кодам из формирователя 41 микроопераций.Результаты сравнения в блоках 32 и 43 сравнения накапливаютця регистрами 33 и 34 результатов теста. Весь диагностический тест состоит из ряда тестовых проверок, результат каждой из которых фиксируется отдельным разрядом регистров 33 и 44 результатов теста, После завершения выполне- . ния микропрограммы диагностического теста содержимое регистров результатов теста подается на информационные входы дешифраторов 34 и 45, на управляющие входы которых в это время подается управляющий сигнал с формирователя 41 микроопераций. При этом дешифратор исправного канала возбуждается, идентифицируя таким образом ис 40 правный канал, и его выходной сигнал через соответствующий элемент ИЛИ устанавливает триггер 28 управления в состояние, соответствующее исправному каналу, При этом передача обработан 45 ной информации осуществляется с исправного канала через коммутатор 20 вбуферный регистр 26. Предположим неисправность обнаружена в блоке 5 локальной памяти илИ в операционном блоке 12. При этом после выполнения микропрограммы обработки отказа срабатывает дешифратор 45 и через элемент ИЛИ 47 устанавливает триггер 28 управления в нулевое состояние. Формирователь 41 микроопераций формирует в регистре 9 адреса начальный адрес третьей области памяти блока 15 буферной памяти и возвращает управление микропрограмме обработки отказа. Если отказ обнаружен в блоке 6 локальной памяти или в операционном блоке 14, управление микропрограмме обработки отказа возвращается с предварительной установкой в единичное состояние триггера 28 управления и установкой в регистре 9 .адреса начального адреса второй области памяти блока 15 буферной памяти, После этого микропрограмма обработки отказа переписывает в операционные блоки 12 ( 14 ) и в блоки 5б ) локальной памяти информацию из той области памяти блока 15 буферной памяти, начальный адрес которой установлен в регистре 9 адреса.В результате этих операций эле менты памяти исправных блоков устанавливаются в состояние, соответствующее правильно выполняющейся обработке информации до возникновения отказа. Элементы памяти неисправных блоков 5 в работе процессора не участвуют. При завершении микропрограмм обработки отказа сигналымикроопераций из формирователя 41 микроопераций считывают из первой облаСти памяти блока 15 бу- щ ферной памяти в регистр 9 адреса адрес, хранящийся там в момент обнаружения отказа, и снимают блокировку записи в блоке 7 .основной памяти. В формирователь 39 адреса микрокоманд из блока 15 буферной памяти пересылается адрес микрокоманды, которая должна выполняться после обнаружения отказа, и обработка данных продолжается с того момента, в котором она была приостановлена обработкой отказа.Далее процессор продолжает обрабатывать информацию в одноканальном режиме. После восстановления отказавшего канала все элементы процессора устанавливаются в начальное состояние З и далее он функционирует в двухканальном режиме.Работа процессора во время повышенной нагрузки.Если число заявок в регистре Хб 40 заявок больше критического, возбуждается одна из выходных шин дешифратора 17 и этот сигнал через элемент ИЛИ 18, открытый сигналом микрооперации,элемент И 19 устанавливает в единичное состояние триггер 22 режима. Сигнал с единичного выхода триггера 22 режима открывает элемент И 13, поступает на элементы ИЛИ 27 и 29 и на вход формирователя 39 адреса микрокоманд. Сигнал с нулевого выхода триггера 22 режима открывает блоки 2 и 11 элементов И и закрывает блоки 1 и 10 элементов И и блок 38 сравнения,блокируя таким образом его работу на протяжении времени функционирования процессора во втором режиме.При этом старшиеразрядов опе 2ранда выполняемой команды из регистра 8 данных через блок 2 элементов И и блок 3 элементов ИЛИ записываются ф в блок 5 локальной памяти, а младшиеразрядов операнда через блок 11 Хэлементов И 11 и блок 4 элементов ИЛИ записываются в блок б локальной памяти. Таким образом, в .блоках 5 и 6 ло кальной памяти хранится операнд полной длины, состоящий изразрядов.При обработке этого операнда процессор функционирует в одноканальном режиме, в котором цепи переноса операционных блоков 12 и 14 соединены через открытый элемент И 13После обработки информации в расширенном операционном блоке, состоящем из блоков 12 и 14, сигналами микроопераций результат перезаписывается либо в блоки 5 и б локальной памяти либо с выходов операционных блоков 12 и 14 через коммутатор 20 - в буферный регистр 26 С выхода буферного регистра 26 сигналами микроопераций информация перезаписывается в блок 7 основноЦ памяти. Далее следующий операнд считывается с блока 7 основной памяти в регистр 8 данных и с ним производится аналогичная обработка. После выполнения очередной микропрограммы (обслуживания очередной заявки) формирователь 41 микро- операций выдает сигнал опроса состояний регистра 16 заявок путем подачи микрооперации на вход элемента И 23 и элемента 21 задержки. Если число заявок в регистре 16 заявок больше критического, элемент И 23 закрыт и триггер 22 режима остается в прежнем состоянии. Процессор приступает к обработке следующей заявки, а сигнал микрооперации через элемент 21 задернки устанавливает регистр 16 заявок в нулевое состояние.Если при опросе регистра 16 заявок число заявок в нем меньше критического, сигнал микрооперации через элемент И 23 устанавливает триггер 22 режима в нулевое состояние, При этом блоки 2 и 11 элементов И и эле" мент И 13 закрываются, а блоки 1 и 10 элементов И открываются. Процессор переходит в двухканальный режим функиционирования при К(К, описанный выше.Если в процессоре во время функционирования в двухканальном Режиме возникает отказ в одном из каналов, триггер отказа устанавливается в единичное состояние. При этом элемент И 19 закрывается по третьему входу и таким образом блокируется реакция процессора на число заявок в регистре 16 заявок. После восстановления отказа триггер 42 отказа сигналом микрооперации устанавливается в нулевое состояние, элемент И 19 при этом открывается. Следовательно, перестраиваеьый микропрограммный процессор существенно превосходит известное устройство по объему используемого оборудования.Использование предлагаемого процессора позволит повысить эффективность вычислительных систем, обслужи 9837132827, вающих нестационарные потоки заявок, например, в автоматических системах коммутации,Формула изобретения1. Перестраиваемый микропрограммный процессор, содержащий первый и второй блоки локальной памяти, первый и второй операционные блоки, блок О основной памяти, регистр адреса, регистр данных, блок буферной памяти, буферный регистр, коммутатор, триггер управления, блок памяти эталонов, первый, второй и третий блоки сравнения, первый и второй регистры результата, первый и второй дешифраторы, Формирователь адреса микрокоманд, блок памяти микрокоманд, Формирователь микроопераций, первый блок элементов И, регистр возврата, причем первый выход регистра данных соединен с первым входом регистра адреса, выход которого соединен с адресными входами блоков буферной и основной памяти, выход блока основной памяти соединен с первым информационным входом регистра данных, второй выход которого соединен с входом кода операций формирователя адреса микрокоманд, первый и второй выходы коммутатора соединены соответственно с первыми.и вторыми входами буферного регистра, выход которого соединен с первыми информационными входами блоков буферной и основной памяти, выход первого З 5 блока элементов И соединен с входом регистра возврата, выход которого соединен с вторым информационным входом блока буферной памяти, выход микро- операций формирователя микроопераций 46 соединен с первым управляющим входом коммутатора, с первым управляющим входом блока основной памяти, с управляющим входом регистра адреса, с управляющими входами первого и второ го регистров результата, первого и второго дешифраторов, первого и второго блоков локальной памяти, первого и второго операционных блоков и первым управляющим входом блока буфернойпамяти, выход которого соединен с вторым информационным входом регистра данных, выход формирователя адреса микрокоманд соединен с входом блока памяти микрокоманд и с первыми входами первого блока элементов И, вторые входы которого соединены с управляющим входом Формирователя адреса микрокоманд, выход блока памяти микро- команд соединен с входом Формирователя микроопераций, выходы адреса мик- фф рокоманд и адреса эталонов которого соединены соответственно с адресный входом Формирователя адреса микрокоманд и с входом блока памяти эталонов, выходы первого и второго блоков ло кальной памяти соединены соответственно с информационными входами первогои второго операционных блоков, первые информационные выходы которыхсоединены с первыми информационными .входами первого и второго блоков локальной памяти соответственно, второй информационный выход первогооперационного блока соединен с первыминформационным входом коммутатора и спервыми входами первого и второгоблоков сравнения, выход первого изкоторых соединен с информационнымвходом первого регистра результата,второй информационный выход второгооперационного блока соединен с вторым информационным входом коммутатора, с вторым входом первого блокасравнения и с первым входом третьегоблока сравнения, выход которого соединен с информационным входом второгорегистра результата, выход блока памяти эталонов соединен с вторыми входами второго и третьего блоков сравнения, выходы первого и второго регистров результата соединевы с информационными входами первого и второгодешифраторов, о т л и ч а ю щ и й с ятем, что, с целью сокращения оборудования, в устройство введены второй,третий, четвертый и пятый блоки элементов И, первый и второй блоки элементов ИЛИ, первый, второй, третий,четвертый и пятый элементы И, первый,второй, третий, четвертый и пятыйэлементы ИЛИ,третий дешифратор, одновибратор, элемент задержки, регистрзаявок, триггер режима и триггер отказа, причем выход первого блока:сравнения соединен с единичным входомтриггера отказа, единичный выход которого через одновибратор соединен суправляющим входом формирователя адреса микрокоманд. и вторым управляющим входом блока основной памяти,нулевой выход триггера отказа соединен с первыми входами первого, второго и третьего элементов И, выход которого соединен с первым входом первого элемента ИЛИ, выходы первого ивторого дешифраторов соединены соответственно с первым входом второгоэлемента ИЛИ и вторым входом первогоэлемента ИЛИ, выходы которых соединены соответственно с единичным и нулевым входами триггера управления,выход микроопераций Формирователямикроопераций соединен с нулевым входом триггера отказа, через элементзадержки - с установочным входом ре.гистра заявок, вторым входом первогоэлемента И, первым входом четвертогоэлемента И, первыми входами второгои третьего блоков элементов И, вторыми входами третьего и второго элемеНтов И, выход которого соединен свторым входом второго элемента ИЛИ,входы заявок устройства соединены синформационными входами регистра з а- явок, выход которого соединен с входами третьего дешифратора, выходы дешифратора соединены с входами третьего элемента ИЛИ, выход которого соединен с третьим входом первого 5 элемента И и инверсным входом четвертого элемента И, выходы которых соединены соответственно с единичным и нулевым входами триггера режима, нулевой выход триггера режима соединен 10 с управляющим входом первого блока сравнения, с вторыми входами второго и третьего блоков элементов И и инверсными входами четвертого и пятого блоков элементов И, выходы которых соединены соответственно с первыми входами первого и второго блоков элементов ИЛИ, единичный выход триггера режима соединен с первым входом пятого элемента И, вторым управляющим входом формирователя адреса микрокоманд и первыми входами третьего и четвертого элементов ИЛИ, выходы которых соединены соответственно с вторым и третьим управляющими входами коммутатора, единичный и нулевой выходы триггера управления соединены с вторыми входами третьего и четвертого элементов ИЛИ соответственно, второй выход регистра данных соединен с прямыми входами четвертого и пятого блоков элементов И и с третьими входами второго и третьего элементов И, выход которого соединен с вторыми входами первого и второго блоков элементов ИЛИ, выход второго блока элементов И соединен с третьими входами первого и второго блоков элементов ИЛИ, выходы которых соединены соответственно с вторыми информационными входами первого и второго блоков локальной памяти, выход переноса первого операционного блока соединен с вторым входом пятого элемента И, выход которого соединен с входом переноса второго операционного блока. 452. Устройство по п.1, о т л и ч аю щ е е с я тем, что операционный блок содержит дешифратор, шифратор, первую и вторую группы элементов И, группу элементов 2 И-ИЛИ, сумматор и Я регистр, причем управляющий вход операционного блока соединен с входом дешифратора, выход которого соединен с входом шифратора, выход шифратора ,соединен с управляюцими входами пер- у вой и второй групп элементов И, с управляющими .входами первой и второй групп входов группы элементов 2 И-ИЛИ и с управляющим входом регистра, выход которого соединен с информацион- еО ным входом первой группы входов группы элементов 2 И-ИЛИ и информационными входами первой и второй групп элементов И, выходы первой и второй групп элементов И являются первым и вторым информационными выходами операционного блока, информационный вход и вход переноса операционного блока соединены соответственно с информационным входом второй группы входов группы элементов 2 И-ИЛИ и с входом переноса сумматора, выходы переноса и суммы которого соединены соответственно с выходом переноса операционного блока и информационным входом регистра, выход группы элементов 2 И-ИЛИ соединен с информационным входом сумматора.3. Устройство по п.1, о т л и ч аю щ е е с я тем, что формирователь адреса микрокоманд содержит регистр адреса микрокоманд, шифратор, группу элементов ИЛИ и сумматор по модулю два, причем первый, второй управляюцие входы, входы кода операции и адреса формирователя адреса микрокоманд соединены соответственно с входом шифратора, первым и вторым входами сумматора по модулю два и первым информационным входом регистра адреса микрокоманд, выход которого является выходом формирователя адреса микро- команд, выходы шифратора и сумматора по модулю два соединены с входами группы элементов ИЛИ, выход которой соединен с вторым информационным входом регистра адреса микрокоманд,4Устройство по п.1, о т л и ч аю щ е е с я тем, что формирователь микроппераций содержит регистр микрокоманд и группу дешифраторов, причем вход формирователя микроопераций соединен с входом регистра мйкрокоманд, выходы которого соединены с входами дешифраторов, выходы дешифраторов соединены с выходом микроопераций и адреса эталонов Формирователя, адресный выход регистра микрокоманд является выходом адреса микрокоманд Формирователя микроопераций.Источники информации,принятые во внимание при экспертизе1. Методы автоматического возвратак программе в вычислительной машинеСОРКА. Экспресс-инФормация, сер. "Вычислительная техника", Р 20, 1978.2. Патент СВ 1 А Р 3848116,кл. 235 в 153, опублик. 1976.3. Той В,Н. Проектирование отказоустойчивых местных процессоров длясистем электронной коммутации.ТИИЭР,1978, 9 10, с.26-47.4. Арторсное свидетельство СССРУ 763902, кл, 0 06 Г 15/00, 1980983713г.ЮФиг ВНИИПИ Заказ 9927/59 Тираж 731 Подписно Филиал ППП "Патент", г.Ужгород, ул.Проектная,4которого соединен с вторым входомрегистра данных, второй выход которого соединен с первым входом формирователя адреса микрокоманд, второйвход которого соединен с первым выходом формирователя микроопераций, 5вход которого соединен с выходом бло.ка памяти микрокоманд, второй выход., с входом генератора эталонов, выходкоторого соединен с первыми входамипервой и второй схем сравнения, выхо ды которых соединены с информационными входами первого и второго регистров результатов теста соответственно,выходы которых соединены с информационными входами первого и второго дешифраторов соответственно, первыйвход третьей схемы сравнения соединен с вторым входом первой схемысравнения, первым входом коммутатораи .первым выходом первого операционного блока, второй выход которогосоединен с первым входом первого блока локальной памяти, выход которогосоединен с первым входом первогооперационного блока, второй входтретьей схемы сравнения соединен свторым входом второй схемы сравнения,вторым входомкоммутатора и первымвыходом второго операционного блока,второй выход которого соединен с первым входом второго блока локальной ЗОпамяти, выход которого соединен спервым входом второго операционногоблока, третий выход ФормирЬвателямикроопераций соединен с четвертымвходом блока .буферной памяти, вторым 35входом регистра адреса, четвертымвходом блока. основной памяти, с вторыми входами первого и второго дешифраторов, с вторыми входами первого ивторого регистров результатов теста, 40с вторыми входами первого и .второгооперационных блоков, с вторыми входами первого и второго блоков локальной памяти (4 3.Недостатками указанного процессора 45являются большой объем оборудованияи низкая достоверность функционирова"ния,В известном устройстве реализуется следующая дисциплина Функционирования.Результаты работы двух параллельнофункционирующих каналов обработки информации сравниваются. При их совпадении осуществляется обмен данными сблоком основной памяти процессора.При этом один канал Функционируеткак основной, а другой - как резервный. В случае несовпадения результатов обработки информации в двух каналах третья схема сравнения формируетуправляющий сигнал, по которому запускаются микропрограмма обработки отказа, в ходе выполнения которой работапроцессора блокируется, содержимоеканалов передается в блок буферной 65 памяти, а затем с использованием специального диагностического оборудования определяется отказавший канал, По результатам диагностики определяется работоспособность канала, восстанавливается его содержимое и процессор продолжает работу в одноканальномрежиме,Большой объем оборудования процессора объясняется следующей причиной.В процессоре отсутствуют средства адаптации к нагрузке (например, кчислу обслуживаемых абонентов при использовании процессора в системе коммутации), которая в зависимости от условий функционирования может меняться (при работе систем .коммутации имеется период времени, так называемый час наибольшей нагрузки, когда число подключаемых абонентов максимально и требуется обеспечить максимальную производительность процессора. В остальное время нагрузка резкоуменьшается и процессор. может работать с минимальной производительностью). В связи с этим, каждый иэ каналов процессора рассчитан на работу со словами полной длины (например, 32-битными), считываемыми из блока основной памяти. Обработка слов полной длины обеспечивает требуемую производительность при максимальной нагрузке, которая обычно сохраняет небольшой отрезок времени, имеющий незначительную относительную величину, (в системах коммутации максимальная нагрузка сохраняется обычно втечение 1-2 ч эа сутки). Следовательно, большую часть времени, когда процессор может работать с меньшей производительностью (например, засчет обработки полуслов длиной 16 бит)вычислительные мощности процессора используются неэффективно. Это обуславливает большую структурную избыточность, процессора, которая приводит к существенным дополнительным затратам оборудования (т.е. практически к удвоению его объема), и вызывает низкую достоверность функционирования за счет увеличения вероятности парных ошибок в каналах.укаэанные недостатки, в свою очередь, обуславливают также большое время диагностирования при выходе иэ строя одного иэ каналов вследствие большой размерности проверяемого объекта (канала), что в конечном итоге снижает коэффициент технической готовности.Целью изобретения является сокращение оборудования.Поставленная цель достигается тем, что в перестраиваеьый микропрограммный процессор, содержащий первый и второй блоки локальной памяти, первый и второй операционные блоки, блок основной памяти, регистр адреса,. 983713 блоков сравнения, выход первого изкоторых соединен с информационнымвходом первого регистра результата,второй информационный выход второгооперационного блока соединен с вторым 5 информационным входом коммутатора, свторым входом первого блока сравненияи с первым входом третьего блокасравнения, выход которого соединен оинформационным входом второго регист О ра результата, выход блока памятиэталонов соединен с вторыми входамивторого и третьего блоков сравнения,выходы первого и второго регистроврезультата соединены с информационны"ми входами первого и второго дешифраторов, введены второй, третий, четвертый и пятый блоки элементов И,первый и второй блоки элементов ИЛИ,первый, второй, третий, четвертыйи пятый элементы И, первый, второй,третий, четвертый и пятый элементыИЛИ, третий дешифратор, одновибратор,элемент задержки, регистр заявок,триггер режима и триггер отказа,причем выход первого блока сравнениясоединен с единичным входом триггераотказа, единичный выход которого че"рез одновибратор соединен с управляющим входом формирователя адреса микрокоманд и вторым управляющим входомблока основной памяти, нулевой выходтриггера отказа соединен с первымивходами первого, второго и третьегоэлементов И, выход которого соединенс первым входом первого элемента ИЛИ, 35 выходы первого и второго дешифраторовсоединены соответственно с первымвходом второго элемента ИЛИ и вторымвходом первого элемента ИЛИ, выходыкоторых соединены соответствеино с 40 единичным и нулевым входами триггерауправления, выход микроопераций формирователя микроопераций соединен снулевым входом триггера отказа, черезэлемент задержки - с установочнымвходом регистра заявок, вторым входом первого элемента И, первым входрм четвертого элемента И, первымивходами второго и третьего блоковэлементов И, вторыми входами третьегои второго элементов И, выход которого соединен с вторым входом второгоэлемента ИЛИ, входы заявок устрой.ства соединены с информационнымивходами регистра заявок, выход которого соединен с входами третьего дешифратора, выходы дешифратора соединены с входами третьего элемента ИЛИ,выход которого соединен с третьимвходом первого элемента И и инверсным входом четвертого элемента И, 40 выходы которых соединены соответственно с единичным и нулевым вхОдамитриггера режима, нулевой выход триггера режима соединен с управляющимвходом первого блока сравнения, с ков буферной и основной памяти, выход регистр данных, блок буферной памяти, буферный регистр, коммутатор,триггер управления, блок памяти эталонов, первый, второй и третий блокисравнения, первый и второй регистрырезультата, первый и второй дешифраторы, формирователь адреса микрокоманд, блок памяти микрокоманд, формирователь микроопераций, первыйблок элементов И, регистр возврата,причем первый выход регистра данныхсоединен с первым входом регистра адреса, выход которого соединен с адресными входами блоков буферной и основной памяти, выход блока основнойпамяти соединен с первым информационным входом регистра данных, второй выход которого соединен с входом кода операций формирователя адреса микрокоманд, первый и второй выходы коммутатора соединены соответственно спервыми и вторыми входами буферногорегистра, выход которого соединен спервыми информационными входами блопервого блока элементов И соединенс входом регистра возврата, выход которого соединен с вторым информационным входом блока буферной памяти,выход микроопераций формирователямикроопераций соединен с первымуправляющим входом коммутатора, спервым управляющим входом блока основной памяти, с управляющим входомрегистра адреса, с управляющими входами первого и второго регистроврезультата, первого и второго дешифраторов, первого и второго блоковлокальной памяти, первого и второго операционных блоков и первым управляющим входом блока буферной памяти, выход которого соединен с вторым информационным входом регистра данных, выход формирователя адреса микрокоманд соединен с входом блока памяти микрокоманд и с первыми входами первого блока элементов И, вторые входыкоторого соединены с управляющимвходом формирователя адреса микрокоманд, выход блока памяти микрокоманд соединен с входом формирователямикроопераций, выходы адреса микрокоманд и адреса эталонов которого соединены соответственно с адресным входом формирователя адреса микрокоманд и с вторым входом блока памяти эталонов, выходы первого и второго блоков локальной памяти соединены соответственно с информационными входамипервого и второго операционных блоков, первые информационные выходы которых соединены с первыми информационными входами первого и второго блоков локальнойпамяти соответственно,второй иНформационный выход первого операционного блока соединен с первыминформационным входом коммутатора ис первыми входами первого и второго вторыми входами второго и третьегоблоков элементов И и инверсными входами четвертого и пятого блоков элементов И, выходы которых соединенысоответственно с первыми входами первого и второго блоков элементов ИЛИ, единичный выход триггера режима соединен с первым входом пятого элемента И, вторым управляющим входом Формирователя адреса микрокоманд и первыми входами третьего и четвертого элементов ИЛИ, выходы которых соедииены соответственно с вторым и третьим управляющими входами коммутатора, единичный и нулевой выходы триггера управления соединены с вторыми входами третьего и четвертого элементов ИЛИ соответственно, второй выходрегистра даяных соединен с прямыми входами четвертого и пятого блоков элементов И и с третьими входами второго и третьего элементов И, выходкоторого соединен с вторыми входамипЕрвого и второго блоков элементовИЛИ, выход второго блока элементов Исоединен с третьими входами первогои второго блоков элементов ИЛИ, выходы которых соединены соответственнос вторыми информационными входамипервого и второго блоков локальнойпамяти, выход переноса первого операционного блока соединен с вторымвходом пятого элемента И, выход которого соединен с входом переноса второго операционного блока.При этом операционный блок содержит дешифратор, шифратор, первую и вторую группы элементов И, группуэлементов 2 И-ИЛИ, сумматор и регистр, причем управляющий вход операционного блока соединен с входом дешифратора, выход которого соединен с входомшифратора, выход шифратора соединен с управляюшими входами первой и второй групп элементов И, с управляющими входами первой и второй групп входов грУппы элементов 2 И-ИЛИ и с управляюцим входом регистра, выход которого соединен с информационным входом первой группы входов группы элементов 2 И-ИЛИ и информационнымивходами первой и второй групп элементов И, выходы первой и второй группэлементов И являются первым и вторыминформационными выходами операционного блока, информационный вход и вход переноса операционного блока соединены соответственно с информационным входом второй группы входов группы элементов 2 И-ИЛИ и с входом переноса сумматора, выходы переносаи суммы которого соединены соответственно с выходом. переноса операционного блока и информационным входом регистра, выход группы элементов2 И-ИЛИ соединен с информационным входом сумматора. Кроме того, формирователь адреса микрокоманд содержит регистр адресамикрокоманд, шифратор, группу элементов ИЛИ и сумматор по модулю два,причем первый, второй управляющиевходы, входы кода операции и адресаформирователя адреса микрокоманд сое динены соответственно с входом шифратора, первым и вторым входами сумматора по модулю два и первым информационным входом регистра адреса микрокоманд, выход которого является вы О ходом формирователя адреса микрокоманд, выходы шифратора и сумматорапо модулю два соединены с входамигруппы элементов ИЛИ, выход которойсоединен с вторым информационным вхо дом регистра адреса микрокоманд.Формирователь микроопераций содержит регистр микрокоманд и группу дешифраторов, причем вход формирователямикроопераций соединен с входом регистра микрокоманд, выходы которогосоединены с входами дешифраторов, выходы дешифраторов соединены с выходоммикроопераций и адреса эталонов формирователя, адресный выход регистрамикрокоманд является выходом адресамикрокоманд формирователя микроопераций.Сущность изобретения состоит в сокрашении используемого оборудованияпроцессора путем адаптации структуры З 0 к подключаемой нагрузке (числу заявокна обслуживание).Если число заявок К, поступающихна обслуживание, меньше критическогоК, соответствующего максимальной наЗ 5 грузке, предлагаемый процессор работает в двухканальном режиме также,как и известное устройство. Отличиесостоит в том, что каждое слово, считываемое из блоков основной памяти, 40 обрабатывается за два такта, поскольку каналы имеют разрядность, соответствующую половине слова. В первомтакте обрабатывается первое полуслово - параллельно в двух каналах со 45 сравнением результатов, а во второмвторое полуслово. Формируемый результат передается в основную память. Таким образом, при К ( К процессоросуществляет обработку полуслов двумяканалами. При отказе одного из каналов обработки информации запускаетсямикропрограмма обработки отказа, обнаруживается отказавший канал и процессор переходит в одноканальный режим функционирования. При восстановлении работоспособности отказавшегоканала, процессор переходит в двухканальный режим функционирования.Если число заявок на обслуживаниебольше или равно критическому (Х Ъ К ),процессор переходит к обработке словполной длины. При этом рабочий и контрольный каналы обработки информациипутем соответствующей коммутацииобъединяются в один канал обработкислов(операндов) полной длины. Приэтом производительность процессора увеличивается в два раза. После выполнения каждой микропрограммы процессор анализирует число необслуженных заявок. Если К),К, работа в одноканальном режиме по обработке операндов полной длины продолжается, если Кс , перед выполнением следующей микропрограммы процессор переходит в двухканальный режим работы по обработке операндов половинной длины и 10 работает аналогиЧно описанному. После выполнения очередной микропрограммы (обслуживания заявки) опрашивается количество необслуженных заявок и работа процессора продолжается аналогично описанному алгоритму. Осуществление реконфигурации структуры процессора с учетом подключаемой нагрузки (числа заявок) позволяет производить обработку информации более простыми операционными блоками, а, следовательно, сократить объем исполь,зуемого оборудования процессора.В предлагаемый микропрограммный процессор введены четыре блока элементов И, два блока элементов ИЛИ, пять элементов И, пять элементов ИЛИ, одновибратор, триггер отказа, регистр заявок, элемент задержки, третий дешифратор, триггер режима.Код микрокоманды, считываемой из , блока памяти микрокоманд в формирователь микроопераций, разбит на три поля: первое поле - код адреса следующей микрокоманды; второе поле - код выполняемых микроопераций; третье 35 поле - код адреса эталона, подаваемого в генератор эталонов.Введение второго - четвертого блоков элементов И, первого и второго блоков элементОв ИЛИ и обусловленных 40 ими. связей позволяет в зависимости от режима работы процессора .записывать одинаковые операнды в оба блока локальной памяти или, в случае обработки операнда полной длины, т/2 старших д 5 разрядов операнда в первый блок локальной памяти имладших разрядов2операнда во второй. блок локальной памяти.Введение пятого элемента И и 50 обусловленных им связей позволяет обеспечить перенос между сумматорами первого и второго операционных блоков в режиме обработки операндов полной длины.55Введение регистра заявок, третьего дешифратора, третьего элемента ИЛИ, первого элемента И, триггера режима и обусловленных ими связей позволяет изменять режим функционирования процессора. Если в регистре заявок число заявок Кк , на выходе третьего дешифратора появляется сигнал, который через третий элемент ИЛИ и первый элемент И воздействует на единичный вход триггера режима и переводит 65 его в единичное состояние. Единичное состояние триггера соответствует ре- жиму функционирования процессора при Кък.Если К- , появление сигнала на подключенных выходах третьего дешифратора не происходит и триггер режима находится в нулевом состоянии. При этом процессор функционирует в двухканальном режиме по обработке оперантов половинной длины.Введение элемента задержки и обусловленных им связей необходимо для обнуления регистра заявок после каждого опроса его состояния.Введение четвертого элемента И и 1обусловленных им связей необходимо для перехода от режима работы процессора при К Ъ К к режиму работы при К Х, что обеспечивается установкой в нулевое состояние триггера режима.Введение триггера отказа и обусловленных им связей необходимо для запуска микропрограммы обработки отказа и запрета управления триггером управления сигналами микроопераций и триггером режима.Введение второго и третьего элементов И и первого и второго элементов ИЛИ и обусловленных ими связей позволяет управлять работой триггера управления либо сигналами микроопераций, либо сигналами с выходов первого и второго дешифраторов.Введение второго одновибратора и обусловленных им связей позволяет формировать сигнал запуска микропрограммы обработки отказа и блокировки записи в блок основной памяти.Введение третьего и четвертого элементов ИЛИ и обусловленных ими связей, а также связи между третьим формирователем микроопераций и первым управляющим входом коммутатора, позволяет записывать обработанную информацию в буферный регистр в зависимости от режима работы либо параллельно с первого и второго операционных блоков при работе в одноканальном режиме обработки операндов полной длины, либо последовательно переписывать с рабочего операционного блокамладших и - старших разрядов обработанных операндов.Таким образом, введение новых элементов и указанных связей позволяет существенно повысить эффективность микропрограммного процессора на основе адаптации его структуры к условиям функционирования. На фиг.1 приведена функциональная схема перестраиваемого микропрограммного процессора; на фиг.2 -функциональная схема блока локальной памяти; на фиг.З - то же, блока основной памяти; на фиг.4 - то же, формирователя микроопераций; на фиг.5 - то же, вто 983713 12рого операционного блока; на фнг.6то же, блока буферной памяти; нафиг.7 - то же, блока памяти эталонов;на фиг.8 - то же, формирователя адреса микрокоманд.Перестраиваеьюй микропрограммныйпроцессор содержит (фиг.1) второйблок 1 элементов И, четвертый блок 2элементов И, первый блок 3 элементовИЛИ, второй блок 4 элементов ИЛИ,первый блок 5 локальной памяти, вто Орой блок 6 локальной памяти, блок 7основной памяти, регистр 8 данных,регистр 9 адреса, третий блок 10 элементов И, пятый блок 11 элементов И,первый операционный блок 12, пятый 15элемент И 13, второй операционныйблок 14, блок 15 буферной памяти, регистр 16 заявок, третий дешифратор17, третий элемент ИЛИ 18, первыйэлемент И 19, коммутатор 20, состоял 2 Ощий из блоков элементов И и блоковэлементов ИЛИ, элемент 21 задержки,триггер 22 режима, четвертый элементИ 23, входы 24 заявок,одновибратор25, буферный регистр 26, третий 25элемент ИЛИ 27, триггер 28 управления, четвертый элемент ИЛИ 29, второйэлемент ИЛИ 30, блок 31 памяти эталонов, второй блок 32 сравнения,первый регистр 33 результата, первый дешифратор 34, второй элемент И 35,первый блок 36 элементов И, регистр37 возврата, первый блок 38 сравнения, формирователь 39 адреса микрокоманд, блок 40 памяти микрокоманд,формирователь 41 микроопераций, триггер 42,отказа, третий блок 43 сравнения, второй регистр 44 результата,второй дешифратор 45, третий элементИ 46, первый элемент ИЛИ 47,Блок локальной памяти включает 40(фиг.2) дешифратор 4.8, шифратор 49,групп 50 элементов 2 И-ИЛИ, и -регистров 51,п групп 52 элементов И,выход 53 блока 15 буферной памяти,первый 54, второй 55 и третий 56 входы блока 15 буферной памяти.Блок основной памяти содержит(фиг.З) первый 57, второй 58, третий59 и четвертый 60 входы блока 7 основной памяти соответственно, блок 5661 элементов И, накопитель 62, первый63 и второй 64 элементы И соответственно, триггер 65, выход 66 .блока 7 основной памяти, входы 67 и 68 синхроимпульсов записи и считывания,В формирователь микроопераций входят (фиг.4) вход 69, регистр 70 микрокоманд,группа дешифраторов 71 кодамикроопераций, дешифратор 72 кодамикрокоманд запуска генератора этало-нов, первый 73, второй 74 и третий75 выходи формирователя 41 микрооперчций соответственно.Операционные блоки выполнены по одной и той же схеме (фиг.5) и содержат первый 76, второй 77 и третий 78 входы второго операционного блока 14, дешифратор 79, шифратор 80, группу 81 элементов 2 И-ИЛИ, сумматор 82, регистр 83, первую 84 и вторую 85 группы элементов И, первый 86 и второй 87 выходы второго операционного блока 14, выход 88 переноса (в первом операционном блоке не используется).Блок буфернойпамяти включает (Фиг.6) первый 89, второй 90, третий 91 и четвертый 92 входы блока 15 буФерной памяти, второй блок 93 элементов И, накопитель 94, блок 95 элементов ИЛИ, выход 96 блока 15 буферной памяти 15, первый элемент И 97, выход 98 генератора импульсов записи, второй элемент И 99, выход 100 генератора импульсов считывания, первый, вход 101 накопителя, первый блок 102 элементов И, второй регистр 103, пятый блок 104 элементов И, второй вход 105 накопителя, третий блок 106 элементов И, первый регистр 107, четвертый блок 108 элементов И.В блоке памяти эталонов находятся (фиг,7) вход 109 генератора эталонов, блок 110 элементов ИЛИ, дешифратор 111, блок 112 памяти эталонов, регистр 113, выход 114 генератора эталонов.Формирователь адреса микрокоманда включает (фиг.8) первый 115, второй 116 и третий 117 входы формирователя 39 адреса микрокоманд, шифратор 118, группу 119 элементов ИЛИ, регистр 120, сумматор 121 по модулю два,четвертый вход 122 формирователя ад" реса микрокоманд, выход 123 формирователя адреса микрокоманд.Назначение основных элементов функциональной схемы микропрограммного процессора (фиг.1) состоит в следующем: второй в .пятый блоки 1, 10, 2 и 11 элементов И, первый и второй блоки 3 и 4 элементов ИЛИ предназначены для передачи операндов из регистра 8 данных в первый 5 и второй 6 блоки локальной памяти в порядке, определяемом поступающими сигналами микроопераций и сигналом с нулевого выхода триггера 22 режима. Блоки 5 и 6 локальной памяти предназначены для хранения операндов (частей операндов в одноканальном режиме функционирования при К),К) и промежуточных результатов обработки информации.Операционные блоки 12 и 14 осуществляют преобразование информации по микрооперациям, поступающими с третьего выхода формирователя 41 микроопераций. При работе в одноканальном режиме (К)К) операционные блоки функционируют как один операционный блок с полной разрядностью обрабатываемых операндов. Пятый элемент И 13предназначен для обеспечения цепи переноса между сумматорами первого 12 и второго 14 операционных блоков,На первые входы операционных блоков 12 и 14 поступает информация с выходов соответствующих блоков ло кальной памяти. Результаты обработки выдаются либо на первые входы блоков 5 и б локальной памяти, либо на первый и второй входы коммутатора 20 и на первый блок 38 сравнения для срав нения.Блок 7 основной памяти предназначен для хранения данных и команд для их обработки.Регистр 8 данных предназначен для приема и хранения очередных команд и данных выполняемой программы, поступаюцих из блока 7 основной памяти на первый вход, и данных, поступающих из блока 15 буферной памяти на второй вход. Операнды с второго выхода регистра поступают на вторые входы второго - пятого блоков 1, 10, 2 и 11 элементов И, а код операции - на первый вход формирователя 39 адреса микрокоманд.Регистр 9 адреса предназначен для хранения адреса следующей команды.Блок 15 буферной памяти предназначен для хранения информации, находящейся на момент отказа в блоках 5 и б локальной памяти, в операционных блоках 12 и 14, в регистре 9 адреса, в регистре 37 возврата и выдачи ее после выполнения микропрограммы обработки отказа через регистр 8 данных 35 в соответствующие блоки.Регистр 16 заявок предназначен для хранения числа заявок на обслуживание поступивших на процессор от потребителей, 40Третий дешифратор 17 предназначен для выдачи сигнала на выходе при Къс. Третий элемент ИЛИ 18 и первый элемент И 19 предназначены для формирования сигнала установки в единичное состояние триггера 22 режима. Четвертый элемент И 23 предназначен для установки в нуль триггера 22 режима. Элемент 21 задержки предназначен для обнуления регистра 16 заявок после 50 его опроса.Коммутатор 20 предназначен для обеспечения перезаписи обработанной информации с вторых выходов операционных блоков 12 и 14 на первый и второй входы буферного регистра 26 в зависимости от управляющих сигналов, поступаюцих на его первый - третий управляющие входы от четвертого 29 и третьего 27 элементов ИЛИ и третьего выхода Формирователя 41 микроопераций.6 ОБуферный регистр 26 предназначен для Формирования и хранения обработанной информации перед записью ее в блок 7 основной памяти или в блок 16 буферной памяти. 65 Четвертый 29 и третий 27 элементыИЛИ предназначены для формированияуправляющих сигналов на третий и четвертый вход коммутатора 20 по сигналам, поступающим на их входы с единичного выхода триггера 22 режима,и выхода триггера 28 управления.Триггер 28 управления предназначен для управления выдачи информациичерез коммутатор 20 от первого 12 иивторого 14 операционных блоков в двухканальном режиме работы процессораили из исправного канала при возникновении отказа в одном из каналов.Третий 46 и второй 35 элементы И ивторой 30 и первый 47 элементы ИЛИпредназначены для формирования сигналов управления: единичный и нулевой.вход триггера 28 управления - посигналам микроопераций с третьеговыхода формирователя 41 микроопераций,сигналам с выходов первого 34 и второго 45 дешифраторов и нулевого выхода триггера 42 отказа,Первый блок 38 сравнения предназначен для сравнения результатов обработки информации в первом 12 и втором14 операционных блоках и выдачи, приналичии управляющего сигнала на управляющем входе, сигнала рассогласования на выходе при несовпадении результатов обработки информации, Блок31 памяти эталонов предназначен дляформирования эталонных последовательностей и выдачи их на второй 32 итретий 43 блоки сравнения при выпол-нении микропрограммы диагноетики процессора.Блоки 32 и 43 сравнения предназначены для сравнения результатов обработки контрольной информации первым12 и вторым 14 операционными блоками с ожидаемыми результатами тестирования (эталонными), которые выдаютсяблоком 31 памяти эталонов в режимевыполнения микропрограммы диагностикиПервый 33 и второй 44 регистры результатов теста предназначены длянакопления информации о первом 12 ивтором 14 операционных блоках.Весь диагностический тест. состоитиз целого ряда диагностических проверок, результат каждой из которых Фиксируется отдельным битом первого 33 ивторого 44 регистров результата теста. На вторые (сдвигаюцие) входы регистров 33 и 44 результата 31 подается сигнал микрооперации, по которому осуществляется сдвиг информации в регистрах,Первый 34 и второй 45 дешифраторы предназначены для идентификации исправности соответствующего канала обработки информации по содержимому первого 33 и второго 44 регистров результата теста.В конце микропрограммы диагностикидешифраторы 34 и 45 срабатывают попоступлении управляющего сигнала сформирователя 41 микроопераций, и вслучае, если в одном из регистров 33и 44 результата записана комбинация,соответствующая исправному состояниюканала информации, на выходе соответствующего дешифратора появляется сигнал, который через второй элементИЛИ 30 или первый элемент ИЛИ 47 устанавливает триггер 28 управления внулевое состояние,Одновибратор 25 предназначен длявыдачи сигнала запуска,микропрограм-,мы обработки отказа в формирователь 1539 адреса микрокоманд, блокировки записи информации нз буферного регист-,ра 26 в блок 7 основной памяти, запи)си в .регистр 37 возврата через первыйблок 36 элементов И адреса микроко- щманды, перед выполнением которойпроизошел отказ одного из каналовпроцессора,Формирователь 39 адреса микрокоманд предназначен для формированияадресов.микрокоманд,.считывания поним микрокоманд из блока 40 памятимикрокоманд.Блок 40 памяти микрокоманд предназначен для хранения микрокоманд об- З(работки информации процессором и микрокоманд, входящих в микропрограммуобработки отказа и выдачи их в формирователь 41 микроопераций по адресу, поступающему из Формирователя 39адреса микрокоманд.Формирователь 41 микрооперацийпредназначен для формирования микроопераций, по которым осуществляетсяобработка информации, для формирования адреса следующей микрокоманды, ффдля запуска блока 31 памяти эталонов.Назначение основных Функциональных элементов блока локальной памяти(Фиг.2) состоит в следующем. Кодопреобраэователь, состоящий из .последовательно соединенных дешифратора 48и шифратора 49, преобразует поступающие на второй вход 55 блока локальной памяти коды микроопераций в управляющие сигналы, которые поступа- Яют на управляющие входы групп элементов И блоков 50 элементов 2 И-ИЛИ иблоков 52 элементов И,Преобразование кодов микроопера.ций в коды управляющих сигналов осуществляется следующим образом.Код микроопераций преобразовывается дешифратором 48 в десятичный позиционный код, На одном из выходов дешифратора появляется единичный сигнал.ф По этому сигналу шифратор 49 формирует код управляющих сигналов, по которым выполняются операции в данном блоке. Преобразователь кодов, состоящий из дешифратора 48 и шифратора 49, И может быть выполнен в виде программируемой логической матрицы.и групп 50 элементов 2 И-ИЛИ предназначены для передачи информациипервого 54, третьего 56 входа блока5 ( 6 ) локальной памяти в соответствующий и -й регистр 51.й регистров 51 .предназначены дляхранения информации и выдачи ее черезсоответствующие группу 52 элементовИ и выход блока 5 ( 6 ) локальной памяти.Блок 5 (6 ) локальной памяти Функционирует следующим образом.По очередному коду микрооперацииоткрываются по второму входу первыегруппы элементов И или по первомувходу - вторые группы элементов И(-го блока 5, элементов 2 И-ИЛИ, черезкоторые информация, поступившая напервый 54 или третий 56 входы блока5 (,6 ) локальной памяти, записываетсяв сбответствующий (-й регистр 51 ихранится в нем,При необходимости выдачи информации из 1-го регистра 51 на выход 53блока 5 локальной памяти, соответст,вующуюгруппу 52 элементов И открывают по второму входу сигналоммикрооперации и информация из регистра 51 через соответствующую группу52 элементов И поступает на выход 53блока 5 (6 ) локальной памяти.Назначение функциональных элементов блока 7 основной памяти (фиг.3)состоит в следующем.Накопитель 62 информации предназначен для хранения данных и,команд поих обработке. Первый 63 и второй 64элементы И предназначены для Формирования сигналов считывания и записи информации на четвертый и третийвходы накопителя 62 соответственнопо адресу, поступающему на первыйвход 57 блока 7 основной памяти.Блок элементов И предназначен длявыдачи по сигналам микроопераций,поступающим на его второй вход, инФормация со второго 58 входа блокаосновной памяти 7 на второй вход накопителя 62,Триггер 65 предназначен для выдачи сигнала блокировки по первому входу первого 63 и второго 64 элементовИ при возникновении отказа в одном изканалов обработки информации в процессоре и снятия сигнала блокировкипри восстановлении отказа.Блок 7 основной памяти функционирует следующим образом.Режим записи информации, Обработанная информация с выхода буферного регистра 26 поступает на второйвход 58 блока 7 основной памяти.Код микроопераций записи информации поступает через четвертый вход60 блока 7 основной памяти, открыва10 3 Режим блокировки записи и считывания информации. При отказе одного иэ каналов обработки информации сигнал с выхода одновибратора 25 поступает на третий вход 59 блока 7 основной памяти и устанавливает триггер 65 в нулевое состояние. При этом сигнал на единичном выходе триггера 65 исчезает, закрывая по первому входу первый 63 и второй 64 элементы И, запрещая таким образом выдачу в накопитель 62 импульсов записи и считывания. 35При восстановлении отказавшего канала обработки информации сигнал микрооперации с четвертого входа 60 блока 7 основной памяти поступает на единичный вход триггера 65. При этом 40 триггер 65 устанавливается в единичное состояние, открывая по первому входу первый 63 и второй 64 элементы И.Назначение основных функциональных 45 элементов формирователя 41 микроопе- раций (фиг.4) состоит в следующем.Регистр 70 предназначен для хранения адресных и операционных частей микрокоманд и выдачи их на первый 73 выход и на входы дешифратора 72 формирователя 41 микроопераций соответственно.Дешифраторы 71 предназначены для формирования операционной части микрокоманд по коду, поступающему. с регистра 70 кодов микроопераций, и выдачи их на третий выход 74 формирователя 41 микроопераций.Дешифратор 72 предназначен для формирования адреса первой эталонной 60 комбинации блока 31 памяти и. выдачи его на второй выход 74 формирователя 41 микроопераций.Формирователь 41 микроопераций функционирует следующим образом. 65 ет по второму входу блок 61 элементов И и по третьему входу - второй . элемент И 64. При нахождении триггера 65 в нулевом состоянии сигнал через второй вход второго элемента И.64 поступает на третий вход накопителя 62 и по адресу, поступающему на первый вход накопителя 62 с первого входа 57 блока 7 основной памяти эаписывает информацию с выхода блока элементов И 64 в накопитель 62.2. Режим считывания информации. Код микрооперации считывания информации через четвертый вход 60 поступает на третий вход первого элемента И 63. Сигнал с генератора импуль сов считывания через второй вход первого элемента И 63 поступает на четвертый вход накопителя 62 и по адресу, поступающему на первый вход накопителя 62 с первого входа 57 20 блока 7 основной памяти, производит считывание следующей команды и подает ее на выход 66 блока 7. Иикрокоманда поступает с входа 69 формирователя микроопераций на регистр 70. Адрес следующей микрокоман- ды с первого выхода регистра 70 поступает на первый выход 73 формирователя 41 микроопераций, а операционная часть микрокоманды поступает на входы дешифраторов 71 и 72. В л дешифраторах 71 формируются коды микрооперации, которые поступают на третий выход 75 Формирователя 41 микроопераций, В дешифраторе 72 формируется адрес первой эталонной комбинации блока 31 памяти эталонов, который поступает на второй выход 74 формирователя 41 микроопераций.Назначение основных функциональных элементов операционных блоков (фиг.5) состоит в следующем.Дешифратор 79 и шифратор 80 преобразовывают поступающие на второй 77 вход операционного блока коды микро- операций в коды управляющих сигналов (также как и в блоках локальной пагляти) и подают их на вторые (первые) входы первой и второй групп элементов И группы 81 элементов 2 И-ИЛИ и вторые (первые) входы первой 84 и второй 85 групп элементов И соответственно.Группа 81 элементов 2 И-ИЛИ предназначена для передачи информации, поступающей с выхода регистра 83 или с первого входа 6 операционных блоков 14 на вход (первый вход) сумматора 82 соответственно, в зависимости от кода управляющих сигналов.Сумматор 82 предназначен для обработки информации и выдачи ее на информационный вход регистра 83, а так" же (только для сумматора блока 12) выдачи сигнала переноса на третий выход первого операционного блока 12,Регистр 83 предназначен для промежуточного хранения информации. Первая 84 и вторая 85 группы элементов И предназначены для передачи информации с регистра 83 на второй 87 и первый 86 выходы операционного блока соответственно. Операционный блок 14 функционирует следующим образом.По кодам микроопераций формируется код управляющих сигналов, по которому открывается первая группа элементов И группы 81 элементов 2 И-ИЛИ и информация с первого входа 76 операционного блока 14 через группу 81 элементов 2 И-ИЛИ Поступает на вход сумматора 82, где осуществляется обработка информации.Далее управляющим сигналом, поступающим на вход синхронизации регистра 83, информация с сумматора 82 перезаписывается в регистр 83. Затем в зависимости от кода управляющих сигналов информация с регистра 83 по

СмотретьЗаявка

3287646, 12.05.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, перестраиваемый, процессор

Опубликовано: 23.12.1982

Код ссылки

<a href="https://patents.su/19-983713-perestraivaemyjj-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Перестраиваемый микропрограммный процессор</a>

Предыдущий патент: Устройство для контроля хода программ

Следующий патент: Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе

Случайный патент: Экстрактор для системы твердое тело жидкость