Модуль интегрирующей вычислительной структуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1101821

Автор: Криворучко

Текст

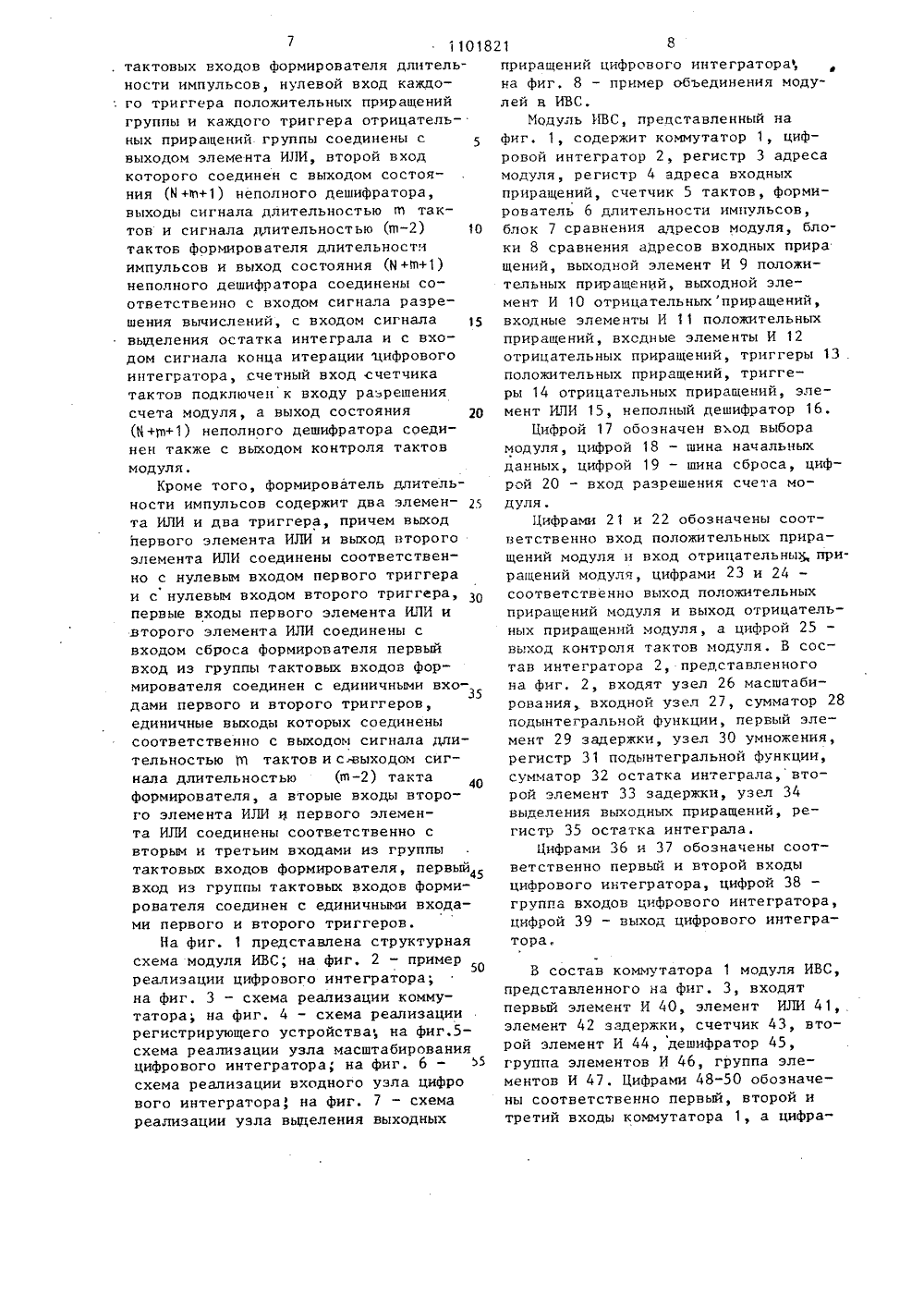

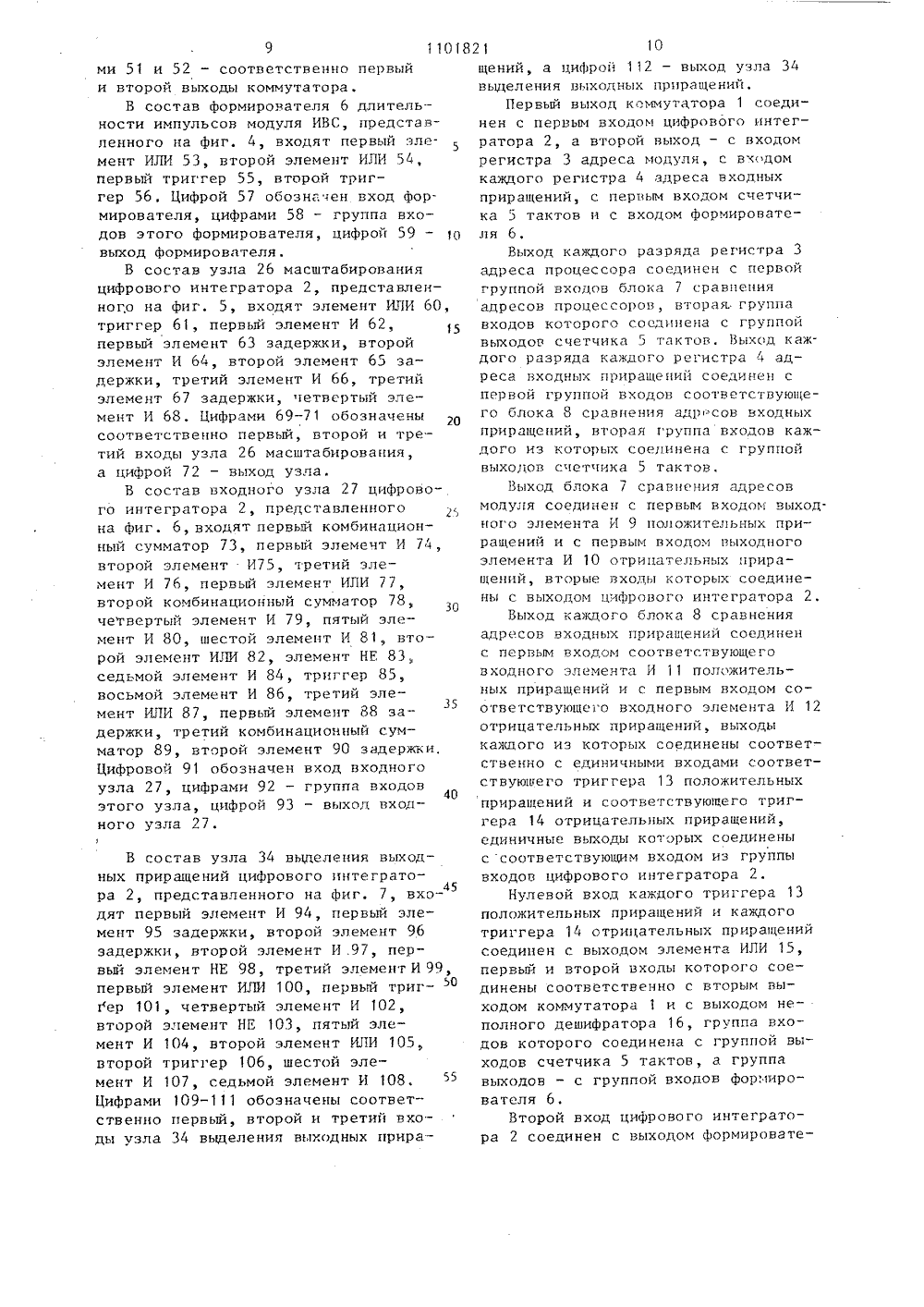

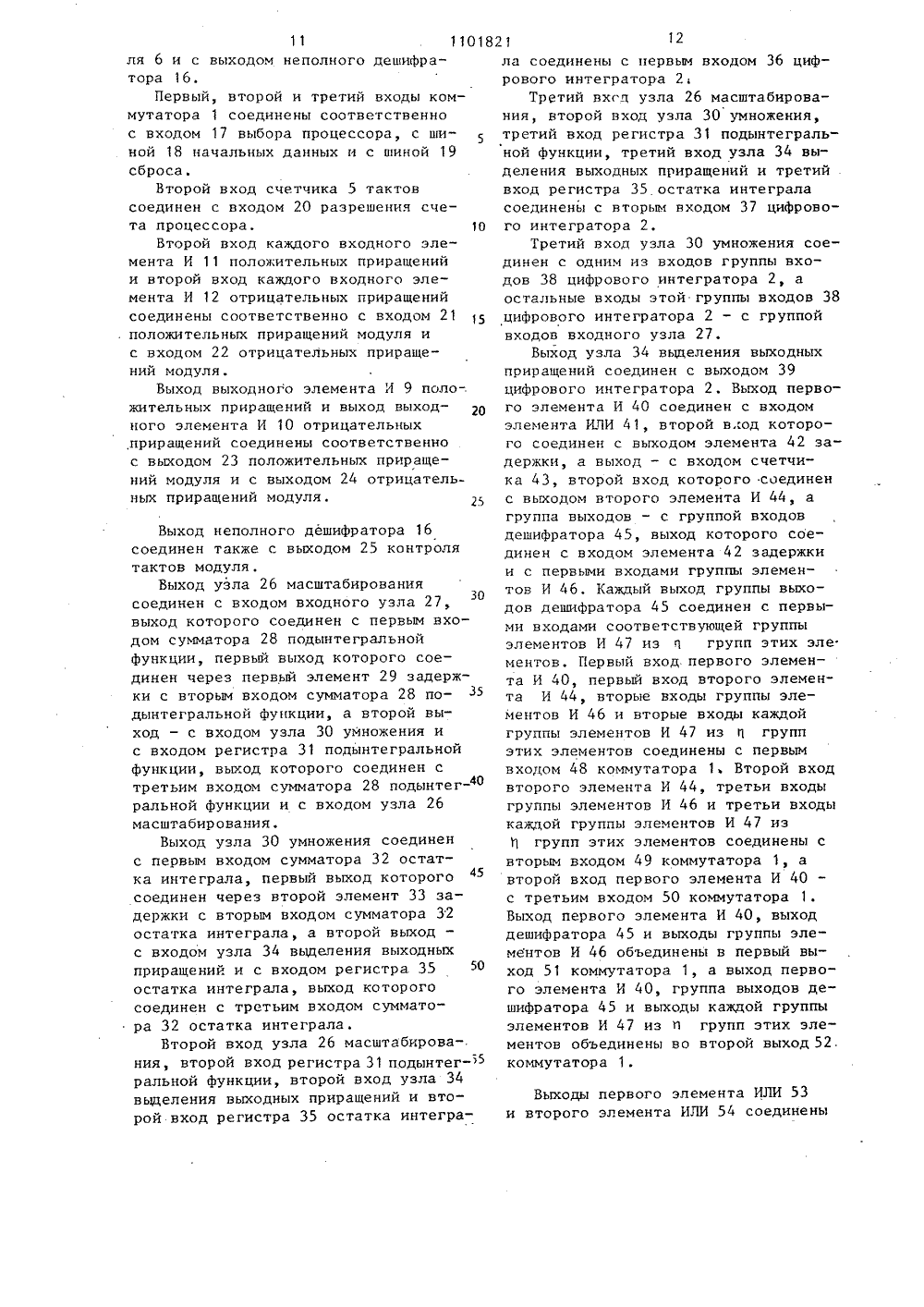

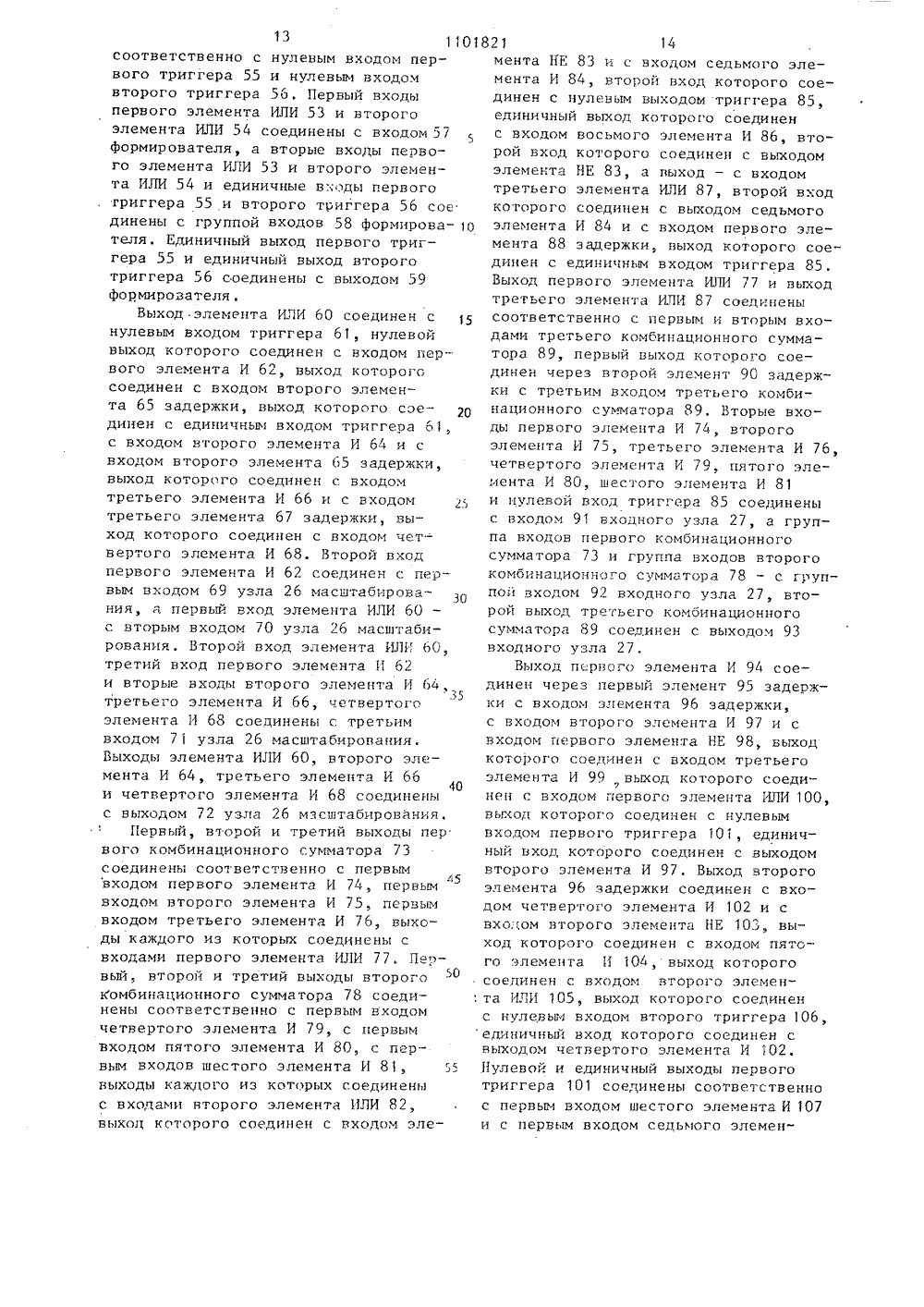

10 соединены с соответствующий входомданного модуля.Последний импульс сопровожденияданных перебросит счетчик 43 в последнее состояние по которому напоследнем выходе дешифратора 45 появится единичный сигнал, которыйразрешит прохождение начальных дан,ных через группу элементов И 46 и "выход 51 коммутатора 1 в цифровойинтегратор 2 через первый вход 36его на входы параллельной записи регистра 31 подынтегральной функции, и одновременно этот единичный сигнал с последнего выхода дешифратора 4515 поступит через выход 51 коммутатора 1 и через вход Зб цифрового интегратора 2 на вход разрешения за - писи этого регистра 31, и в результате в регистр 3 1 запишется соответ 20 ствующее данному модулю начальное значение подынтегральной функции. Кроме того, единичный сигнал с последнего выхода дешифратора 45 поступит на вход элемента 4 2 задержки и, задерживаясь на один такт на этом элементе 42 задержки, поступит через элемент ИЛИ 4 1 и сбросит счет - чик 43 в нулевое состояние. На этом ввод начальных данных заканчивается,30Модуль ИВС оперирует с одноразрядными приращениями, представленными в тернарной системе кодирования, т.е. имеющими три значения: "+1", "0" и "-1", поэтому обмен прираще - ниями между модулями осуществляется по двум каналам - положительному и отрицательному. Выходные элементы И 9 и 10 выполняются по схеме с открытым коллектором, что позволяет простым объединением их выводов реа 40 лизовать функцию МОНТАЖНОЕ ИЛИ, Схема соединения модулей между собой представлена на фиг. 8, на которой два выхода у каждого модуля - выход 23 положительных приращений и выход 24 отрицательных приращений, а два входа - вход 21 положительных приращений и вход 22 отрицательных приращений модуля (на фиг. 8 показаны лишь входы и выходы, обеспечиваю-. 50 щйе связь модулей между собой, а все остальные входы, обеспечивающие связь модулей с другими устройствами ИВС, опущены). Как видно из фиг. 8, выход положительных прираще ний каждого модуля через МОНТАЖНОЕ ИЛИ соединен с входом положительных приращений каждого процессора,а выход отрицательных приращений каждого процессора через МОНТАЖНОЕ ИЛИ соединен с входам отрицательных приращений каждого модуля.Модуль ИВС работает следующим образом.По сигналу, разрешающему решение, в модуль через вход 20 на вход счетчика 5 тактов начинают поступать из центрального устройства управления ИВС импульсные сигналы, которые в каждой итерации последовательно изменяют состояние счетчика 5 от 1 до Й +В+1), где К - количество модулей в ИВС, П 1 - количество разрядов в регистре падынтегральной функции модуля, При этом процесс решения на каждой итерации разбивается на два этапа: этап передачи приращений и этап вычислений, Причем этап передачи приращений происходит за первые 1 тактов, т.е. когда счетчик изменяет свое состояние от 1 до 1 а этап вычислений выполняется за т тактов, когда счетчик изменяет свое состояние от Ч до (Й +Ф), и (В +в+1) - й такт используется для подготовки модуля к следующей интерации. Тогда при поступлении на вход 20 импульсных сигналов последовательно изменяемые в каждом такте значения счетчика 5начнут поступать в качестве адресов модуля от 1 до Ч с единичных выходов каждого разряда этого счетчика параллельным кодом на входы блокасравнения и на входы блоков 8 сравнения, При совпадении адреса, пришедшего с выходов счетчика 5 на входы блока 7 сравнения, с адресом модуля, записанным в регистр З,блок 7 сравнения выдает разрешающий сигнал на входы элементов И 9 и 10, обеспечив тем самым прохождение одноразрядных приращений интеграла с выхода 39 цифрового интегратора 2 через элементы И 9 и 10 и через МОНТАЖНОЕ ИЛИ на входы 21 и 22 всех модулей ИВС,При совпадении же адреса, поступающего с выходов счетчика 5, с адресом, записанным в регистр 4, соответствующий узел 8 сравнения выдает разрешающий сигнал на входы соответствующих элементов И 11 и 12, и одноразрядные приращения интеграла, пос тупившие в этот момент времени на входы 21 и 22 всех модулей это будут одноразрядные приращения интеграла с выходов 23 и 24 того модуля, кото 19 1101рые по структурной схеме решения задачи соединен с данным входом данногомодуля и, следовательно, адрес которого записан в соответствующем регистре 4 данного модуля), пройдут5через соответствующие элементы И 11и 12 и запишутся в соответствующихтриггерах 13 и 14, Через М тактовсчетчик 5 установится в состояние,равное М , и произойдет переадресса- Оция приращений последнего И -го модуля ИВС. На этом этап передачи приращений закончится, и в следующем так.те счетчик 5.перейдет в состояние,равное М +1, и на соответствующем 5выходе дешифратора 1 б появится единичный сигнал, который поступит черезсоответствующий вход из группы входов 58 формирователя 6 на единичньевходы триггеров .55 и 56 и перебросит 20их в единичное состояние,В результате триггер 55 начнетвырабатывать единичный сигнал длительностью (а) такта, который поступит с единичного выхода триггера 5525через выход 59 блока 6 в цифровойинтегратор 2 через второй вход 37на вход управления сдвигом регистра 35остатка интеграла, Так как процессороперирует с одноразрядными приращениЗОями, то в соответствии с алгоритмомего работы квантование неквантованного приращения интеграла производитсяследующим образом: квантованные одноразрядные приращения выделяются взнаковых разрядах п -разрядного модифицированного кода неквантованногоприращения интеграла, а оставшиесячисловые разряды этого кода без знаковых разрядов выделяются в качестве остатка интеграла, поэтому ре 40гистр 35 остатка интеграла имеет(ц 1-2) разряда, и сигнал управлениясдвигом имеет длительность (п 1-2)такта,45На единичном выходе триггера 56 одновременно начнет вырабатываться сигнал, разрешающий вычисления, длительностью й тактовкоторый поступит через выход 59 формирователя 6 и через вход 37 в цифровой интегратор 2 на вход управления сдвигом регистра 31 подынтегральной функции, на вход узла 30 умножения, в узел 26 масштабирования через третий 55 его вход 71 на третий вход элемента И 62 и на вторые входы элементов И 64, 66 и 68, а также в узел 34 20821выделения выходных приращений черезтретий его вход 111, на второй входэлемента И 94 и разрешит выполнениев этом цифровом интеграторе 2 операции численного интегрирования. Начнется этап вычислений длительностьюй тактов (счетчик 5 в это времяизменяет свое состояние от (Я+1)до (К +М, в течение которого значение подынтегральной функции, представленное в модифицированном дополнительном двоичном коде, будет поступать с выхода регистра 31 младшими разрядами вперед на вход сумматора 28 и на первый вход 69 узла 26масштабирования.В результате первая же единицав коде подынтегральной функции, являющаяся начальным импульсом, положение которогб зависит от масштабапредставления величин, поступитв узел 26 масштабирования черезвход 69, через открытый элемент И 62и, задержавшись на один такт наэлементе 63 задержки, переброситтриггер 61 в единичное состояние,закрыв тем самым элемент И 62, иодновременно поступит через открытыйэлемент И 64 (на второй вход этогоэлемента, также как и на второй входэлементов И бб, 68 и третий входэлемента И 62 поступает через вход1из блока 6 сигнал, разрешающий вычисления) и через выход 72 во входной узел 27 в качестве первого масштабного импульса, соответствующегокванту подынтегральной функции, т,е.последнему младшему разряду,Кроме того, задержавшись на одинтакт на элементе 65 задержки, этот сигнал поступит в качестве второго масшт; бного импульса, соответствующего предпоследнему разряду подынтегральной функции, через открытый элемент И 66 и через выход 72 тоже во входной узел 27, а задержавшись еще на один такт на элементе 67 задержки, этот сигнап поступит уже в качестве третьего масштабного импульса через открытый элемент И 68 и через выход 72 во входной узел 27. Одновременно одноразрядные приращения, представленные в тернарной системе кодирования, поступят с выходов триггеров 13 положительных приращений и триггеров 14 отрицательнь 1 х приращений в виде потенциалов, соответствующих "+1" или "-1", через группу входов 3821О 1цифрового интегратора 2 и через группу входов 92 входного узла 27 навходы соответственно комбинационногосумматора 73 и комбинационного сумматора 78. Причем в комбинационномсумматоре 73 происходит суммированиеположительных приращений, а в комбинационном сумматоре 78 - отрицательных приращений.Получившиеся суммы положительных 10приращений и отрицательных приращений поступают соответственно с выходов сумматора 73 и выходов сумматора 78 параллельным трехразряднымкодом (число разрядов в этих кодах,равное числу выходов из этих сумматоров, не превышает трех так какчисло одновременно суммируемых приращений подынтегральной функции, а следовательно, и число входов входногоузла, т,е. число входов по подынтегральной функции цифрового интегратора, не превышает семи и на практикеравно обычно 3.-5) на первые входысоответственно элементов И 74-76 иэлементов И 79 - 81, на вторые входыкоторых поступают с выхода 72 узла 26 масштабирования через вход 91входного узла 27 первыи, второйи третий масштабные имгульсы в соответствии с весом разряда параллельного трехразрядного кода суммы приращений. Причем первый масштабныйимпульс, соответствующий кванту подынтегральной функции т.е. последнему, младшему разряду, поступает навторые входы элементов И 74 и 79,на первые входы которых поступаютмладшие разряды трехразрядных параллельных кодов соответственно суммыположительных приращений и суммыотрицательных приращений, второймасштабный импульс, соответствующийпредпоследнему разряду подынтегральной функции, поступает на вторыевходы элементов И 75 и 80, на первыевходы которых поступают средние раз.ряды трехразрядных параллельных кодовсоответственно суммы положительныхприращений и суммы отрицательных приОращений, а третий масштабный импульс,так же как и старшие разряды трехразрядных параллельных кодов сумм приращений поступают на входы элементов И 76 и 81,В результате масштабные импульсы, вырабатываемые узлом 26 масштабирования, приводят суммы положительных 821 22и Отрицательных приращений к масштабу подынтегральной функции данногомодуля и переводят их из параллельного двоичного кода в последовательный. При этом количество масштабныхсигналов, вырабатываемых узлом 26,зависит так же, как и количествовьжодов у сумматоров 73 и 78, отчисла одновременно суммируемых приращений подынтегральной функции и практически не превышает трех, так какмаксимальное число одновременно суммируемых приращений подынтегральнойфункции как теоретически так и практически не превышает семи,Последовательный код суммы положительных приращений, приведенныйк масштабу подынтегральной функцииданного модуля, с выхода элемента ИЛИ 77 поступает на первый входкомбинационного сумматора 89, а последовательный код суммы отрицательных приращений, поступающий с выходаэлемента ИЛИ 82, сначала преобразуется в дополнительный код, а потомуже с выхода элемента ИЛИ 87 поступает на второй вход сумматора 89. Образование дополнительного кодасуммы отрицательных приращений производится следующим образом. Первая единица в последовательном коде суммы отрицательных приращений, поступающая с выхода элемента ИЛИ 82, пройдет через открытый элемент И 84 (на второй вход этого элемента поступает единичный сигнал с нулевого выхода триггера 85, так как этот триггер был установлен в нулевоесостояние при подготовке к решенщо сигналом сброса) и поступит без изменения через элемент ИЛИ 87 на второй вход сумматора 89, а задержавшись на один такт на элементе 88 задержки, эта единица поступит на единичный вход триггера 85 и переброситего в единичное состояние.В результате триггер 85 закроет элемент И 84 и откроет элемент И 86, и весь оставшийся последовательный код суммы отрицательных приращений, проинвертировавшись на элементе ИЕ 83, поступит в инверсном виде через открытый элемент И 86 и элемент ИЛИ 87 на второй вход сумматора 89, Образованный таким образом дополнительный код суммы отрицательных приращений, поступающии с выхода элемента ИЛИ 87, просуммируется на23 11018 сумматоре 89 с суммой положительных приращений, поступающей с выхода элемента ИЛИ 77, и общая сумма приращений подынтегральной функции поступич с выхода сумматора 89 на выход 93 входного узла 27.В цепь переноса сумматора 89 вклю-. чен однотактный элемент 90 задержки, служащий для образования поразрядного переноса при суммировании суммы положительных приращений с суммой отрицательных приращений. Полученная общая сумма входных приращений подынтегральной функции поступит с выхода 93 входного узла 27 на вход сумматора 28, на другой вход которого поступает из регистра 31 значение подынтегральной функции. В цепь переноса этого сумматора 28 включен однотактный элемент 29 задержки, служащийО для образования переноса при сложении общей суммы входных приращений подынтегральной функции с текущим значением подынтегральной функции.Получающееся в результате сумми рования на сумматоре 28 новое значение подынтегральной функции поступит в регистр 31 и на вход узла 30 умножения, где произойдет умножение это го значения подынтегральной функции ЗО на приращение переменной интегрирования, поступающее:на другой вход узла 30 умножения с выхода соответствующего триггера 13 или 14 через соответствующий вход 38 цифрового интегратора 2. Результат умножения поступит на вход сумматора 32 остатка интеграла, на другой вход которого поступает значение остатка интеграла из регистра 35. В цепь переноса 40 сумматора 32 включен элемент 33 задержки, служащий для образования переноса при сложении результата умножения с текущим значением остатка интеграла. 45Полученное в результате суммирования на сумматоре 32 значение неквантованного приращения интеграла поступает на вход узла 34, где происходит выделение нового значения квантованного приращения интеграла, и в регистр 35, в который записывается выделяемый новый остаток интеграла, представляющий собой в соответствии с алгоритмом работы с одноразрядными 55 приращениями значение неквантованного приращения интеграла без знаковых разрядов, а знаковые разряды опреде 2421ляют значение квантованного приращения интеграла. Причем выделение нового значения остатка интеграла производится, как уже отмечалось, использованием укороченного регистра, имеющего (щ) разряда, и подачей из формирователя 6 с выхода триггера 55(п 1-2)-х тактного сигнала управлениясдвигом,по которому в регистр 35запишутся лишь числовые разряды беззнаковых, и по (й +в+1)-му такту дешифратор 16 выдаст через соответствующий вход из группы входов 58 ичерез элемент ИЛИ 53 на нулевойвход триггера 55 единичный сигнал,по которому триггер 55 формирователя 6 перейдет в нулевое состояние,и сдвиг информации в регистре 35прекратится, Оставшиеся знаковые разряды, которые определяют значениеквантованного приращения интеграла,анализируются в узле 34,Выполняется это следующим образом. Значение неквантованного приращения интеграла, поступающие с выхода сумматора 32, пройдет через вход 109 узла 34 и постучит на вход элемента И 94. А так как на второй вход этого элемента И 94 поступает через вход 111 из формирователя 6 сигнал, разрешающий вычисления, то это значение неквантованного приращения интеграла .;ройдет через элемент И 94 и поступит на вход элемента 95 задержки, задерживается на этом элементе задержки на такт (эта задержка выполняется для того, чтобы первый (старший) знаковый разряд совпал по времени с сигналом подготовки модуля к следующей итерации, появляющимся на выходе дешифратора 16 по окончании этапа вычислений в (И+В+1)-м такте) и поступает на вход элемента И 97 и через элемент НЕ 98 на вход элемента И 99, а задержавшись еще на один такт на элементе 96 задержки (эта задержка выполняется для того, чтобы и второй (младший) знаковый разряд, следующий на такт раньше первого (старшего) знакового разряда, совпал по времени с сигналом подготовки процес сора к следующей итерации, появляющимся на выходе дешифратора 16, как уже отмечалось, по окончанию этапа вычислений в (8+щ+1)-м такте с целью обеспечения возможности одновременного анализа обоих знаковых разря,цов), поступает на вход элемента И 102 и через элемент НЕ 103 навход элемента И 104. А на вторыевходы элементов И 97, 99, 102 и 104поступает по окончании этапа вычис 5лений в (И+В+1)-м такте с выхода дешифратора 16 через вход 37 цифрового интегратора 2 и через вход 111узла 34 сигнал подготовки модуляк следующей интерации, так как счет Очик 5 установится в этом такте тоже в состояние, равное (11+оп+1), ив результате по этому сигналу триггеры 101 и 106 устанавливаются в состояния,.соответствующие соответственно старшему и младшему знаковым разрядам, т.е. триггер 101 будет анализировать знак, а триггер 106 - переполнение знакового разряда.Поскольку квантованные приращения интеграла являются одноразрядными и представляются в тернарной системе кодирования, то кодирование приращений осуществляется следующим образом; 01 Т +11 1100 ОУ 25 т,е. если по сигналу подготовки моду - ля к следующей итерации, появляющегося на выходе дешифратора 16 по окончании этапа вычислений в Й +п+1) -м такте, триггер 101 устанавливается в нулевое состояние, а триггер 106 в единичное, то на выходе элемента И 107 появится единичный сигнал длительностью одной итерации,соответствующий положительному приращению интеграла "+1", который через вы - ход 112 узла 34 и через выход 39 цифрового интегратора 2 поступит на вход элемента И 9 положительных приращений; если же по сигналу подготов -40 ки модуля к следующей интерации в (11+я+1)-м такте в единичное состояние устанавливаются оба триггера 101 и 106, то единичный сигнал длительностью одной итерации, соответствую 45 щей отрицательному приращению интеграла "-1", появится на выходе элемента И 108 и поступит через выход 112 узла 34 и через выход 39 цифрового интегратора 2 на вход элемента И 105 ц отрицательных. приращении .Если же оба триггера 101 и 106 окажутся в нулевом состоянии, то приращения на выход 112 узла 34 выдаваться не будут, что соответствует 55 значению приращения интеграла, равного "0". Одновременно в 5+ш+1) -м такте из дешифратора 16 в блок 6 че 821 26рез соответствующий вход из группы входов 58 и через элемент ИЛИ 54 на нулевои вход триггера 56, вырабатываю щего сигнал разрешения вычислений, поступит единичный сигнал, который перебросит этот триггер 56 блока 6 в нулевое состояние, прекращая тем самым подачу сигнала разрешения вычислений на вход 37 цифрового интегратора и завершая этап вычислений длительностью п тактов, Кроме того, появившийся в (8+в+1)-м такте, используемом для подготовки модуля к следующей итерации, на выходе дешифратора 16 вследствие того, что счетчик 5 устанавливается в состояние, равное (,1+В+1), сигнал установки в исходное состояние поступит с выхода дешифратора 16 через элемент ИЛИ 15 на нулевые входы триггеров 13 и 14, подготавливая их к этапу передачи приращений в следующей итерации. Далее этот сигнал поступит через вход 37 цифрового интегратора 2 в узел 26 масштабирования через третий его вход 71 и через элемент ИЛИ 60 на нулевой вход триггера 61, устанавливая его в нулевое состояние, и с выхода элемента ИЛИ 60 этот сигнал поступит через выход 72 узла 26 ичерез вход 91 узла 27 на нулевой вход триггера 85, устанавливая его в нулевое состояние и подготавливая тем самым узел 26 и узел 27 к этапу вычислений в следующей итерации,Одновременно этот сигнал с выхода дешифратора 16, соответствующий состоянию счетчика 5, равному Р +а+1) поступит через выход 25 модуля в центральное устройство управления ИВС и в случае совпадения этих сигналов, поступающих в центральное устройство управления ИВС с входов 25 всех модулей ИВС, свидетельствующем об отсутствиисбоев в процессе счета на первой итерации, центральное устройство управления ИВС продолжит выдавать импульсные сигналы на входы 20 всех модулей ИВС уже для следующей итерации. И первый же импульсный сигнал в первом такте следующей итерации перебросит счетчик 5 из состояния (Я +Э+1) в состояние, равное единице (счетчик 5 является счетчиком по модулю (я+3+1), и. начнется вторая итерация, в течение которой затактов произойдет переадресация приращений и за й тактоввыполнится операция численного интегрирования, а в (4+в+1) - й тактпроизойдет подготовка. модуля к следующей интерации, а также контрольпроцесса счета центральным устройством управления ИВС, и в случае отсутствия сбоев в процессе счетацентральное устройство управления ИВСпродожит выдавать импульсные сигналына вход 20, и в следующемтакте счетчик 5 перейдет изсостояния (М + в+1) в состояние,равное единице, и начнется новаяитерация и т,д,В случае же если при контроле процесса счета в (И+в+1)-м такте какой-либо итерации центральным устройством управления ИВС будет обнаружено отсутствие в этом такте сигнала с выхода 25 хотя бы одного модуля ИВС, что свидетельствует о наличии сбоя в процессе счета, центральное устройство управления ИВС прекратит выдавать импульсные сигналы на вхо"ды 20 модуля, и процесс решения будет остановлен.Таким образом, предлагаемый модуль ИВС наряду с выполнением функции численного интегрирования обеспечивает возможность универсальнойкоммутации, т.е, любой вход любогомодуля может быть соединен с любым 10 выходом любого модуля, задав соответствующий адрес в регистр адресавходных приращений. В то же времяв сравнении с известным модулем ИВСзатраты оборудования на предлагаемыймодуль с учетом реализации его насовременных комплексах микросхем непревышает затраты на известный модуль, что позволяет создавать на егооснове ИВС такой же вычислительноймощности, что и известный модуль, нообеспечение универсальности коммутации при этом значительно упроститпрограммирование задачи и сократитвремя подготовки задачи к решению1101821 Составитель А.Чекановактор В.Данко Техред А.Бабинец Корректор О,Тигор П исно СССР крытиикая наб Филиал ППП "Патент", г.ужгород, ул.Проектная аказ 4769/33 ВНИИПИ по 11303Тираж 699 Государственного коми елам изобретений и от Москва, Ж, Раушсгеров. 11 О 1 выход соединен с первым входом выход - ного элемента И положительных приращений и с первым входом выходного элемента И отрицательных приращений, вторые входы которых соединены соответственно с выходами положительного и отрицательного приращения интеграла цифрового интегратора, а выхоцы - с выходами положительных и отрицательных приращений процессора соответственно, единичный выход каждого разряда 1 -го регистра адреса входных приращений группы со динен с первой группой входов 1 -го блока сравнения адресов входных приращений группы, вторая группа входов которого соединена с группой единичных выходов счетчика тактов, а выход 1 -го блока сравнения адресов входных приращений группы соединен с первым входом-го входного элемента И положительных приращений группы и с первым входом 1 -го входного элемента И отрицательных приращений группы, вторйе входы которых соединены соответственно с входом положительных приращений модуля и с входом отрицательных приращений модуля, а выходы соединены соответственно с единичным входом-го триггера положительных приращений группы и с единичным входом 1 -го триггера отрицательных приращений группы, единичные выходы которых соединены соответственно с -ми входами из групп входов положительных и отрицательных значений входных приращений цифрового интегратора, группа входов неполного дешифратора соединена с группой единичных выходов счетчика тактов, выходы состояния Р +1) (где М - количество модулей в интегрирующей вычислительной структуре), состояния (11 + Гп -1) и состояния (В+а+1) неполного дешифратора (где Ф - количество разрядов в регистре подынтегральной функции цифрового интегратора) соедине,ны соответственно с первым, вторым и третьим входами группы тактовых Изобретецие относится к вычислительной технике и предназначено для 821входов формирователя длительности импульсов, нулевой вход каждого триггера положительных приращений группы и каждого триггера отрицательных приращений группы соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом состояния (Ч +П+1) неполного дешифратора, выходы сигнала длительностью Ф тактов и сигнала длительностью (ъ - 2) тактов формирователя длительности импульсов и выход состояния (Ч+щ+1) неполного дешифратора соединены соответственно с входом сигнала разрешения вычислений, с входом сигнала выделения остатка интеграла и с входом сигнала конца итерации цифрового интегратора, счетный вход счетчика тактов подключен к входу разрешения счета модуля, а выход состояния (11+1+1) неполного дешифратора соединен также с выходом контроля тактов модуля.2, Модуль по и. 1, о т л и ч а ющ и й с я тем что формирователь длительности импульсов содержит два элемента ИЛИ и два триггера причем выход первого элемента ИЛИ и выход второго элемента ИЛИ соединены соответственно с нулевым гходом первого триггера и с нулевым входом второго триггера, первые входы первого элемента ИЛИ и второго элемента ИЛИ соединены с входом сброса формирователя, первый вход из группы тактовых входов формирователя соединен с единичными входами первого и второго триггеров, единичные выходы которых соединены соответственно с выходом сигнала длительностью Гп тактов и с выходом сигнала длительностью (в) такта формирователя, вторые входы второго элемента ИЛИ и первого элемента ИЛИ соединены соответственно с вторым и третьим входами из группы тактовых входов формирователя, первый вход из группы тактовых входов формирователя соединен с единичными входами первого и второго триг 1 использования в итегрирующих вычислительных структурах (ИВС), 11013Известны цифр овые инте гр аторы, содержащие регистры и сумматоры подынтегральной функции, регистры и сумматоры остатка интеграла, узлы умножения, узлы выделения приращений и предназначенные для использования в ИВС 1 .и 2 .Основным недостатком этих цифровых интеграторов является то, что они не могут выполнять функцию програм мируемого коммутатора, вследствие чего нельзя строить на их основе экономичные ИВС большой вычислительной мощности, в то же время ИВС аналогичной мощности, построенные на основе этих цифровых интеграторов, из - за больших затрат оборудования на их коммутацию очень неэкономичны и даже не всегда практически реализуемы.Наиболее близким по технической20 сущности к изобретению является про. цессор ИВС с одноразрядными приращениями,содержащий коммутатор,регистр настройки, узел входных коммутаторов25 узел выходных коммутаторов и цифровой интегратор, включающий регистр и сумматор подынтегральной функции, регистр и сумматор остатка интеграла, узел умножения, узел выделения выходных приращений, первый и второй узлы масштабирования, причем первый и второй выходы коммутатора соединены соответственно с входом регистра настройки и входом первого узла масштабирования цифрового интегратора, З 5 а входы коммутатора соединены с ши:ной выбора процессора, шиной начальных данных и шиной сброса, выходы регистра настройки соединены соответственно с входом узла входных комму О таторов и первым входом узла выходных коммутаторов, второй вход которого подключен к выходу узла выделения выходных приращений цифрового интегратора, группа входов узла входных коммутаторов соединена с четырьмя шинами входных приращений, а выходы подключены соответствено к входам второго узла масштабирования и узла умножения цифрового интегратора, группа входов узла выходных коммутаторов соединена с четырьмя шинами входных приращений, а группа выходовс четырьмя шинами выходных приращений, выход второго узла масштабиро вания цифрового интегратора соединен с первым входом сумматора подынтегральной функции цифрового интеграто 821 4ра, второй вход которого подключен к выходу регистра подынтегральной функцуи цифрового интегратора, а выход сумматора подынтегральной функции цифрового интегратора соединен с первыми входами регистра подынтегральной функции и узла умножения цифрового интегратора, выход узла умноженияцифрового интегратора подключен кпервому входу сумматора остатка интеграла цифрового интегратора, выход которого соединен с входом узла выделения выходных приращений цифрового интегратора непосредственно и через регистр остатка интеграла цифрового интегратора с вторым входом сумматора остатка интеграла, первый и второй выходы первого узла масштабирования цифрового интегратора соединены соответственно с входами второго узла масштабирования и регистра подынтегральной функции цифрового интегратора.Известный процессор ИВС наряду с выполнением основной задачи - численного интегрирования одновременно может выполнять задачи программируемого коммутатора, что позволяет соз -давать на его основе экономичныеплоские ИВС большой вычислительной мощности 3.Основным недостатком известного процессора ИВС являются ограниченные коммутационные возможности, так как каждый процессор может соединяться только с четырьмя соседними процессорами и может использоваться при необходимости как коммутатор приращений этих четырех соседних процессоров, что не обеспечивает унирерсальность коммутации, Расширению же коммутационных возможностей известного процессора ИВС препятствуют резко возрастающие при этом затраты оборудования и увеличение числа внешних связей, что делает в этом случае невозможным создание на его основе ИВС большой вычислительной мощности. В то же время ограниченные коммутационные возможности известного процессора ИВС затрудняют программирование задачи и требуют значительного времени на подготовку задачи к решению на данной ИВС, так как наряду со сложностью составления структурной схемы решения задачи, т.е. сложностью вложения задачи в ИВС, вследствие ограниченности связей могут возникать и тупиковые ситуации (нехватка связей), 1101821т.е. когда задача не вкладывается в ИВС, построенную на основе известного процессора.Целью изобретения является расширение области применения путем реше ния более сложных систем уравнений. Поставленная цель достигается тем,что в модуль ИВС, содержащий коммутатор и цифровой интегратор, причемвыход установки в исходное состояние,группа выходов начальных данных подынтегральной функции и выход импульса,сопровождения начальных данныхподывтегральной функции коммутаторасоединены соответственно с входомустановки в исходное состояние, сгруппой входов начальных данных ивходом разрешения записи начальныхданных цифрового интегратора, а первый вход, группа входов и второйвход коммутатора соединены с входомвыбора модуля, с шиной начальных данных и входом сброса модуля, введенырегистр адреса модуля, группа из 3 5регистров адреса входных приращений(где 3 - число входных приращенийцифрового интегратора), блок сравнения адресов модуля, группа из 3блоков сравнения адресов входныхпрйращений, группа из 3 триггеровположительных приращений, группа из3 триггеров отрицательных приращений, группа из 3 входных элемен.тов И положительных приращений, груп 35па из 3 входных элементов И отрица -тельных приращений, выходные элементы И положительных и отрицательныхприращений, счетчик тактов, элемент ИЛИ, неполный дешифратор и фср 40мирователь длительности импульсоз,причем выход установки в исходноесостояние, 1 - я группа информационных выходов и выход 1 -го импульса из группы выходов импульсов сопро, с,вождения начальных данных коммутатора соединены соответственно с входомустановки нуля, группой информационных входов и входом разрешения записи-го регистра адреса входныхприращений группы ( = 1,2, Л ),50а выход установки в исходное состояние, (1+1)-я группа информационныхвыходов и выход (3+1)-го импульсаиз группы выходов импульсов сопровождения начальных данных коммутаторасоединены соответственно с входомустановки нуля, с группой информационных входов и входом разрешения записи регистра адреса модуля, крометого, выход установки в исходное состояние коммутатора соединен с входомустановки нуля счетчика тактов, свходом сброса формирователя длительности импульсов и с входом элемента ИЛИ, единичный выход каждого раэ-ряда регистра адреса модуля соединенс первой группой входов блока сравнения адресов модуля, вторая группавходов которого соединена с группойединичных выходов счетчика тактов,а выход - с первым входом выходногоэлемента И положительных приращенийи с первым входом выходного элемента И отрицательных приращений, вторые входы которых соединены соответственно с выходами положительного и отрицательного приращения интеграла цифрового интегратора, а выходы -с выходами положительных и отрицательных приращений процессора соответственно, единичный выход каждогоразряда , -го регистра адреса входных приращений группы соединен спервой группой входов 1 -го блокасравнения адресов входных приращенийгруппы, вторая группа входов которого соецинена с группой единичныхвыходов счетчика тактов, а выход 1 -гоблока сравнения адресов входных приращений группы - с первым входом1 -го входного элемента И положительных приращений группы и с первымвходом-го входного элемента И отрицательных приращений группы, вторые входы которых соединены соответственно с входом положительных приращений модуля и с входом отрицательных приращений модуля, а выходы -соответственно с единичным входом-го триггера положительных приращений группы и с единичным входом 1 -готриггера отрицательных приращенийгруппы, едини ейные выходы которыхсоединены соответственно с 1 -ми входами из групп входов положительныхи отрицательных значений входныхприращений цифрового интегратора,группа входов неполного дешифраторас группой единичных выходов счетчикатактов, выходы "остояния (К +1)+1) неполного дешифратора (г;н гц -количество разрядов в регистре подынтегральной функции цифрового интегратора),соединены соответственно с первым, вторым н третьим входами группы71101тактовых входов формирователя длительности импульсов, нулевой вход каждого триггера положительных приращенийгруппы и каждого триггера отрицательных приращений группы соединены с5выходом элемента ИЛИ, второй входкоторого соединен с выходом состояния (В +а+1) неполного дешифратора,выходы сигнала длительностью а тактов и сигнала длительностью (в) 10тактов формирователя длительностиимпульсов и выход состояния (й+п 1+1)неполного дешифратора соединены соответственно с входом сигнала разрешения вычислений, с входом сигнала 15выделения остатка интеграла и с входом сигнала конца итерации цифровогоинтегратора, счетный вход счетчикатактов подключен к входу разрешениясчета модуля, а выход состояния 20(г 1+р+1) неполного дешифратора соединен также с выходом контроля тактовмодуля,Кроме того, формирователь длительности импульсов содержит два элемента ИЛИ и два триггера, причем выходпервого элемента ИЛИ и выход второгоэлемента ИЛИ соединены соответственно с нулевым входом первого триггераи с нулевым входом второго триггера,первые входы первого элемента ИЛИ ивторого элемента ИЛИ соединены свходом сброса формирователя первыйвход из группы тактовых входов формирователя соединен с единичными вхо 35дами первого и второго триггеров,единичные выходы которых соединенысоответственно с выходом сигнала длительностью Ч тактов и с выходом сигнала длительностью (щ) тактаФормирователя, а вторые входы второго элемента ИЛИ и первого элемента ИЛИ соединены соответственно свторым и третьим входами из группытактовых Входов формирователяф первьгй 45вход из группы тактовых входов формирователя соединен с единичными входами первого и второго триггеров.На фиг. 1 представлена структурнаясхема модуля ИВС; на Фиг. 2 - примерреализации цифрового интегратора;на фиг. 3 - схема реализации коммутатора, на фиг. 4 - схема реализациирегистрирующего устройства, на фиг.5 схема реализации узла масштабированияцифрового интегратора, на фиг. 6 - 55схема реализации входного узла цифрового интегратора, на фиг. 7 - схемареализации узла выделения выходных 821 8приращений цифрового интегратора 1, на Фиг. 8 - пример объединения модулей в ИВС.Модуль ИВС, представленный на фиг. 1, содержит коммутатор 1, цифровой интегратор 2, регистр 3 адреса модуля, регистр 4 адреса входных приращений, счетчик 5 тактов, формирователь 6 длительности импульсов, блок 7 сравнения адресов модуля, блоки 8 сравнения адресов входных прира щений, выходной элемент И 9 положительных приращений, выходной элемент И 10 отрицательных приращений, входные элементы И 11 положительных приращений, входные элементы И 12 отрицательных приращений, триггеры 13 положительных приращений, тригг еры 14 отрицательных приращений, элемент ИЛИ 15, неполный дешифратор 16.Цифрой 17 обозначен вход выбора модуля, цифрой 18 - шина начальных данных, цифрой 19 - шина сброса, цифрой 20 - вход разрешения счета модуляЦифрами 21 и 22 обозначены соответственно вход положительных приращений модуля и вход отрицательных,приращений моцуля, цифрами 23 и 24 соответственно выход положительных приращений модуля и выход отрицательных приращений модуля, а цифрой 25 выход контроля тактов модуля. В состав интегратора 2, представленного на фиг. 2, входят узел 26 масштабирования, входной узел 27, сумматор 28 подынтегральной функции, первый элемент 29 задержки, узел 30 умножения, регистр 31 подынтегральной функции, сумматор 32 остатка интеграла, второй элемент 33 задержки, узел 34 выделения выходных приращений, регистр 35 остатка интеграла.Цифрами 36 и 37 обозначены соответственно первый и второй входы цифрового интегратора, цифрой 38 группа входов цифрового интегратора, цифрой 39 - выход цифрового интегратора. В состав коммутатора 1 модуля ИВС, представленного на фиг. 3, входят первый элемент И 40, элемент ИЛИ 41,. элемент 42 задержки, счетчик 43, второй элемент И 44, дешифратор 45, группа элементов И 46, группа элементов И 47. Цифрами 48-50 обозначены соответственно первый, второй и третий входы коммутатора 1, а цифра 9 1101 ми 51 и 52 - соответственно первый и второй выходы коммутатора.В состав формирователя 6 длительности импульсов модуля ИВС, представленного на фиг. 4, входят первый элемент ИЛИ 53, второй элемент ИЛИ 54, первый триггер 55, второй триггер 56. Цифрой 57 обозначен вход Формирователя, цифрами 58 - группа входов этого формирователя, цифрой 59 выход формирователя.В состав узла 26 масштабирования цифрового интегратора 2, представлен - ного на Фиг. 5, входят элемент ИЛИ 60, триггер 61, первый элемент И 62, первый элемент 63 задержки, второй элемент И 64, второй элемент 65 задержки, третий элемент И 66, третий элемент 67 задержки, четвертый элемент И 68, Цифрами 69-71 обозначены соответственно первый, второй и третий входы узла 26 масштабирования, а циФрой 72 - выход узла.В состав входного узла 2 цифрового интегратора 2, представленного на фиг. 6, входят первый комбинационный сумматор 73, первый элемент И 74, второй элемент И 75, третий элемент И 76, первый элемент ИЛИ 77, второй комбинационный сумматор 78, четвертый элемент И 79, пятый элемент И 80, шестой элемент И 81, второй элемент ИЛИ 82, элемент НЕ 83 седьмой элемент И 84, триггер 85, восьмой элемент И 86, третий эле 35 мент ИЛИ 87, первый элемент 88 задержки, третий комбинационный сумматор 89, второй элемент 90 задержки, Цифровой 91 обозначен вход входного узла 27, цифрами 92 - группа входов40 этого узла, цифрой 93 - выход вход - ного узла 27. В состав узла 34 выделения выход - ных приращений цифрового интегратора 2, представленного на фиг. 7, вхо 45 дят первый элемент И 94, первый элемент 95 задержки, второй элемент 96 задержки, второй элемент И .97, первый элемент НЕ 98 третий элемент И 99, первый элемент ИЛИ 100, первый триг гер 101, четвертый элемент И 102, второй элемент НЕ 103, пятый элемент И 104, второй элемент ИЛИ 105, второй триггер 106, шестой элемент И 107, седьмой элемент И 108.Цифрами 109-111 обозначены соответственно первый, второй и третий входы узла 34 выделения выходных прира 821 10щений, а цифрой 11 - выход узла 34выделения выходных приращений,Первый выход комутатора 1 соединен с первым входом цифрового интегратора 2, а второй выход - с входомрегистра 3 адреса модуля, с вхо домкаждого регистра 4 адреса входныхприращений, с первым входом счетчика 5 тактов и с входом формирователя 6,Выход каждого разряда регистра 3адреса процессора соединен с первойгруппой входов блока 7 сравненияадресов процессоров, вторая. группавходов которого соединена с группойвыходов счетчика 5 тактов. Выход каждого разряда каждого регистра 4 адреса входных приращений соединен спервой группой входов соответствующего блока 8 сравнения адр сов входныхприращений, вторая группа входов каждого из которых соединена с группойвыходов счетчика 5 тактов.Выход блока 7 сравнения адресовмодуля соединен с первым входом выходного элемента И 9 положительных приращений и с первым входом выходногоэлемента И 10 отрицательных приращений, вторые входы которых соединены с выходом цифрового интегратора 2,Выход каждого блока 8 сравненияадресов входных приращений соединенс первым входом соответствующеговходного элемента И 11 положительных приращений и с первым входом соответствующего входного элемента И 12отрицательных приращений, выходыкахщого из которых соединены соответственно с единичными входами соответствующего триггера 13 положительныхприращений и соответствующего триггера 14 отрицательных приращений, единичные выходы которых соединены с соответствующим входом из группы входов цифрового интегратора 2.Нулевой вход каждого триггера 13 положительных приращений и каждого триггера 14 отрицательных приращений соединен с выходом элемента ИЛИ 15, первый и второй входы которого соединены соответственно с вторым вы - ходом коммутатора 1 и с выходом неполного дешифратора 16, группа входов которого соединена с группой выходов счетчика 5 тактов, а группа выходов - с группой входов фор:1 ирователя 6.Второй вход цифрового интегратора 2 соединен с выходом Формировате12 01821 ла соединены с первым входом 36 циф 1 О 15 20 Выход неполного дешифратора 16 соединен также с выходом 25 контроля тактов модуля.Выход узла 26 масштабирования30 соединен с входом входного узла 27, выход которого соединен с первым входом сумматора 28 подынтегральной функции, первый выход которого соединен через первый элемент 29 задержки с вторым входом сумматора 28 по дынтегральной функции, а второй выход - с входом узла 30 умножения и с входом регистра 31 подынтегральной функции, выход которого соединен с третьим входом сумматора 28 подынтег40 ральной функции и с входом узла 26 масштабирования.Выход узла 30 умножения соединен с первым входом сумматора 32 остатка интеграла, первый выход которого 45 соединен через второй элемент 33 задержки с вторым входом сумматора 32 остатка интеграла, а второй выход - с входом узла 34 выделения выходных приращений и с входом регистра 35 50 остатка интеграла, выход которого соединен с третьим входом сумматора 32 остатка интеграла.Второй вход узла 26 масштабирова-. ния, второй вход регистра 31 подынтегральной функции, второй вход узла 34 выделения выходных приращений и второй вход регистра 35 остатка интегра 11 11 ля 6 и с выходом неполного дешифратора 16.Первый, второй и третий входы коммутатора 1 соединены соответственно с входом 17 выбора процессора, с шиной 18 начальных данных и с шиной 19 сброса.Второй вход счетчика 5 тактов соединен с входом 20 разрешения счета процессора.Второй вход каждого входного элемента И 11 положительных приращений и второй вход каждого входного элемента И 12 отрицательных приращений соединены соответственно с входом 21 положительных приращений модуля и с входом 22 отрицательных приращений модуля.Выход выходного элемента И 9 положительных приращений и выход выходного элемента И 10 отрицательных ,приращений соединены соответственно с выходом 23 положительных приращений модуля и с выходом 24 отрицательных приращений модуля. рового интегратора 2 Третий вход узла 26 масштабирования, второй вход узла 30 умножения,третий вход регистра 3 подынтегральной функции, третий вход узла 34 выделения выходных приращении и третии вход регистра 35 остатка интеграла соединены с вторым входом 37 цифрового интегратора 2,Третий вход узла 30 умножения соединен с одним из входов группы входов 38 цифрового интегратора 2, а остальные входы этой группы входов 38 цифрового интегратора 2 - с группой входов входного узла 27.Выход узла 34 выделения выходных приращений соединен с выходом 39 цифрового интегратора 2. Выход первого элемента И 40 соединен с входом элемента ИЛИ 41, второй вход которого соединен с выходом элемента 42 задержки, а выход - с входом счетчика 43, второй вход которого соединен с выходом второго элемента И 44, а группа выходов - с группой входов дешифратора 45, выход которого соединен с входом элемента 42 задержки и с первыми входами группы элементов И 46, Каждый выход группы выходов дешифратора 45 соединен с первыми входами соответствующей группы элементов И 47 изгрупп этих эле. ментов. Первый вход. первого элемента И 40, первый вход второго элемента И 44, вторые входы группы элементов И 46 и вторые входы каждой группы элементов И 47 из ч групп этих элементов соединены с первым входом 48 коммутатора 1. Второй вход второго элемента И 44, третьи входы группы элементов И 46 и третьи входы каждой группы элементов И 47 изгрупп этих элементов соединены с вторым входом 49 коммутатора 1, а второй вход первого элемента И 40 с третьим входом 50 коммутатора 1. Выход первого элемента И 40, выход дешифратора 45 и выходы группы элементов И 46 объединены в первый выход 51 коммутатора 1, а выход первого элемента И 40, группа выходов дешифратора 45 и выходы каждой группы элементов И 47 из и групп этих элементов объединены во второй выход 52. коммутатора 1. Выходы первого элемента ИЛИ 53 и второго элемента ИЛИ 54 соединены13 1101 соответственно с нулевым входом первого триггера 55 и нулевым входом второго триггера 56. Первый входы первого элемента ИЛИ 53 и второго элемента ИЛИ 54 соединены с входом 57 формирователя, а вторые входы первого элемента ИЛИ 53 и второго элемента ИЛИ 54 и единичные в: оды первогогриггера 55 и второго триггера 56 сое динены с группой входов 58 формирова О теля. Единичный выход первого триггера 55 и единичный выход второго триггера 56 соединены с выходом 59 формирователя.Выход элемента ИЛИ 60 соединен с нулевым входом триггера 61, нулевой выход которого соединен с входом первого элемента И 62, выход которого соединен с входом второго элемента 65 задержки, выход которого соединен с единичным входом триггера 61, с входом второго элемента И 64 и с входом второго элемента 65 задержки, выход которого соединен с входом третьего элемента И 66 и с входом 25 третьего элемента 67 задержки, выход которого соединен с входом чет - вертого элемента И 68. Второй вход первого элемента И 62 соединен с первым входом 69 узла 26 масштабирования, а первый вход элемента ИЛИ 60 - с вторым входом 70 узла 26 масштабирования, Второй вход элемента ИЛИ 60, третий вход первого элемента И 62 и вторые входы второго элемента И 64,35 третьего элемента И 66, четвертого элемента И 68 соединены с третьим входом 71 узла 26 масштабирования. Выходы элемента ИЛИ 60, второго эле - мента И 64, третьего элемента И 66 и четвертого элемента И 68 соединены с выходом 72 узла 26 масштабирования.Первый, второй и третий выходы пер вого комбинационного сумматора 73 соединены соответственно с первымl 5 входом первого элемента И 74, первым " входом второго элемента И 75, первым входом третьего элемента И 76, выходы каждого из которых соедцнены с входами первого элемента ИЛИ 77. Первый, второй и третий выходы второго комбинационного сумматора 78 соединены соответственно с первым входом четвертого элемента И 79, с первым входом пятого элемента И 80, с первым входов шестого элемента И 81, 55 выходы каждого из которых соединены с входами второго элемента ИЛИ 82, выход которого соединен с входом эле 821 14мента НЕ 83 и с входом седьмого элемента И 84, второй вход которого соединен с нулевым выходом триггера 85,единичный выход которого соединенс входом восьмого элемента И 86, второй вход которого соединен с выходомэлемента НЕ 83, а выход - с входомтретьего элемента ИЛИ 87, второй входкоторого соединен с выходом седьмогоэлемента И 84 и с входом первого элемента 88 задержки, выход которого соединен с единичным входом триггера 85.Выход первого элемента ИЛИ 77 и выходтретьего элемента ИЛИ 87 соединенысоответственно с первым и вторым входами третьего комбинационного сумматора 89, первый выход которого сое -динен через второй элемент 90 задержки с третьим входом третьего комбинационного сумматора 89. Вторые входы первого элемента И 74 второгоэлемента И 75, третьего элемента И 76,четвертого элемента И 79, пятого элемента И 80, шестого элемента И 81и нулевой вход триггера 85 соединеныс входом 91 входного узла 27, а группа входов первого комбинационногосумматора 73 и группа входов второгокомбинационного сумматора 78 - с группой входом 92 входного узла 27, второй вьход третьего комбинационногосумматора 89 соединен с выходом 93входного узла 27,Выход первого элемента И 94 соединен через первый элемент 95 задержки с входом элемента 96 задержки,с входом второго элемента И 97 и свходом первого элемента НЕ 98, выходкоторого соединен с входом третьегоэлемента И 99, выход которого соединен с входом первого элемента ИЛИ 100,выход которого соединен с нулевымвходом первого триггера 101, единичный вход которого соединен с выходомвторого элемента И 97. Выход второгоэлемента 96 задержки соединен с входом четвертого элемента И 102 и свходом второго элемента НЕ 103, выход которого соединен с входом пятого элемента И 104, выход которогосоединен с входом второго элемента ИЛИ 105, выход которого соединенс нулевым входом второго триггера 106,единичный вход которого соединен свыходом четвертого элемента И 102.Нулевой и единичный выходы первоготриггера 101 соединены соответственнос первым входом шестого элемента И 107и с первым входом седьмого элемец15 1101 та И 108, второй вход каждого из которых соединен с единичным выходом второго триггера 106. Первый вход первого элемента И 94 соединен с первым входом 109 узла 34 выделения выходных приращений, а второй вход первого элемента ИЛИ 100 и второй вход второго элемента ИЛИ 105 соединены с вторым входом 110 узла 34 выделения выходных приращений. Вто- О рые входы первого элемента И 94, второго элемента И 97, третьего элемента И 99, четвертого элемента И 102 и пятого элемента И 104 соединены с третьим входом 111 узла 34 выделе ния выходных приращений, а выходы шестого элемента И 107 и седьмого элемента И 108 соединены с выходом 112 узла 34 выделения выходных приращений. 20 Перед началом работы производится установка модуля ИВС в исходное состояние, При этом на вход 17 выбора модуля подается единичный сигнал, который, пройдя через вход 48 коммутатора 1, откроет элемент И 40, и при подаче сигнала сброса через вход 19 модуля на вход 50 коммутатора 1 этот сигнал пройдет через открытый элемент И 40 и поступит через30 выход 52 на входы установки нуля регистров 3 и 4 и счетчика 5 устанавливая их в нулевое состояние, а пройдя через элемент ИЛИ 15, этот сигнал установит в нулевое состояниетриггеры 13 и 14. Кроме того, сигнал сброса с выхода 52 коммутатора 1 поступит на вход 57 блока 6 и, пройдя через элементы ИЛИ 53 и ИЛИ 54, сбросит в нулевое состояние триггеры 55 4 б и 56. Одновременно сигнал сброса поступит с выхода элемента И 40 через выход 51 коммутатора 1 в цифровой интегратор 2 через первый его вход 36 на входы установки нуля регистров 31и 35, устанавливая их в нулевое состояние, а пройдя с входа 36 цифрового интегратора 2 через вход 70 узла 26 масштабирования и через элемент ИЛИ 60, установит в нулевое состояние триггер 61. Кроме того, с выхода элемента ИЛИ 60 сигнал сброса пройдет через выход 72 узла 26 масштабирования и вход 91 входного узла 27 на нулевой вход триггера 85 55 и установит его в нулевое состояние. Одновременно сигнал сброса с входа 36 цифрового интегратора поступит 821 16 на вход 110 узла 34 выделения выходных приращений и, пройдя через элементы ИЛИ 100 и ИЛИ 105, сбросит в нулевое сОстояние соответственно триггер 101 и триггер 106, Кроме того, сигнал сброса с выхода элемента И 40 пройдет через элемент ИЛИ 41 и сбросит в нулевое состояние счетчик 43.Затем производится ввод начальных данных. При этом через вход 17 на вход 48 коммутатора 1 подается потенциал, поступающий на вход элемента И 44, ка вторые входы группы элементов И 46 и на вторые входы каждой группы элементов И 47 из И групп этих элементов, а по шине 18 на шину 49 коммутатора 1 подаются параллельным кодом начальные данные, которые поступают с шины 49 на третьи входы группы элементов И 46 и на третьи входы каждой групп. элементов И 47 из й групп этих элементов. Одновременно по одной из линий связи шины 18 начальных данных (обычно по последней линии связи) в коммутатор 1 на второй вход элемента И 44 поступают импульсы сопровождения данных, которые проходят через этот элемент И 44 (на второй его вход поступает потенциал с входа 17) на суммирующий вход счетчика 43, состояние которого расшифровывается дешифратором 45. Причем при поступлении каждого нового импульса сопровождения данных состояние счетчика 43 увеличивается на единицу, и на соответствующем выходе дешифратора 45 появляется единичный сигнал, который разрешает прохождение начальных данных через соответствующую группу элементов И 47 из и групп этих элементов и через выход 52 коммутатора 1 на входы параллельной записи регистра 3 или соответствующего регистра 4 адреса входных приращений. Одновременно этот единичный сигнал с соответствующего выхода дешифратора 45 поступит через выход 52 коммутатора 1 на вход разрешения записи соответствующего регистра 3 или 4, обеспечивая тем самым ввод начальной информации в соответствующий регистр. При этом в регистр 3 запишется адрес, соответствующий номеру модуля на структурной схеме решения задачи, а в регистры 4 - соответствующие этому модулю адреса входных приращений, т,е. номера тех модулей, которые по структурной схеме решения. задачи

СмотретьЗаявка

3475115, 26.07.1982

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

КРИВОРУЧКО ИВАН МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 7/64

Метки: вычислительной, интегрирующей, модуль, структуры

Опубликовано: 07.07.1984

Код ссылки

<a href="https://patents.su/19-1101821-modul-integriruyushhejj-vychislitelnojj-struktury.html" target="_blank" rel="follow" title="База патентов СССР">Модуль интегрирующей вычислительной структуры</a>

Предыдущий патент: Датчик случайных последовательностей

Следующий патент: Делительно-множительное устройство

Случайный патент: Устройство для изготовления плоских изделий из формуемой смеси