Устройство для побитовой обработки чисел, представленных в форме с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

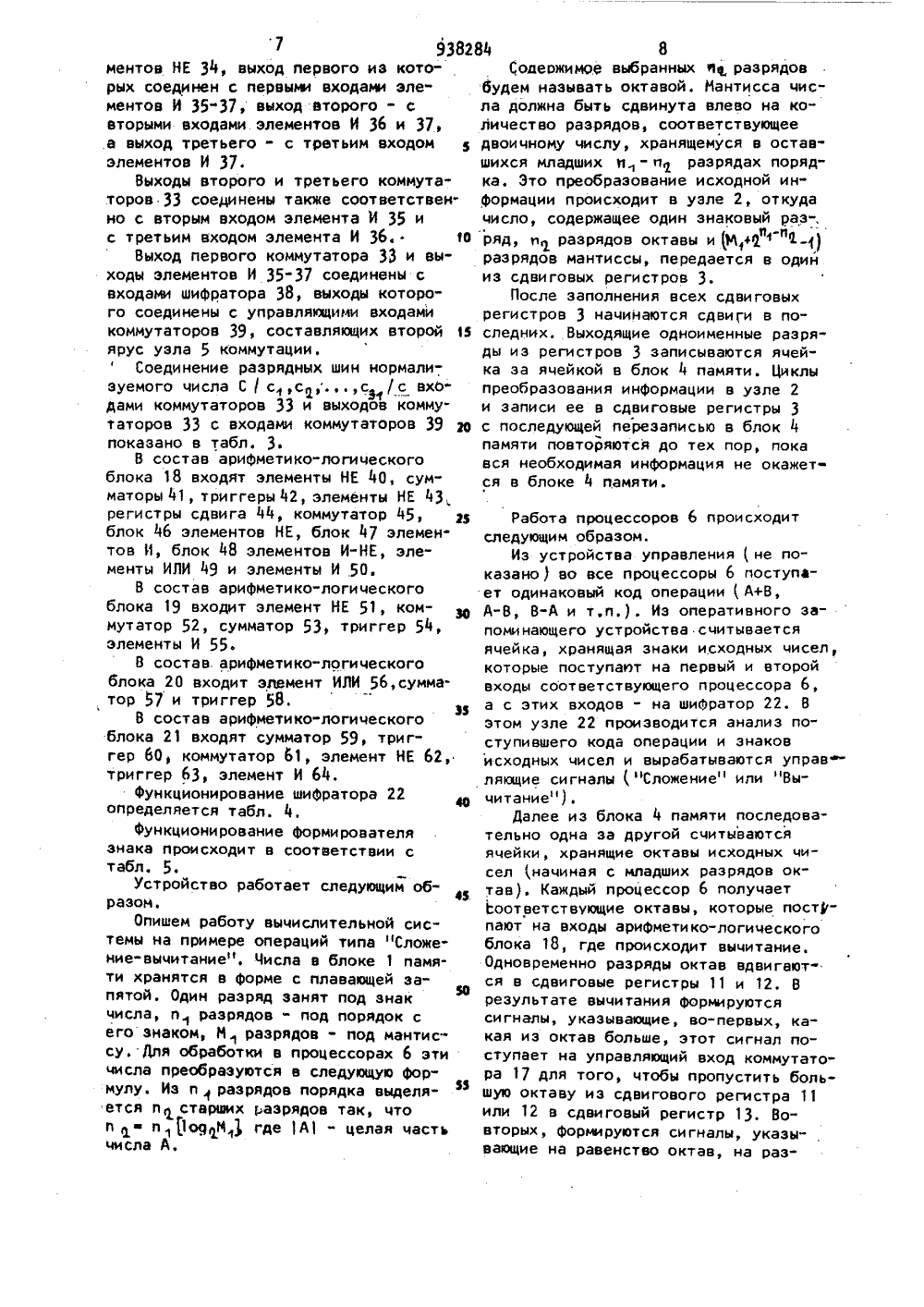

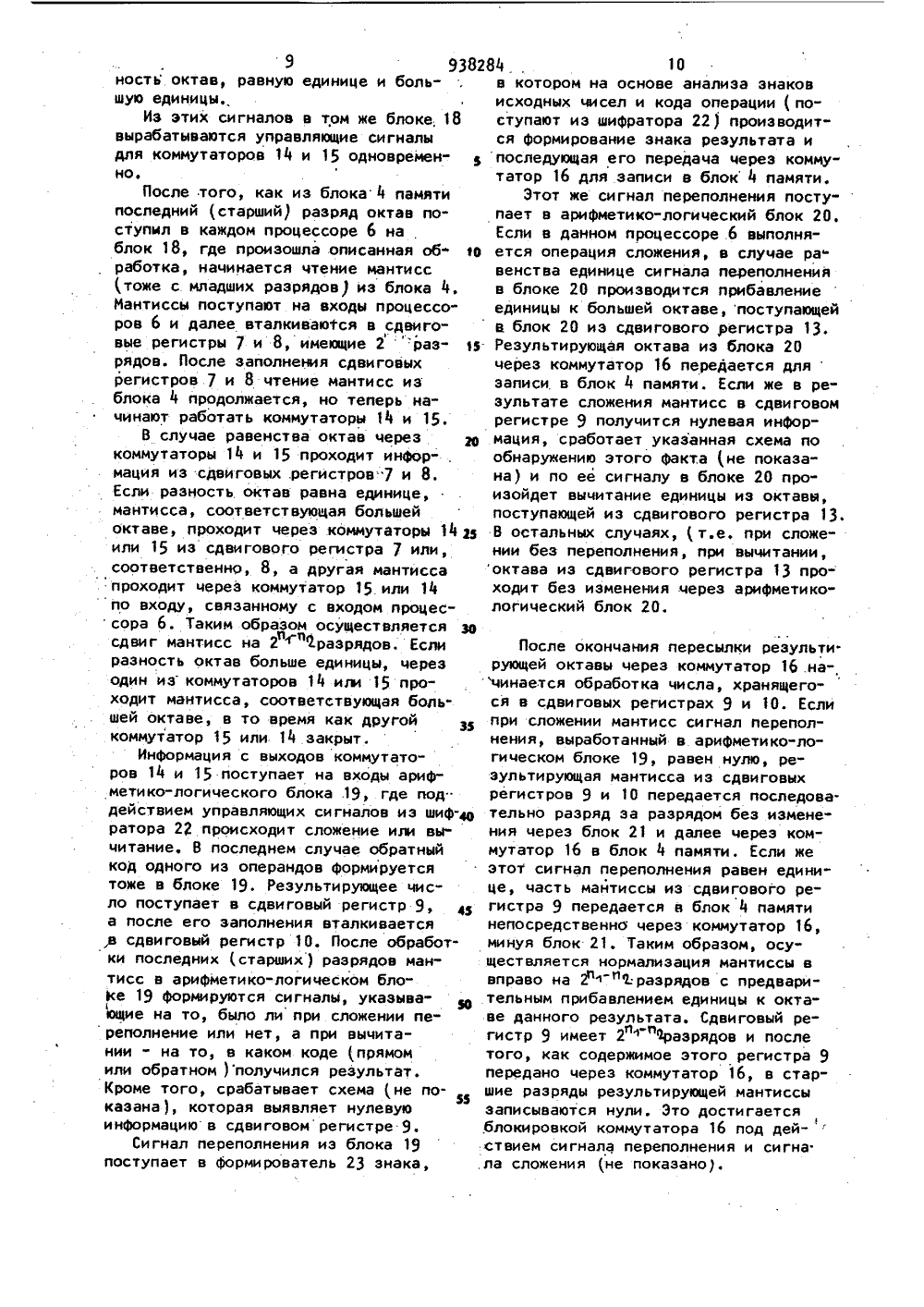

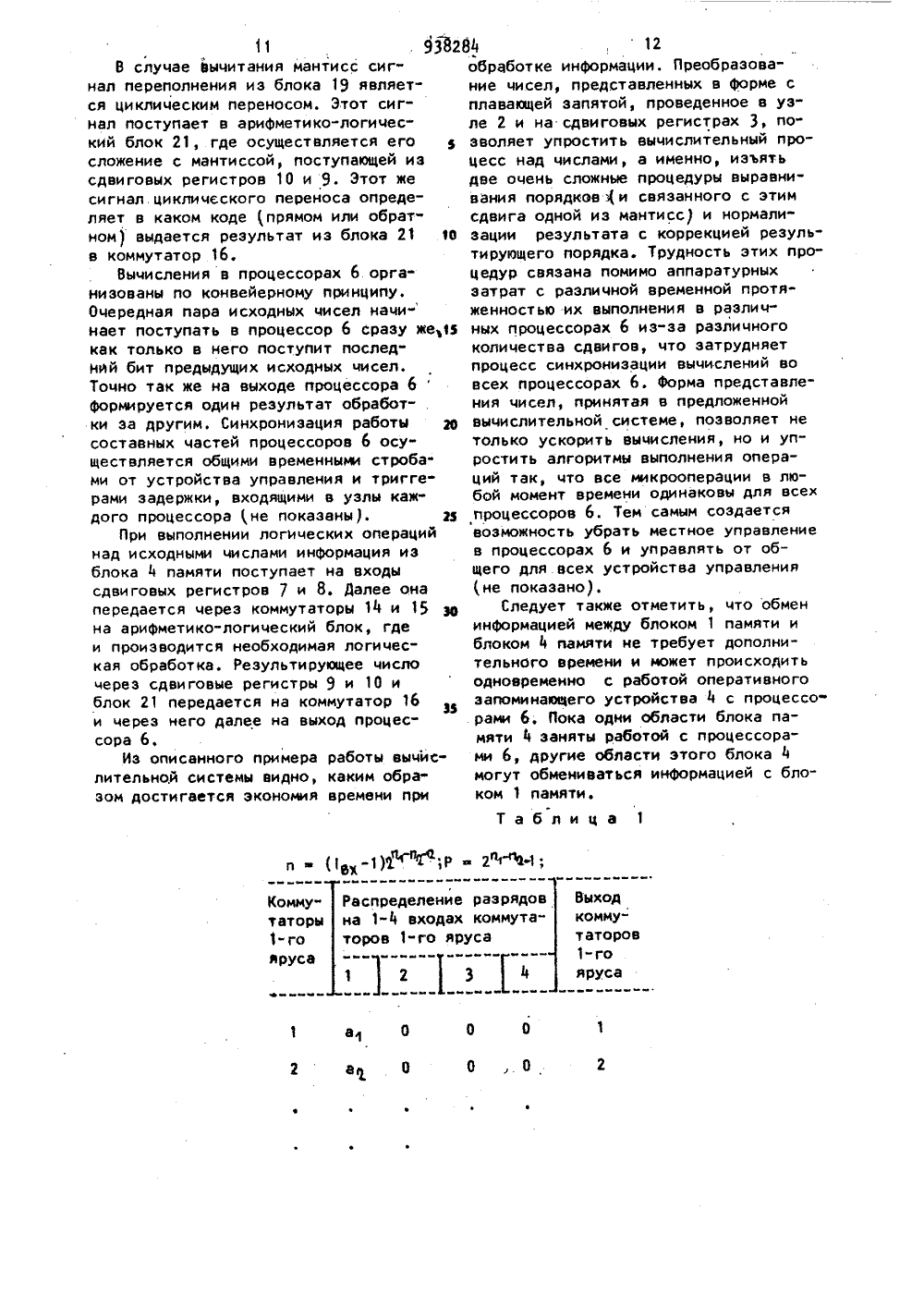

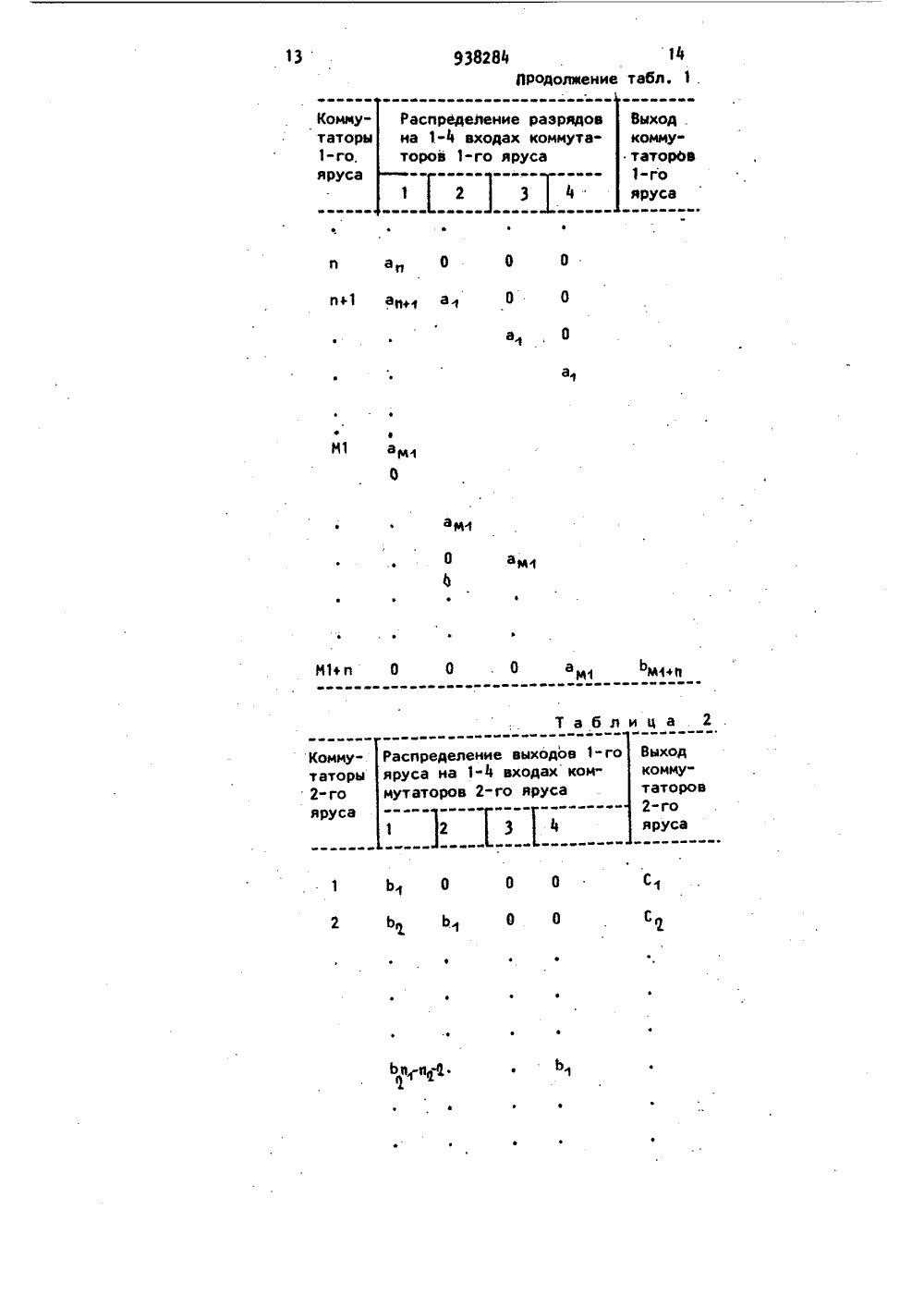

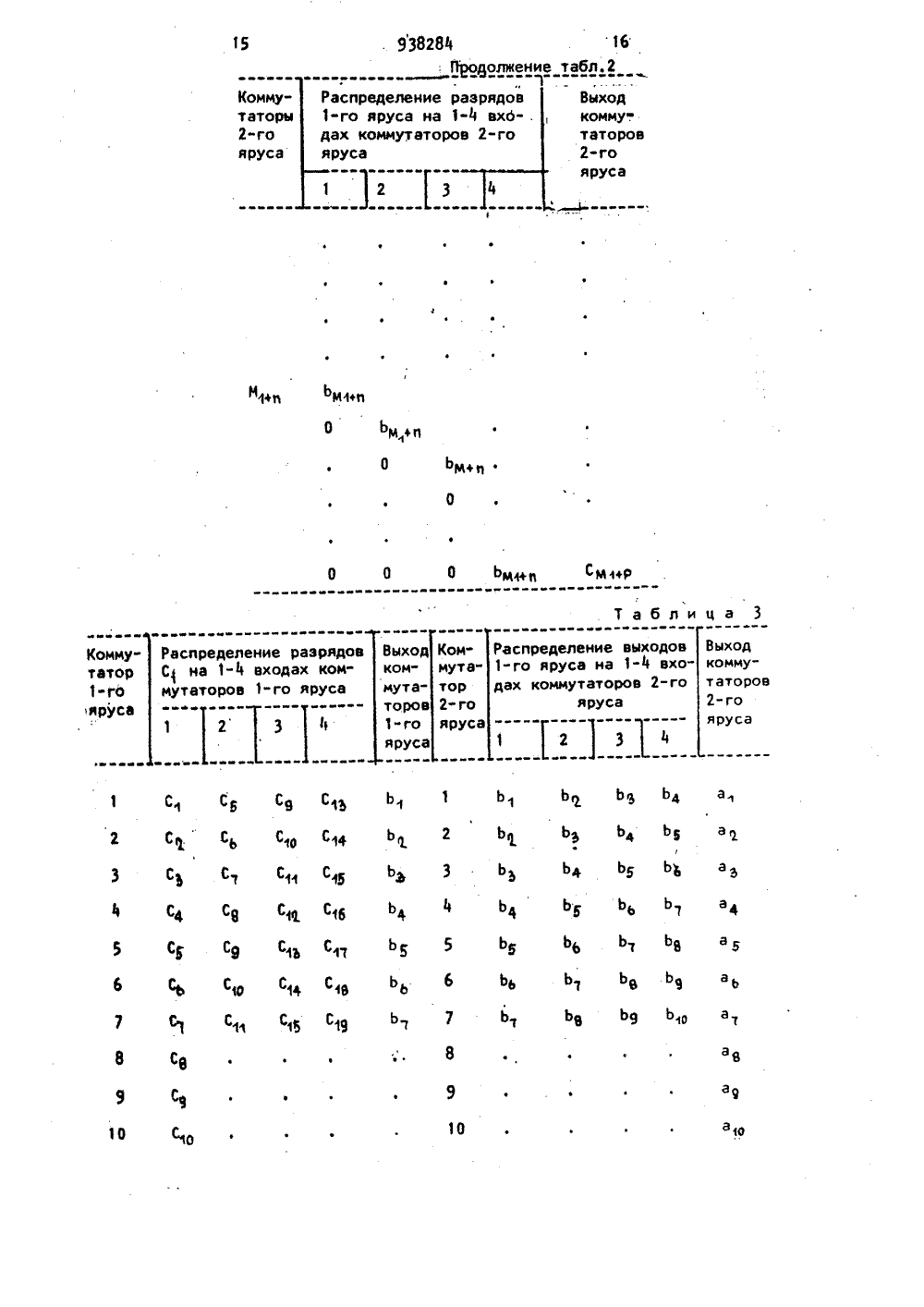

(и)938284 ОП ИСАНИЕИЗЬВРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски кСоциалистичесиикреспублик(23)Приорнтет(51)М. Кл. С 06 Г 15/00 Зееудэфстеснныб квинтет ьИР дв делам нзебретеннЯ и етеритнЯ(72) Авторы изобретения 7) Заявитель 54) УСТРОЙСТВО ДЛЯ ПОБИТОВОЙ ОБРАБОТКИ ЧИСЕЛ ПРЕДСТАВЛЕННЫХ В ФОРМЕ С ПЛАВАЮЩЕЙ ЗАПЯТ запоминающего устрой Изобретение относи тельной технике, а им цессорным вычислительИзвестно устройство тельной обработки чис оперативва 2. я к вычисли. но многопром системам.для последова" 11."ства ность, м устрасширение функфей и увеличение Недостатком известного устройстваявляется отсутствие возможности обработки чисел, представленных в формес плавающей запятой,Наиболее близким к изобретениютехническим решением является вычислительное устройство, содержащее запоминающий блок, узел сдвига, сдвиговые регистры, оперативное запоминающее устройство, узел нормализации,процессоры, состоящие из сдвиговыхрегистров, коммутаторов, узлов арифметико-логической обработки, узла формирования знака, причем выходы оперативного запоминающего устройства соединены с первыми и вторыми входамипроцессоров, а выходы процессоров соединены с соответствующими входами Недостатком известного устроиявляется невысокая производительсвязанная с тем, что на известноройстве нельзя непосредственно обрабатывать числа, представленные в форме с плавающей запятой,Цель изобретения "циональных возможностпроизводительности.Указанная цель достигается тем,что в устройстве для побитовой обработки чисел, представленных в формес плавающей запятой, содержащем й процессоров, каждый из которых содержитчетыре коммутатора, четыре арифметико-логических блока, шифратор, семьрегистров сдвига и формирователь знака, а также общие для всех процессоров два блока памяти, два узла ком"мутации и а регистров сдвига, выходыкоторых объединены и подключены к управляющему входу второго блока памяЧаееееееайЕеем еа Операция Знаки исходных1еч ееЛ е е аЗн,А Зн.Веачаеа ааааа ееаеа Знак результатаЗн.С Циклперенос Зн,А Зн,А О Зн.АО О А+В О 1 Зн.В О О Зн.А 1 Зн.В О О О Зн.А1 Инв.Зн.АО Зн.А1 Инвер.Зн.А Зн.В Зн.В О Зн.ВИнв.Зн.В О Зн,В ВА О 1 Инв.Зн.В йа ееа еааее Таблица 522 938284 21 Продолжение табл. 5 Знак результатаЗн.С Операция,Знаки исходныхчиселеещшта етЗн.А Зн.В Циклперенос А - 1 В 1 0 1 . 1 формула и зобрет.ения 1. Устройство для побитовой обра ботки чисел, представленных в Форме с плавающей запятой, содержащее Й процессоров, каждый из которых содержит четыре коммутатора, четыре арифметико-логических блока, шифратор 2 семь регистров сдвига и формирователь знака, а также общие для всех процессоров.два блока памяти, два узла коммутации и п регистров сдвига, выходы которых объединены и подключены к уп- эв равляющему входу второго блока памяти, вход данных которого подключен к выходам процессоров, выход второго блока памяти подключен к первому и второму входам каждого процессора, инфор. мационный вход первого блока памяти подключен к входу ввода устройства, третьи входы каждого процессора объединены и подключены к входу кода операции устройства, о т л и- , ч а ю щ е е с я тем, что, с целью повышения производительности, входы Ю регистров сдвига объединены между собой и подключены к выходу первого узла коммутации, вход которого подключен к выходу первого блока памяти, вход которого соединен с выходом второго узла коммутации, вход которого соединен с выходом второго блока памяти, а в каждом процессоре выход первого коммутатора подключен к выходу процессора, первый, второй, третий и четвертый входы коммутатора соедине ны с выходом формирователя знака, выходом первого арифметико-логическоЯ го блока, выходом второго арифметикологического блока, выходом первого регистра сдвига и входом второго регистра сдвига, соответственно, выход которого соединен с первым информаци-.онным входом первого арифметико-логического блока, второй информационныйвход которого соединен с информационным входом формирователя знака, первым информационным входом второгоарифметико-логического блока и первымвыходом третьего арифметико-логического блока, второй выход которого соединен с входом первого регистрасдвига, первый информационный входтретьего арифметико-логического блока подключен к выходу второго ком"мутатора, а второй информационныйвход - к выходу третьего коммутатора,управляющие входы второго, третьегои четвертого коммутаторов объединеныи подключены к выходу четвертого ариф.метико-логического блока, первый информационный вход которого соединенс первым входом шифратора, входомтретьего регистра сдвига, входом четвертого регистра сдвига, первым информационным входом второго коммутатора и подключен к первому входу процессора, выход третьего регистра сдвига соединен с вторым информационнымвходом второго коммутатора, первыйинформационный вход третьего коммутатора соединен с входом пятого регистра сдвига, вторым информационным вхо"дом четвертого арифметико-логическогоблока, входом шестого регистра сдвига,вторым входом шифратора и подключенко второму входу процессора, выходшифратора подключен к управляющим вхо.дам первого, второго и третьего арифметико-логического блока и Формирова.теля знака, выход пятого регистрасдвига соединен со вторым информационным входом третьего коммутатора,выходы четвертого и шестого регистров сдвига соединены с первым и вторым информационными входами четверто.го коммутатора, соответственно, выход которого соединен с входом седьмого регистра сдвига, выход которогосоединен с вторым информационным входом второго арифметико"логическогоблока.2. Устройство по п 1, о т л и "ч а ю щ е е с я тем, что первый ариф 46метико"логический блок содержит элемент И, сумматор, два триггера, элемент НЕ и коммутатор, выход. которогосоединен с выходом блока, первый информационный вход коммутатора со" 15единен со входом элемента НЕ и информационным выходом сумматора, выходпереноса которого соединен с выходомпервого триггера, выход которого со"единен с входом переноса сумматора, 2 фпервый информационный вход которогосоединен с первым информационным вхо"дом блока, второй информационный иуправляющий входы блока соединены спервым и вторым входами элемента И, 2соответственно, выход которого со"единен с вторым информационным входомсумматора и входом второго триггера,выход которого соединен с управляющимвходом коммутатора, второй информа" Мрионный вход которого соединен с выходом элемента НЕ.3. Устройство по и. 1, о т л ич а ю щ е е с я тем, что второйарифметико-логический блок содержитэлемент ИЛИ, сумматор.и триггер, выход которого соединен со входом переноса сумматора, первый информационный вход которого соединен с выходом элемента .ИЛИ, первый информацион"вный, второй информационный и управляющий входы блока подключены к пер-вому и второму входу элемента ИЛИ ивторому информационному входу сумматора, соответственно, выход Переносасумматора соединен со входом триггера, выход суммы сумматора соединенс выходом блока,4. Устройство по и. 1, о т л и "ч а ю щ е е с я тем, что третийарифметико-логический блок содержитэлемент НЕ, коммутатор, сумматор,триггер и первый и второй элементы И,выходы которых подключены к первомуи второму вь 1 ходу блока, соответствен. но, первый информационный вход блокаподключен к первому информационномувходу коммутатора и входу элемента НЕ,выход которого соединен со вторым информационным входом коммутатора, управляющий вход которого соединен со вторым информационным входом блока и первыми входами первого и второго элементов И, соответственно, вторые входы которых объединены и подключены к выходу триггера и входу переноса сумматора, выход которого соединен со входом триггера, первый информационный вход сумматора соединен с выходом коммутатора, а второй информационный вход сумматора:- с управляющим входом блока.5, Устройство по и, 1, о т л ич а ю щ е е с я тем, что четвертый арифметико-логический блок содержит четыре элемента НЕ, два сумматора, два триггера, два регистра сдвига, коммутатор, два элемента ИЛИ, два элемента И, блок элементов НЕ, блок элементов И и блок элементов И-НЕ, выход которого соединен с первыми входами первого и второго элементов И, второй вход первого элемента И соединен с первым входом первого элемента ИЛИ и выходом первого элемента НЕ, вход которого соединен с выходом первого триггера и входом переноса первого сумматора, выход переноса которого соединен с входом триггера, а информационный выход - с входом первого регистра сдвига, выход которого соединен с первым входом коммутатора, второй вход которого соединен с выходом второго регистра сдвига, вход которого соединен с информационным выходом второго сумматора, выход пееноса которого соединен с входом торого триггера, выход которого соединен с входом второго элемента НЕ и входом переноса второго сумматора, первый информационный вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с пер,вым информационным входом блока и пер. вым информационным входом первого сумматора, второй информационный вход которого соединен с выходом четвертого элемента НЕ, вход которого соединен с вторым информационным входом блока и вторым информационным входом второго сумматора, выход коммутатора подключен к входу блока элементов НЕ, выход которого соединен с входом блока элементов И-НЕ и входом блока элементов И, выход которого соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ. выход второго элемента НЕ соединен с25 938281 26третьим входом коммутатора, вторыми 1. Рагспотоп В.О. ОАР 5 адд роиегвходами второго элемента И и второго о совроег ргосеыпя. - нЕ 1 есйго"элемента ИЛИ и выходом блока, выходы исв апд пьйгапеп 1 айоп", й У,первого и второго элементов И, перво, й 11.го и второго элементов ИДИ подключены у 2. Согзи Р. ап 4 оТЬегв. ТЬек выходу блока, вега 1 всгоргосезвогаггу (5 ИА) 5 уерИсточники информации, оп совр агсЬ, 5 сЬ, 1978, р. 230-235принятые во внимание при экспертизе (прототип ).938 г 84 дмч Ци оставитель П ехре 6 И. Гай д Щвыдк еаактщщ щщаказ о ко ий и ьаска Уищщщ Н. джиргам ТУ 73 Тираж 731ВНИИПИ Государственногпо делам изобретен113036 Москва ЖРалиал ППП ППатент", г. Ужго ЧистобородовУ КорректорПодписноемитета СССРоткрытийнаб. д, 4/5щ щщщ 1 дщщ щщщ щ щ щул. Проектная, 938 г 84ти, вход данных которого подключен к выходам процессоров, выход второго блока памяти подключен к первому и второму входам каждого процессора, информационный вход первого блока памяти подключен к входу ввода устройства, третьи входы каждого процессора объединены и подключены к вхо. ду кода операции устройства, входы в регистров сдвига объединены между 1 в собой и подключены к выходу узла ком" мутации, вход которого подключен к выходу первого блока памяти, вход которого соединен с выходом второго узла коммутации, вход которого соединен 1 с выходом второго блока памяти, а в каждом процессоре выход первого коммутатора подключен к выходу процес" сора, первый, второй, третий и четвертый входы коммутатора соединены с выходом формирователя знака, выходом первого арифметического блока, выходом второго арифметического бло" ка, выходом первого регистра сдвига и входом второго регистра сдвига соответственно, выход которого соеди" нен с первым информационным входом первого арифметико-логического бло" ка, второй информационный вход которого соединен с информационным входом формирователя знака, первым информационным входом второго арифмети ко-логического блока и первым выходом третьего арифметико"логического блока, второй выход которого соединен с входом первого регистра сдвига, пер. вый информационный вход третьего арифметико-логического блока подключен к выходу второго коммутатора, а второй информационный вход - к выхо 40 ду третьего коммутатора, управляющие входы второго, третьего и четвертого коммутаторов объединены и подключены к выходу четвертого арифметико-логического блока, первый информационный вход которого соединен с первым вхо"45 дом шифратора, входом третьего регистра сдвига, входом четвертого регистра сдвига, первым информационным входом второго коммутатора и подключен к первому входу процессора, выход 5 О третьего регистра сдвига соединен с вторым информационным входом второго коммутатора, первый информационный вход третьего коммутатора соединен с входом пятого регистра сдвига, вторыминформационным входом четвертого регистра сдвига, вторым входом шифрато" ра и подключен к второму входу процессора, выход шифратора подключен к управляющим входам первого, второго и третьего арифметико"логического блока и Формирователя знака, выход пятого регистра сдвига соединен с вторымн информационным входом третьего коммутатора, выходы четвертого и шестого регистров сдвига соединены с первым и вторым информационными входами четвертого коммутатора соответственно, выход которого соединен с входом седьмого регистра сдвига, выход которого соединен с вторым информацион ным входом второго арифметико-логического блока.Первый арифметико-логический блок содержит элемент И, сумматор, два триггера, элемент НЕ и коммутатор, выход которого соединен с выходом блока,.первый информационный вход коммутатора соединен с входом элемент та НЕ и инбормааионным выходом сумматора, выход переноса которого соединен с входом переноса сумматора, первый информационный вход которого соединен с первым информационным входом блока, второй информационный и управляющий входы блока соединены с первым и вторым входами элемента И соответственно, выход которого соединен с вторым информационным входом сумматора и входом. второго триггера, выход которого соединен с управляющим входом коммутатора, второй информационный вход которого соединен с выходом элемента НЕ.Второй арифметико-логический блок содержит элемент ИЛИ, сумматор и триггер, выход которого соединен с входом переноса сумматора, первый инФормационный вход которого соединен с выходом элемента ИЛИ, первый информационный, второй информационный и управляющий входы блока подключены к первому и второму входам элемента ИЛИ и второму информационному входу сумматора соответственно, выход переноса сумматора соединен с входом триггера, выход суммы сумматора соединен с выходом блока.Третий арифметико-логический блок содержит элемент НЕ, коммутатор, сумматор, триггер, первый и второй элементы И, выходы которых подключены к первому и второму входу блока соответственно, первый информационный вход блока подключен к первому информационному входу коммутатора и входу элемента НЕ, выход которого соединенс вторым информационным входом коммутатора, управляющий вход которого соединен с вторым информационным входом блока и первыми входами первого и второго элементов И соответственно, вторые входы которых объединены и подключены к выходу триггера и входу переноса сумматора,. выход которого соединен с входом триггера, первый информационный вход сумматора соеди нен с выходом коммутатора, а второй информационный вход сумматора " с управляющим входом блока.Четвертый арифметико-логический блок содержит четыре элемента НЕ, два 15 сумматора, два триггера, два регист.ра сдвига, коммутатор, дваэлемента ИЛИ, два элемента И, блок элементов НЕ, блок элементов И и блок элементов И-НЕ, выход которого соединен 20 с первыми входами первого и второго элементов И, второй вход первого элемента И соединен с первым входом первого элемента ИЛИ и выходом первого элемента НЕ, выход которого со з единен с выходом первого триггера и входом переноса первого сумматора, Выход переноса которого соединен с входом триггера, а информационный выход - с входом первого регистра Зв сдвига, выход которого соединен с , первым входом коммутатора, второй вход которого соединен с выходом второго регистра сдвига, вход которого соединен с информационным выходом второго сумматора, выход переноса которого соединен с входом второго триггера, выход которого соединен с входом второго элемента НЕ и входом переноса второго сумматора, щ первый информационный вход которого соединен с выходом третьего элемента НЕ, вход которого соединен с первым информационным входом блока И,. первым информационным входом первого сумматора, второй информационный вход которого соединен с выходом четвертого элемента НЕ, вход которого соединен с вторым информационным входом блока и вторым информационным входом второго сумматора, выход коммутатора подключен к входу блока элементов НЕ, выход которого соединен с входом блока элементов И-НЕ и входом блока элементов И, выход которого соединен с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, выход второго элемента НЕ соединен с третьим входом коммутатора, вторыми входами второго элемента И и второго элемента ИЛИ и выходом блока, выходы первого и второго элементов И подключены к выходу блока.На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - схема узла 2 коммутации; на фиг. 3 - схема узла 3 коммутации; на фиг. 4 - схема арифметико-логичес. кого блока 18; на фиг. 5 - схема арифметика-логического блока 19; на фиг, 6 - схема арифметико-логического блока 20; на фиг. 7 - схема ариф- . метико-логического блока 21.Устройство для побитовой обработки чисел, представленных в Форме с плавающей запятой, содержит блок 1 памяти, узел 2 коммутации, предназначенный для управления сдвигом, сдвиговые регистры 3, блок 4 памяти, узел 5 коммутации, предназначенный для нормализации, и процессоры 6, каждый из которых состоит из сдвиговых регистров 7- 13, коммутаторов 14- 17, арифметико-логических блоков 18"21, шифратора 22, формирователя знака 23.Узел 2 коммутации содержит коммутаторы 24, образующие первый ярус, и коммутаторы 25, образующие второй ярус. Соединение разрядных шин сдвигаемого чила А (а 1 а аа,) с входами коммутаторов 24 и выходов коммутаторов 24 с входами коммутаторов 25 показано в табл. 1 и 2.Узел коммутации 5 содержит элементы НЕ 26, входы которых соединены с двенадцатью старшими разрядами нормализуемого числа, а выходы элементов НЕ 26 соединены с входами элементов И 27, выходы которых соединены с входами элементов НЕ 28,Выход первого элемента И 27, кроме того, соединен с первыми входами элементов И 29-31. Выход второго эле-. мента И 27 соединен также с вторыми входами элементов И 30 и 31, а выход третьего элемента И 27 соединен также с третьим входом элемента И 31. Выходы второго и третьего элементов НЕ 28 соединены с вторым и третьим входами соответственно элементов И 29 и 30.Выходы первого элемента НЕ 28 и выходы элементов И 29-31 соединены с входами шифратора 32, выходы которо. го соединены с управляющими входами коммутаторов 33, составляющих первый ярус узла 5 коммутации.Выходы первых трех коммутаторов 33 первого яруса соединены с входами эле9 938284 10ность октав, равную единице и боль- , в котором на основе анализа знаков шую единицы., исходных чисел и кода операции ( поИэ этих сигналов в том же блоке, 18 ступают из шифратора 22 ) производит- вырабатываются управляющие сигналы ся формирование знака результата и для коммутаторов 14 и 15 одновремен-последующая его передача через коммуно. татор 16 для записи в блок 4 памяти.После того, как из блока 4 памяти Этот же сигнал переполнения посту- последний (старший) разряд октав по- пает в арифметико-логический блок 20. ступыл в каждом процессоре 6 на Если в данном процессоре 6 выполняблок 18, где произошла описанная об- ф ется операция сложения, в случае ра" работка, начинается чтение мантисс венства единице сигнала переполнения (тоже с. младших разрядов) из блока 4, в блоке 20 производится прибавление Мантиссы поступают на входы процессо- единицы к большей октаве, поступающей ров 6 и далее вталкиваются в сдвиго-в блок 20 из сдвигового регистра 13. вые регистры 7 и 8, имеющие 2 раз- з- Результирующая октава иэ блока 20 рядов. После заполнения сдвиговых через коммутатор 16 передается длярегистров 7 и 8 чтение мантисс из записи. в блок 4 памяти. Если же в реблока 4 продолжается, но теперь на- зультате сложения мантисс в сдвиговом чинают работать коммутаторы 14 и 15, регистре 9 получится нулевая инфорВ случае равенства октав через э мация, сработает указанная схема по коммутаторы 14 и 15 проходит инфор-, обнаружению этого Факта (не показамация из сдвиговых .регистров: 7 и 8. на ) и по ее сигналу в блоке 20 проЕсли разность октав равна единице, изойдет вычитание единицы из октавы, мантисса, соответствующая большей поступающей из сдвигового регистра 13, октаве, проходит через коммутаторы 14 э В остальных случаях, ( т.е. при сложеили 15 из сдвигового регистра 7 или, нии без переполнения, при вычитании, соответственно, 8, а другая мантисса октава иэ сдвигового регистра 13 пропроходит через коммутатор 15.или 14 ходит беэ изменения через арифметикопо входу, связанному с входом процес- логический блок 20. сора 6. Таким образом осуществляется зво-псдвиг мантисс на 2 " 1 разрядов. Если После окончания пересылки результи. разность октав больше единицы, через рующей октавы через коммутатор 6 .наодин иэ коммутаторов 14 или 15 про- чинается обработка числа, хранящего- ходит мантисса, соответствующая боль" ся в сдвиговых регистрах 9 и 1 О. Если шей октаве, в то время как другой з при сложении мантисс сигнал переполкоммутатор 15 или 14 закрыт. нения, выработанный в арифметико"лоИнформация с выходов коммутато- гическом блоке 19, равен нулю, реров 14 и 15 поступает на входы ариф- эультирующая мантисса из сдвиговых метико-логического блока .19, где под" регистров 9 и 10 передается последовадействием управляющих сигналов иэ шиф-в тельно разряд за разрядом без изменератора 22 происходит сложение или вы- ния через блок 21 и далее через комчитание. В последнем случае обратный мутатор 16 в блок 4 памяти. Если же код одного иэ операндов формируется этот сигнал переполнения равен единитоже в блоке 19. Результирующее чис- . це, часть мантиссы из сдвигового рело поступает в сдвиговый регистр 9, э гистра 9 передается в блок 4 памяти а после его заполнения вталкивается непосредственно через коммутатор 16, ,в сдвиговый регистр 1 О. После обработ- минуя блок 21. Таким образом, осуки последних (старших ) разрядов ман- ществляется нормализация мантиссы в тисс в арифметико-логическом бло- вправо на 2 п 1 п 1 разрядов с предвариКе 19 Формируются сигналы, указыва- тельным прибавлением единицы к октающие на то, было ли при сложении пе- ве данного результата. Сдвиговый ререполнение или нет, а при вычита- гистр 9 имеет 2 "0 разрядов и после нии - на то, в каком коде (прямом того, как содержимое этого регистра 9 или обратном )получился результат. передано через коммутатор 16, в стар- Кроме того, срабатывает схема ( не по- шие разряды результирующей мантиссы5казана ), которая выявляет нулевую записываются нули. Это достигается информацию в сдвиговомрегистре 9. .блокировкой коммутатора 16 под дейСигнал переполнения иэ блока 19ствием сигнала переполнения и сигна поступает в формирователь 23 знака, .ла сложения (не показано).9382 11В случае Вычитания мантисс сигнал переполнения иэ блока 19 является циклическим переносом. Зтот сиг"нал поступает в арифметика-логический блок 21, где осуществляется егосложение с мантиссой, поступающей иэсдвиговых регистров 10 и 9. Зтот жесигнал. циклического переноса определяет в каком коде прямом или обратном) выдается результат из блока 21 0в коммутатор 16,Вычисления в процессорах 6 организованы по конвейерному принципу,Очередная пара исходных чисел начи"нает поступать в процессор 6 сразу же 15как только в него поступит последНий бит предыдущих исходных чисел.Точно так же на выходе процессора 6Формируется один результат обработ- .ки за другим. Синхронизация работы эрсоставных частей процессоров 6 осу"ществляется общими временными строба"ми от устройства управления и триггерами задержки, входящими в узлы каж"дого процессора (,не показаны). 23При выполнении логических операцийнад исходными числами информация изблока 4 памяти поступает на входысдвиговых регистров 7 и 8. Далее онапередается через коммутаторы 14 и 15 вна арифметико-логический блок, гдеи производится необходимая логичес"кая обработка. Результирующее числочерез сдвиговые регистры 9 и 10 иблок 21 передается на коммутатор 16и через него далее на выход процессора 6,Из описанного примера работы вычислительной системы видно, каким образом достигается экономия времени при 84 12обработке информации, Преобразование чисел, представленных в форме с плавающей запятой, проведенное в узле 2 и на сдвиговых регистрах 3, по" зволяет упростить вычислительный процесс над числами, а именно, изъять две очень сложные процедуры выравнивания порядков ( и связанного с этим сдвига одной из мантисс) и нормализации результата с коррекцией результирующего порядка. Трудность этих процедур связана помимо аппаратурных затрат с различной временной протяженностью их выполнения в различ" ных процессорах 6 из"за различного количества сдвигов, что затрудняет процесс синхронизации вычислений во всех процессорах 6. Форма представления чисел, принятая в предложенной вычислительной системе позволяет не только ускорить вычисления, но и упростить алгоритмы выполнения операций так, что все микрооперации в любой момент времени одинаковы для всех процессоров 6, Тем самым создается возможность убрать местное управление в процессорах 6 и управлять от общего для всех устройства управления (не показано).Следует также отметить, что обмен информацией между блоком 1 памяти и блоком 4 памяти не требует дополнительного времени и может происходить одновременно с работой оперативного запоминающего устройства 4 с процессо рами 6, Пока одни области блока памяти 4 заняты работой с процессорами 6, другие области этого блока 4 могут обмениваться информацией с блоком 1 памяти.Таблица 1-го яруса на 1ах коммутаторорусав т е е с Мну ТаблиФаееаееюе Выходкоммутаторо Ра 1 ю деление выходо руса на 1-М вх ммутаторов 2-гяруса м аспределение разряд на 1-М входах ком утаторов 1-го яруса1-го ярус дах яр 2 3 с сф17 18Продолжение табл. 3938284 аспределение разрядовна 1-4 входах комутаторов 1-го яруса 2 3 4 1 ) руса 1 2 3а 1 12 13 14 14 16 СМЬ С 0 С 4 СВ Ь 16 16 Ь 16 ЬМВ Ь 19 аь 18 Сщ Сфц СЦ С 0 Ь 18 Ь" "Гам 19 С, С С, Сь.,д И 1 Ьи Таблица

СмотретьЗаявка

3214818, 09.09.1980

ПРЕДПРИЯТИЕ ПЯ М-5489

КАРЦЕВ МИХАИЛ АЛЕКСАНДРОВИЧ, ЛЕЩИНСКИЙ ВЛАДИМИР ПЕТРОВИЧ, ЛУШПИН ЛЕОНИД ИВАНОВИЧ, МИЛЛЕР ЛЕОНИД ЯКОВЛЕВИЧ, ПАХУНОВ ВЛАДИМИР НИКИТОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: запятой, плавающей, побитовой, представленных, форме, чисел

Опубликовано: 23.06.1982

Код ссылки

<a href="https://patents.su/18-938284-ustrojjstvo-dlya-pobitovojj-obrabotki-chisel-predstavlennykh-v-forme-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для побитовой обработки чисел, представленных в форме с плавающей запятой</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Логическое устройство

Случайный патент: Рубанок