Сумматор кодов фибоначчи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 732864

Автор: Стахов

Текст

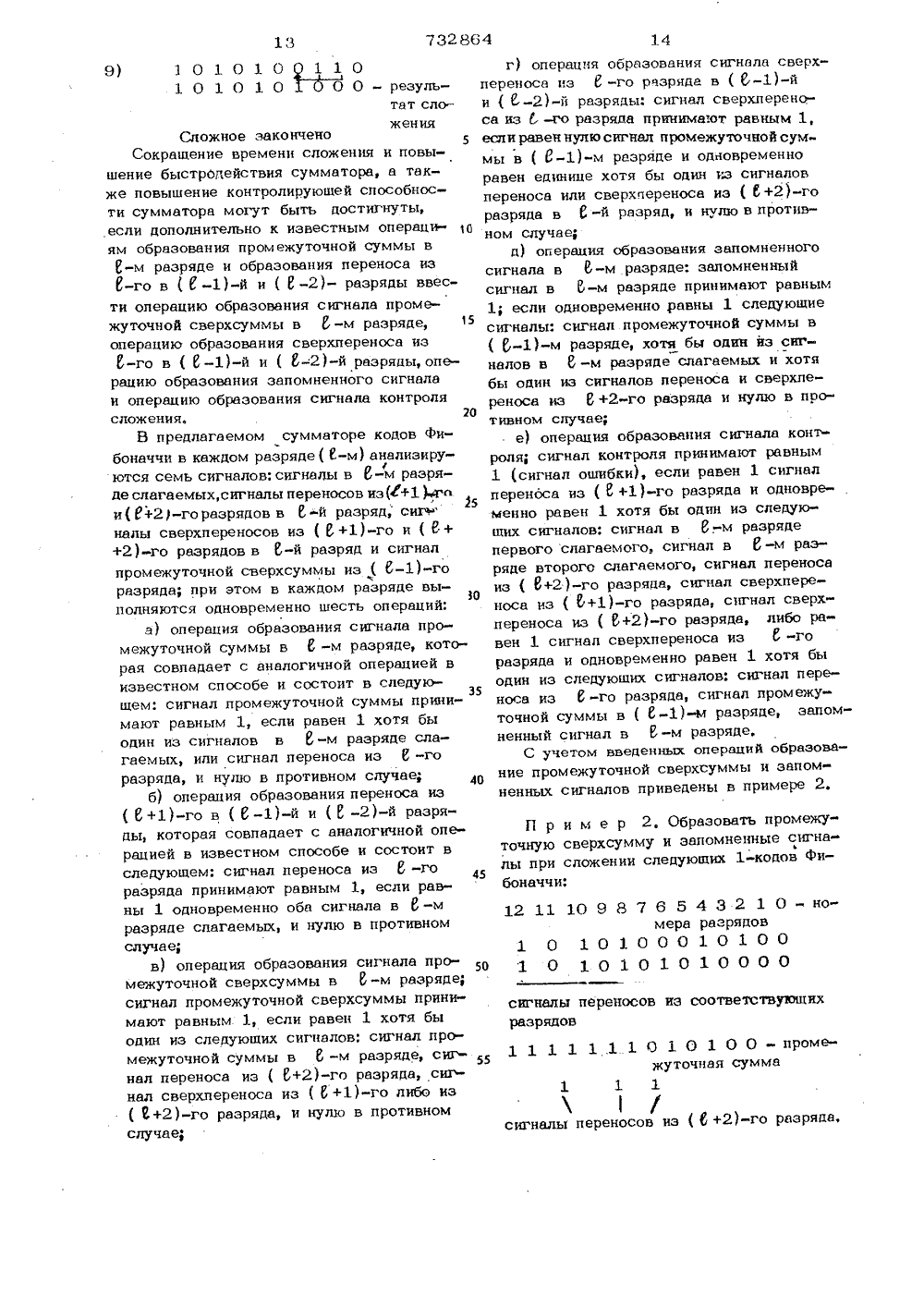

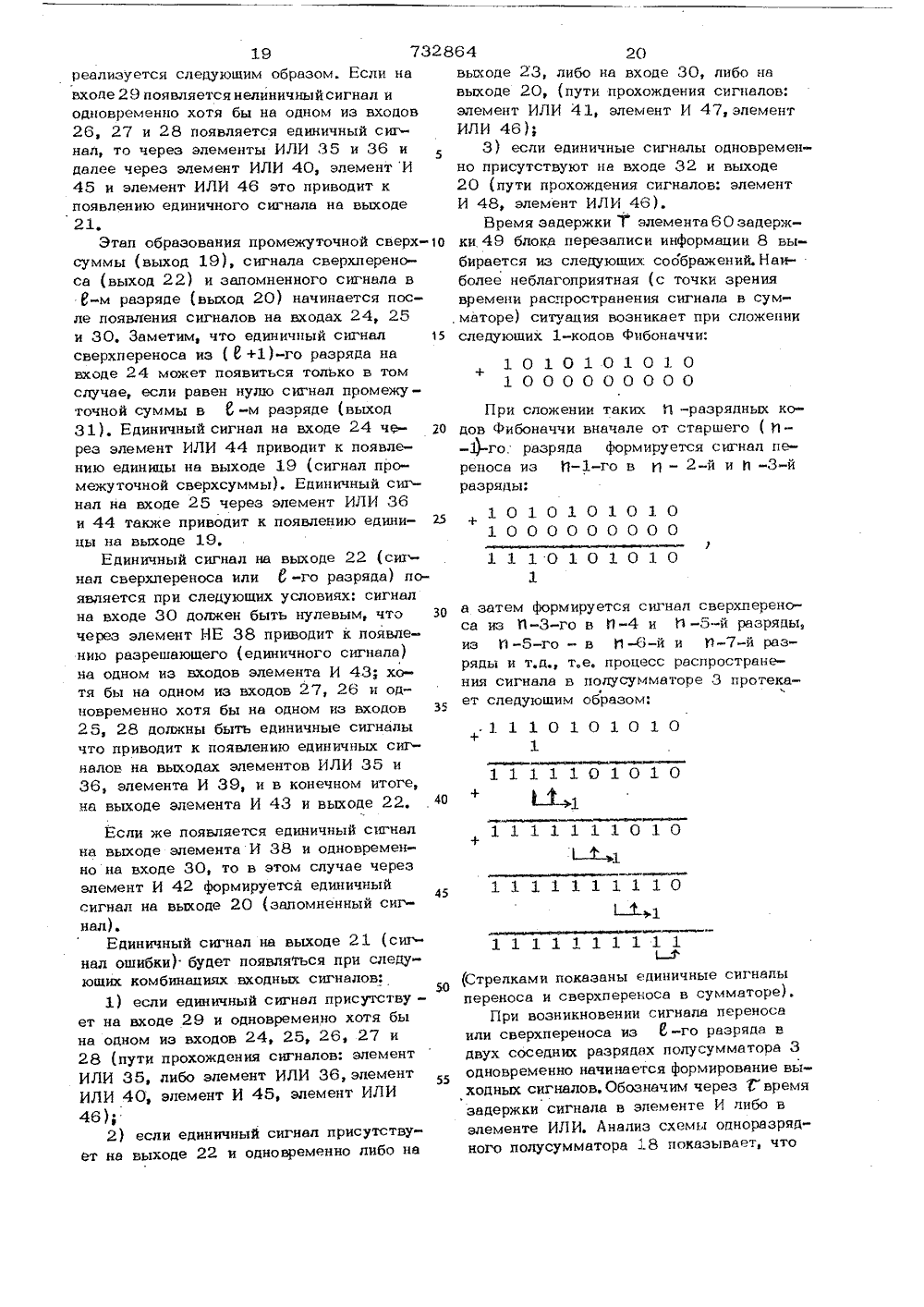

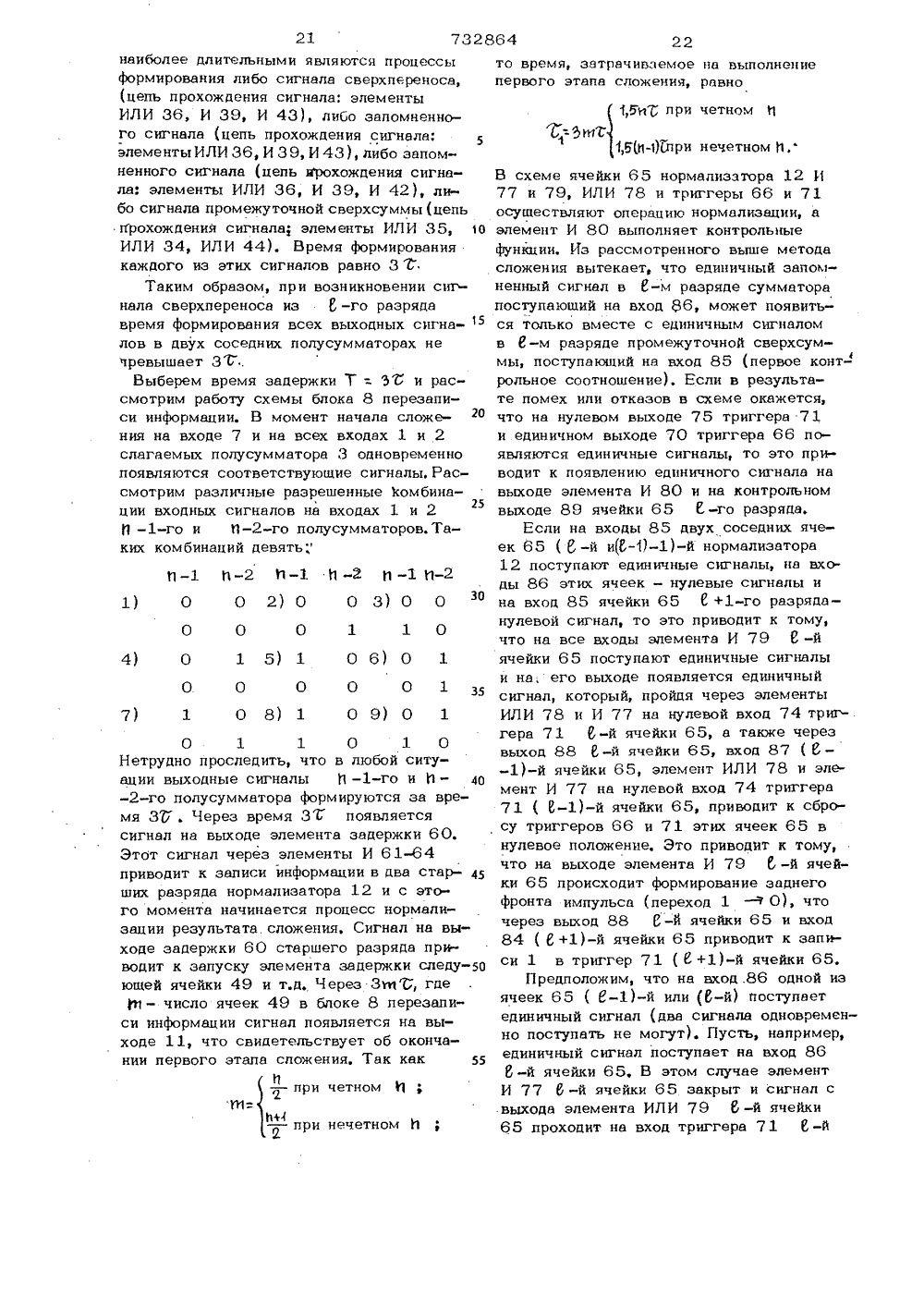

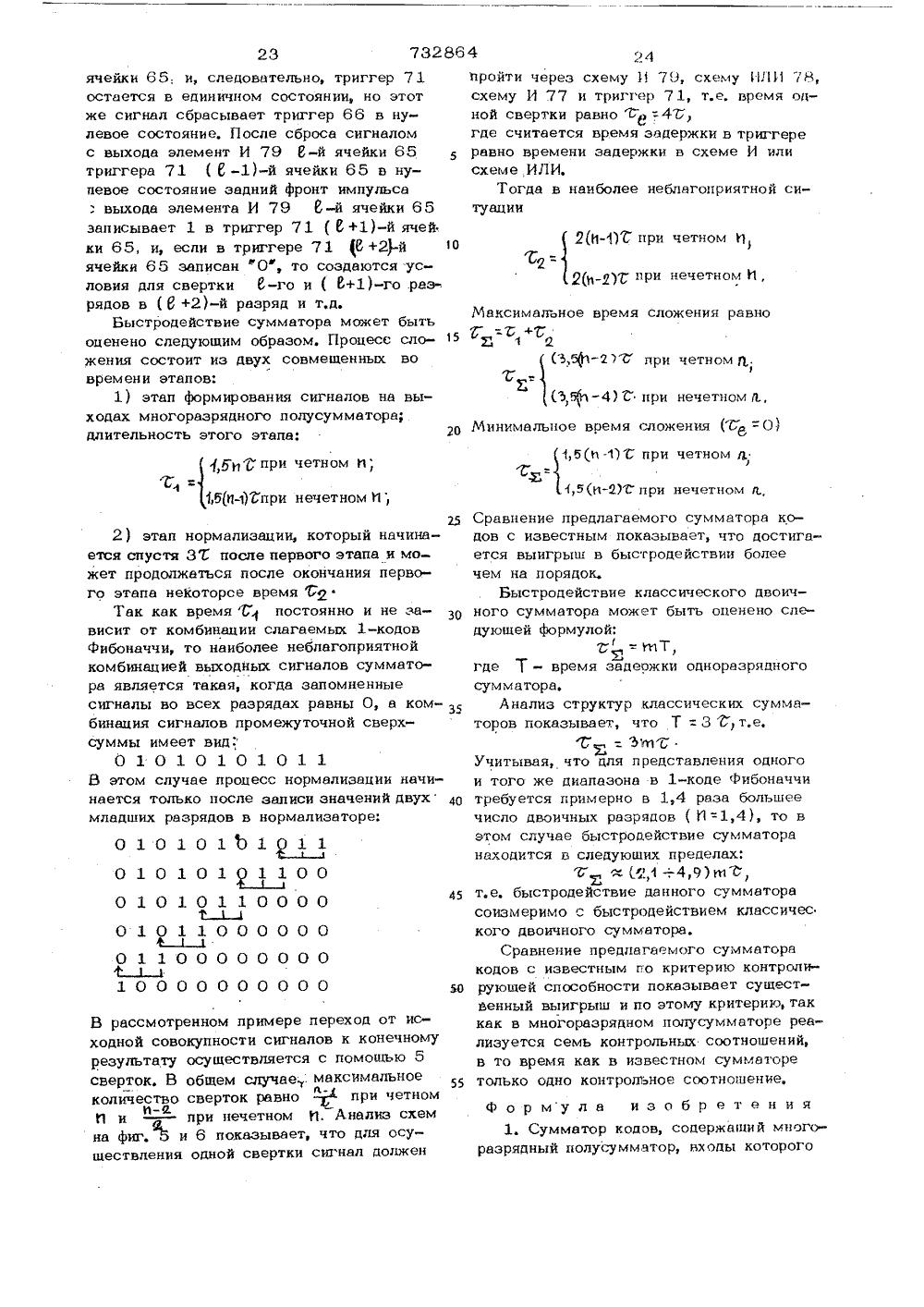

Союз СоветскикСоциалмстическикРеспублии ОП ИСАНИ ЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 732864 1 3) Заявлено 22.12.76 (2 2432391 51)М. Кд,Г 7/3 присоелинением заявки Ж дерстееииый комитет СССР 23)Приоритет и изобретеиийоткрытий Опубликовано 05 5.80. Бюллетень М 17 ия описания 08.05,80(71) Заявите кий институт им,ганрогский радио алмы(54 СУММАТОР КОДОВ фИБОНАЧ быстроБель изобретени действия сумматора лируюшей способнос Для достиженияовы и повышение контрои сумматора. той цели сумматортор и блок перезаписиоторого соединены со ния и выходами просодержит нормвлизаинформации, входы входом начала слож олу Изобретение относится к вычислительной технике и может быть использованов арифметическом устройстве БВМ,Известны сумматоры кодов фибоначчи,построенные на основе алгоритма сложения кодов фибоначчи 11, 21 и 3.Недостатком таких сумматоров является большое количество в среднем цикловсложения, что приводит к снижению быстродействия сумматора.Наиболее близким к предлагаемому является сумматор кодов фибоначчи, содержаший многоразрядный полусумматор, входы которого соединены со входами слагаемых сумматора и элемент ИЛИ, выходкоторого подключен к контрольному выходу сумматора 4,Недостатком такого сумматора является большое количество в среднем цикловсложения, что приводит к снижению бысъ ОродейСтвия сумматора, и невысокая контролирующая способность сумматора, .такквк в сумматоре проверяется только одноконтрольное соотношение,межуточной сверхсуммы и запомненных спс налов многоразрядного полусуммвтора, в выходы - со входами нормализаторв, вы ходы нормалиэатора соединены с выходами результата сложения сумматора, окончания сложения сумматора и первым входом элемента ИЛИ, второй вход которого подклю чен к контрольному выходу м(тогоразряд ного полусумматора.К роме этого многоразрядный полусумматор содержит П однотипных одноразряа. ных полусумматоров ( т 1 - количество разрядов) и элемент ИЛИ, выход которого подключен к контрольному выходу многоразрядного полусумматора, а входы - к контрольным выходам одноразрядных п сумматоров, входы слагаемых-го од(Стрелками показаны единичные сигналы переноса и сверхпереноса в сумматоре),При возникновении сигнала переноса или сверхпереноса из 6 -го разряда в двух соседних разрядах полусумматора 3 одновременно начинается формирование выходных сигналов, Обозначим через Г время задержки сигнала в элементе И либо в элементе ИЛИ, Анализ схемы одноразрядного полусумматора 18 показывает, что 19 7328реализуется следующим образом. Если навхоле 29 появляется нелиничный сигнал иодновременно хотя бы на одном из входов26, 27 и 28 появляется единичный сигнал, то через элементы ИЛИ 35 и 36 идалее через элемент ИЛИ 40, элемент И45 и элемент ИЛИ 46 это приводит кпоявлению единичного сигнала на выходе21.Этап образования промежуточной сверхосуммы (выход 19), сигнала сверхпереноса (выход 22) и запомненного сигнала в8-м разряде (выход 20) начинается после появления сигналов на входах 24, 25и 30, Заметим, что единичный сигнал 15сверхпереноса из ( 8 +1)-го разряда навходе 24 может появиться только в томслучае, если равен нулю сигнал промежуточной суммы в ь -м разряде (выход31). Единичный сигнал на входе 24 через элемент ИЛИ 44 приводит к появлению единицы на выходе 19 (сигнал промежуточной сверхсуммы). Единичный сигнал на входе 25 через элемент ИЛИ 36и 44 также приводит к появлению единицы на выходе 19,Единичный сигнал на выходе 22 (сигнал сверхпереноса или 8 -го разряда) появляется при следующих условиях: сигнална входе 30 должен быть нулевым, что 30через элемент НЕ 38 приводит к появлению разрешающего (единичного сигнала)на одном из входов элемента И 43; хотя бы на одном из входов 27, 26 и одновременно хотя бы на одном из входов зБ25, 28 должны быть единичные сигналычто приводит к появлению единичных сигналов на выходах элементов ИЛИ 35 и36, элемента И 39, и в конечном итоге,на выходе элемента И 43 и выходе 22, 40Если же появляется единичный сигнална выходе элемента И 38 и одновременно на входе 30, то в этом случае черезэлемент И 42 формируется единичныйсигнал на выходе 20 (запомненный сигнал).Единичный сигнал на выходе 21 (сщнал ошибки) будет появлягься при следующих комбинациях входных сигналов:Я)1) если единичный сигнал присутствует на входе 29 и одновременно хотя бына одном из входов 24, 25, 26, 27 и28 (пути прохождения сигналов: элементИЛИ 35, либо элемент ИЛИ 36, элементИЛИ 40, элемент И 45, элемент ИЛИ46);2) если единичный сигнал присутствует на выходе 22 и одновременно либо на 64 20выходе 23, либо на входе 30, либо на выходе 20, (пути прохождения сигналов: элемент ИЛИ 41, элемент И 47, элемент ИЛИ 46) 33) если единичные сигналы одновременно присутствуют на входе 32 и выходе 20 (пути прохождения сигналов: элемент И 48, элемент ИЛИ 46).Время задержки Т элемента 60 задержки 49 блока перезаписи информации 8 выбирается из следующих соображений. Наиболее неблагоприятная (с точки зрения времени распространения сигнала в сумматоре) ситуация возникает при сложении следующих 1-кодов фибоначчи: При сложении таких ьь -разрядных кодов фибоначчи вначале от старшего ( п - -3)-го. разряда формируется сигнал переноса из и-го в И - 2-й и и -3-й разряды: а затем формируется сигнал сверхпереноса из И-го в Ии И -5-й разряды, из ь 1-5-го - в И -6-й и И-й разряды и т,д т,е, процесс распространения сигнала в полусумматоре 3 протекац ет следующим образом:1) 0 0 1 1 0 0 0 4) 0 1 5) 1 0 6) 0 1 0 0 0 0 1 з 5 7) 1 0 8) 1 0 9) 0 1 0 1 1 0 1 0 Нетрудно проследить, что в любой ситуации выходные сигналы П -1-го и й -2-го полусумматора формируются за время 37, Через время 3 Г появляется сигнал на выходе элемента задержки 60. Этот сигнал через элементы И 61-64 приводит к записи информации В двв ста)45 ших разряда нормализатора 12 и с этого момента начинается процесс нормализации результата. сложения, Сигнал на выходе задержки 60 старшего разряда приводит к запуску элемента задержки следующей ячейки 49 и т.д. Через Змь; где т 1- число ячеек 49 в блоке 8 перезаписи информации сигнал появляется на выходе 11, что свидетельствует об окончании первого этапа сложения, Так квк 55И- при четном И2Я=Ь+4- при нечетном й2Э наиболее длительными являются процессы формирования либо сигнала сверхпереноса, (цепь прохождения сигнала: элементы ИЛИ 36, И 39, И 43), либо запомненного сигнала (цепь прохождения сигнала;элементы ИЛИ 36, И 39, И 43), либо запомненного сигнала (цепь врохождения сигнала: элементы ИЛИ 36, И 39, И 42), либо сигнала промежуточной сверхсуммы (цепь прохождения сигнала; элементы ИЛИ 35, 1 о ИЛИ 34, ИЛИ 44). Время формирования каждого иэ этих сигналов равно 3 TТаким образом, при возникновении сит- нала сверхпереноса из ь -го разряда время формирования всех выходных сигна лов в двух соседних полусумматорах не чревышвет 3 ГВыберем время задержки Т = 5 б и рассмотрим работу схемы блока 8 перезаписи информации. В момент начала сложения на входе 7 и на всех входах 1 и 2 слагаемых полусумматорв 3 одновременно появляются соответствующие сигналы, Рассмотрим различные разрешенные комбинации входных сигналов на входах 1 и 2 Д -1-го и И-го полусумматоров. Таких комбинаций девять то время, затрачиваемое на выполнениепервого этапа сложения, равно 1,Ги при четном=3 юС 1 ЯИ)упри нечетном Н,В схеме ячейки 65 нормалиэатора 12 И 77 и 79, ИЛИ 78 и триггеры 66 и 71 осуществляют операцию нормализации, в элемент И 80 выполняет контрольные функции. Из рассмотренного выше метода сложения вытекает, что единичный запомненный сигнал в 8-м разряде сумматора поступающий на вход 86, может появиться только вместе с единичным сигналом в 0-м разряде промежуточной сверхсуммы, поступаюший на вход 85 (первое конт- рольное соотношение). Если в результате помех или отказов в схеме окажется, что на нулевом выходе 75 триггера 71 и единичном выходе 70 триггера 66 появляются единичные сигналы, то это приводит к появлению единичного сигнала на выходе элемента И 80 и на контрольном выходе 89 ячейки 65 Ю-го разряда,Если на входы 85 двух соседних ячеек 65 ( -й и(ь-т)-1)-й нормализвтора 12 поступают единичные сигналы, на входы 86 этих ячеек - нулевые сигналы и на вход 85 ячейки 65 6+1-го разряда- нулевой сигнал, то это приводит к тому, что на все входы элемента И 79 В -й ячейки 65 поступают единичные сигналы и на, его выходе появляется единичный сигнал, который, пройдя через элементы ИЛИ 78 и И 77 нв нулевой вход 74 триггера 7 1 6 -й ячейки 65, а также через выход 88 6-й ячейки 65, вход 87 ( Ю- -1)-й ячейки 65, элемент ИЛИ 78 и элемент И 77 на нулевой вход 74 триггера 71 ( 1-1)-й ячейки 65, приводит к сбросу триггеров 66 и 71 этих ячеек 65 в нулевое положение, Это приводит к тому, что на выходе элемента И 79 ь-й ячейки 65 происходит формирование заднего фронта импульса (переход 1 в0), что через выход 88 ь-й ячейки 65 и вход 84 ( 6+1)-й ячейки 65 приводит к записи 1 в триггер 71 ( 6+1)-й ячейки 65.Предположим, что на вход.86 одной из ячеек 65 ( Ы)-й или (В-й) поступает единичный сигнал (два сигнала одновременно поступать не могут). Пусть, например, единичный сигнал поступает нв вход 86 3-й ячейки 65, В этом случае элемент И 77 6-й ячейки 65 закрыт и сигнал с .выхода элемента ИЛИ 79 6-й ячейки 65 проходит на вход триггера 71 ь-й252) этап нормализации, который начинается спустя 37 после первого этапа и мо жет продолжаться после окончания первого этапа неКоторсе время дТак как время Г постоянно и не зависит от комбинации слагаемых 1-кодов Фибонеччи, то наиболее неблагоприятной комбинацией выходных сигналов сумматора является такая, когда запомненные сигналы во всех разрядах равны О, а комбинация сигналов промежуточной сверх- суммы имеет вид,"01010101011В этом случае процесс нормализации начинается только после записи значений двух40 младших разрядов в нормвлизаторе.010101 Ь 1)11О 1 О 1 О 11 ОО01010110000Й 301011000000Фл01 100000000 10000000000 В рассмотренном примере переход от исходной совокупности сигналов к конечному результату осуществляется с помощью 5 сверток. В общем случае максимальное количество сверток равно - при четном Л и при нечетном Л. Анализ схем нв фиг. % и 6 показывает, что для осуществления одной свертки сигнал должен ячейки 65 и, следовательно, триггер 7 1 остается в единичном состоянии, но этот же сигнал сбрасывает триггер 66 в нулевое состояние, После сбросе сигналом с выхода элемент И 79 0-й ячейки 65 триггера 71 ( ( -1)-й ячейки 65 в нупевое состояние задний фронт импульсе : выхода элемента И 79 6-й ячейки 65 записывает 1 в триггер 71 ( 6+1)-й ячей ки 65, и, если в триггере 71 (6+2-й О ячейки 65 записан 0, то создаются.условия для свертки 6-го и ( 6+1)-го раз-. рядов в (+2)-й разряд и т,д.Быстродействие сумматора может быть оценено следующим образом, Процесс сло жения состоит из двух совмещенных во времени этапов:1) этап формирования сигналов на выходах многоразрядного полусумматоре;длительность этого этапа: 204г пройти через схему ) 79, схему И 78 схему И 77 и триггер 71, т.е. время одной свертки равно=. 4 Г, где считается время задержки в триггере равно времени задержки в схеме И или схеме,ИЛИ.Тогда в наиболее неблагоприятной ситуации2(И-ЯГ при четном Л ГавД( ) при нечетном И, Максимальное время сложения равно +ф а(Ъ,ф) С при нечетном а, Минимальное воемя сложения (Г =0) 1 5 (и - 1 С при четном а5 Ь)С при нечетном и Сравнение предлагаемого сумматора кодов с известным показывает, что достигается выигрыш в быстродействии более чем на порядок.Быстродействие классического двоичного сумматора может быть оценено следующей формулой:=Щ, где Г - время зедеожки одноразрядного сумматора,Анализ структур классических сумматоров показывает, что Т = 3 Г т,е,;1;Е Учитывая, что для представления одного и того же диапазоне в 1-коде Фибоначчи требуется примерно в 1,4 резв большее число двоичных разрядов ( И=14) то в этом случае быстродействие сумматора находится в следующих пределах:Г х ЛЧ +49) в С, т,е, быстродействие данного сумметора соизмеримо с быстродействием классичес кого двоичного сумматора.Сравнение предлагаемого сумматора кодов с известным по критерию контролирующей способности показывает существенный выигрыш и по этому критерию, твк как в многоразрядном полусумматоре реализуется семь контрольных соотношений, в то время как в известном сумматоре только одно контрольное соотношение, Формула изобретения1. Сумматор кодов, содержащий многоразрядный полусу мм втор входы которого732864 25соединены с входами слагаемых сумматора и элемент ИЛИ, выход которого подключен к контрольному выходу сумматора, о т л и ч а ю ш и й с я тем, что, с делью повышения быстродействия и контролирующей способности сумматора, он содержит нормализатор и блок перезаписи информации входы которого соединены со входом начала сложения и выходами промежуточной сверхсуммы я запомненных 10 сигналов многоразрядного полусумматора, а выходы - со входами нормализатора, выходы нормализатора соединены с выходами результата сяожения сумматора, окончания сложения сумматора и первым входом элемента ИЛИ, второй вход которого подключен к контрольноМу выходу многоразрядного полусумматора.2, Сумматорпоп. 1,отличаю щ и й с я тем, что многоразрядный полусумматор содержит И однотипных одноразрядных полусумматоров ( П - количество разрядов) и элемент ИЛИ, выход которого подключен к контрольному выходу многоразрядного полусумматора, а входы - к контрольным Выходам одноразрядных полусумматоров входы слагаемых-го одноразрядного полусумматора ( 6=1, , д ) подключены ко входам 6-го разряда многоразрядного полусумЭО матора, выходы промежуточной сверхсуммы и запомненного сигнала 6-го одноразрядного полусумматора подключены к выходам 3 -го разряда промежуточной сверхсуммы и запомненного сигнала мно- З 5 горазрядного полусумматора, выход запомненного сигнала К -го одноразрядного полусумматора подключен ко входу запомненного сигнала ( 3-1)-го однораэрядно 40 го полусумматора, выход переноса ь-го одноразрядного полусумматора подключен ко входу переноса ( 6-1)-го и ( С -2)-го одноразрядных полусумматоров входы переноса 6 -го одноразрядного, полусумма"- 45 тора подключены к выходам переноса ( 3+1)-го и ( 6+2)-го одноразрядных полусумматоров, выход сверхпереноса 6-го одноразрядного полусумматора подключен ко Входам сВерхпереноса ( 6 1) го и 50 ( 8 -2) -го одноразрядных полусумматоров входы сверхпереноса 0 -го одноразрядного полусумматора подключены к выходам сверхперенося (8+1)-го и ( 8+2)-го Одноразрядньзх полусумматороВ Вьход промежуточной суммы О -го одноразрядно-.го полусумматора подключен ко входу промежуточной суммы ( 6+1)-го одноразрядного полусумматора, вход промежуточной 26суммы 8 -го одноразрядного полусумма- тора подключен к выходу промежуточной суммы ( 8 -1)-го одноразрядного полусумматора, выходы переноса, сверхлереноса и промежуточной суммы первого одноразрядного полусумматора подключены ко входам элемента ИЛИ.3, Сумматорпоп.2, о тл ичаю щ и й с, я тем, что одноразрядный полусумматор состоит иэ элементов И, ИЛИ и НЕ, причем вход элемента НЕ соединен со входом промежуточной суммы и первыми входами первого элемента И и первого элемента ИЛИ а Выход - с первым входом второго элемента И, второй вход которого соединен со вторым входом первого элемента И и выходом третьего элемента И, а.выход - с выходом сверхпереноса н первым входом четвертого элемента И, второй вход которого соединен с.выходом первого элемента ИЛИ, а выход - с первым входом второго элемента ИЛИ, выход которого соединен с контрольным выходом, второй вход - с выходом пятого элемента И, а третий вход - с выходом шестого элемента И, первый вход которого соединен с выходом третьего элемента ИЛИ, а второй вход - со входом переноса из ( 0+1)-го разряда и первым входом четвертого элемента ИЛИ, выход которого соединен с выходом промежуточной суммы и первым входом пятого элемента ИЛИ, а второй вход - с первым входом третьего элемента И, первым входом третьего элемента ИЛИ и выходом шестого элемента ИЛИ, первый вход которого соединен со входом первого слагаемого и первым входом седьмого элемента И, а второй вход - со входом второго слагаемого и вторым входом седьмого элемента И, выход которого соединен с выходом переноса и вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, выходом запомненного сигнала и первым входом пятого элемента И, второй вход которого соединен с входом запомненного сигнала, вход сверхпереноса из ( 1+1)-го разряда соединен со вторым входом третьего элемента ИЛИ и вторым, входом пятого элемента ИЛИ, выход которого соединен с Выходом промежуточной сверхсуммы, а третий вход - со вторым входом третьего элемента И, третьим входом третьего элемента ИЛИ и выходом седьмого элемента ИЛИ, первый вход которого соединен со входом переноса из ( 1+2)-го разряда, а второй вход - со27 73286 входом сверхпереноса из ( ь+2)-го разряда,Источники информации,принятые во внимание при экспертизе1, Стахов А. П,Избыточные двоичныепозиционные системы счисления. Сб. Однородные цифровые вычислительные и интегрирующие структуры, вып, 2 Таганрог,1974,4. Сумматорпоп. 1, отлича - ю ш и й с я тем, что блок перезаписи информации состоит из однотипных ячеек по одной на два соседних разряда, начичая с младшего разряда, причем каждая ячейка содержит первый, второй, третий и четвертый входы, соединенные с соот 10 ветствующими выходами промежуточной сверхсуммы и запомненных сигналов соответствующих двух разрядов многоразрядного полусумматора, пятый вход, первый, второй, третий и четвертый выходысое Б диненные с соответствующими входами прс. межуточной сверхсуммы и запомненных сигналов соответствуюших двух разрядов нормализатора, пятый выход, который для всех ячеек, за исключением младшей,сое динен с пятым входом предыдущей ячейки, пятый выход младшей ячейки соединен с выходом блока, а пятый вход старшей ячейки соединен со входом начала сложения блока перезаписи информации, причем 21 каждая ячейка блока перезаписи информации состоит из элементов И и элемента задержки, вход которого соединен с пятым входом ячейки, а выход - с пятым выходом ячейки и с первыми входами перього ЗО второго, третьего и четвертого элементов И, вторые входы которых соединены соответственно с первым, вторым, третьим и четвертым входами ячейки, а выходы соответственно с первым, вторым, третьим ЗБ и четвертым выходами ячейки. 5. Сумматор по и. 1, о т л и ч а ю ш и й с я тем, что нормализатор состоит из однотипных ячеек по числу раз рядов, каждая из которых содержит вход промежуточной сверхсуммы, вход запомненного сигнала, первый, второй, третий и четвертый входы связи, информационный . выход, контрольнЫй выход, первый и второй выходы связи, кроме того нормализатор содержит первый и второй элементы ИЛИ, фильтр, постоянная времени которо го превышает время переходного процесса в нормализаторе, триггер, элемент НЕ и элемент Ивыход которого соединен с выходом конца сложения нормализатора, первый вход - с единичным выходом триттера, второй вход - с выходом элемента НЕ, вход которого соединен с выходом первого элемента ИЛИ и входом фильтра, выход которого соединен с первым входом второго элемента ИЛИ, другие входы которого соединены соответственно с конт 4 28рольными выходами ячеек нормализатора,единичный вход триггера соединен с входом нормализатора, входы первого элемента ИЛИ соединены с соответствуюшимивторыми выходами связи всех ячеек нормализатора, информационные выходы всехячеек нормализатора соединены с выходомрезультата сложения сумматора, второйвыход связи ячейки В -го разряда соединен с четвертым входом связи ячейки(8-1)-го разряда и третьим входом связи ячейки (0+1)-го разряда, первый вход.связи ячейки 1 -го разряда соединен синформационным выходом ячейки ( с,-1) горазряда, второй вход ячейки с, -го разряда соединен с первым выходом связи ячейки ( 6+1)-го разряда, причем каждая "ячейка нормализатора содержит элементИЛИ, первый, второй и третий элементыИ, первый триггер и второй триггер, счетный вход которого соединен с третьимвходом связи, единичный вход - со входомпромежуточной сверхсуммы, нулевой входс выходом первого элемента И ячейкинормализатора, единичный выход - с информационным выходом ячейки нормализатора и первым входом второго элементаИ ячейки нормализатора, нулевой выход -с первым выходом связи ячейки нормализатора и первым входом третьего элемента И ячейки нормализатора, второй входвторого элемента И ячейки нормализато 3ра соединен с первым входом связи ячейки нормализатора, третий вход - со втсрым входом связи ячейки нормализатора,а выход - со вторым выходом связи ипервым входом элемента ИЛИ ячейки нормализатора, второй вход которого соединен с четвертым входом связи ячейкинормализатора, а выход - с первым входом первого элемента И и третьим входомпервого триггера ячейки нормализатора,единичный вход которого соединен со входом запомненного сигнала нулевой выход - со вторым входом первого элемента И ячейки нормализатора, а единичныйвыход - со вторым входом третьего элемента И ячейки нормализатора, выход которого соединен с контрольным выходомячейки нормализатора,73286430Сб. кодирование и передача дискретныхсообщений в системах связи М., ".Наука",1976. 2, Стахов А. П, Использование естественной избыточности Фибоначчиевых" систем счисления для контроля вычислительных систем; фАвтоматика и вычислительная техника", М 6, 1976.3, Стахов А. П. фибоначчиевы" двоичные позиционные системы счисления,5 4. Авторское свидетельство СССР по заявке М 2358578, кл,606 Р 7/50, 03.05.76. (прототип).Составитель 8. Цереэкинактор 3. Шубенко Техред И. Асталош Корректор В, Бутягин каз 15 Тир Госу иал ППП Патент, г. Ужгород, ул. Проектная,54/10 по 13035, аж 751 арствен изобретеЖв Подписноего комитета СССРи открытийушская наб д. 4/573286 3норазрядного полусумматора (= 1, П ) подключены ко входам 8-го разряда многоразрядного полусумматора, выходы промежуточной сверхсуммы и запомненного сигнала 6 -го одноразрядного полусум-матора подключены к выходам -го разряда промежуточной сверхсуммы и запомненного сигнала многоразрядного полусумматора, выход запомненного сигнала 1-го одноразрядного полусумматора подключен 10 ко входу запомненного сигнала ( -1)-го одноразрядного полусумматора, выход переноса 3 -го одноразрядного полусумматора подключен ко входу переноса ( -1)-го и ( -2)-го одноразрядных полусуммато 15 ров, входы переноса-го одноразрядного полусумматора подключены к: выходам переноса (8+1)-го и ( 0+2)-го одноразрядных полусумматоров, выход сверхпереноса -го одноразрядного полусуммвто 20 рв подключен ко входам сверхпереноса ( (;-1)-го и ( 6-2)-го одноразрядных полусумматоров, входы сверхпереноса 0-го одноразрядного полусуммвтора подключены к выходам сверхпереноса ( 6+1)-го и25 ( 1+2)-го одноразрядных полусумматоров, выход промежуточной суммы-го одноразрядного полусумматора подключен ко входу промежуточной суммы ( +1)-го одЗО норазрядного полусумматора, вход промежуточной суммы-го одноразрядного полусуммвтора подключен к выходу промежуточной суммы ( 6-1)-го одноразрядного полусумматора, выходы переноса, сверхпереноса и промежуточной суммы первого одноразрядного полусумматорв подключены ко входам элемента ИЛИ. При этом одноразрядный полусумматор состоит из элементов И, ИЛИ и НЕ, причем вход элемента НЕ соединен со входом промежуточной суммы и пеовыми вхо.дами первого элемента И и первого элемента ИЛИ, а выход - с первым входом второго элемента И, второй вход которо 45 го соединен со вторым входом первого элемента И и выходом третьего элемента И, а выход - с выходом сверхпереноса итпервым входом четвертого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - с первым входом второго элемента ИЛИ, выход которого соединен с контрольным выходом, второй вход - с выходом пятого элемента И, в третий вход - с выходом шестого элемента И, первый вход которого соединен с выходом третьего элемента ИЛИ, в второй вход - со входом пе:.- носа из ( +1)-го разряда и первым входом четвертого элемента ИЛИ, вькод которого соединен с выходом промежуточнойсуммы и первым входом пятого элемента4ИЛИа второй вход - с первым входомтретьего элемента И, первым входом третьего элемента ИЛИ и выходом шестогоэлемента ИЛИ, первый вход которого соединен со входом первого слагаемого ипервым входом седьмого элемента И, авторой вход - со входом второго слагаемого и вторым входом седьмого элемента И, выход которого соединен с выходомпереноса и вторым входом первого элемента ИЛИ, третий вход которого соединен свыходом первого элемента И, выходомзапомненного сигнала и первым входомпятого элемента И, второй вход которогосоединен с входом запомненного сигнала,вход сверхпереноса из ( 0+1)-го разрядасоединен со вторым входом третьего элемента ИЛИ и вторым входом пятого элемента ИЛИ, выход которого соединен свыходом промежуточной сверхсуммы, атретий вход - со вторым входом третьегоэлемента И, третьим входом третьего элемента ИЛИ и выходом седьмого элементаИЛИ, первый вход которого соединен совходом переноса из ( 1+2)-го разряда, в .второй вход - со входом сверхпереносаиз (8+2)-го разряда,Кроме того, блок перезаписи информации состоит иэ однотипных ячеек по одной нв два соседних разряда, начиная смладшего разряда, причем каждая ячейкасодержит первый, второй, третий и четвертый входы, соединенные с соответствующими выходами промежуточной сверхсуммы и запомненных сигналов соответствующих двух разрядов многоразрядного полусумматора, пятый вход, первый, второй,третий и четвертый выходы, соединенныес соответствующими входами промежуточной сверхсуммы и запомненных сигналовсоответствующих двух разрядов нормализатора, пятый выход, который для ячеек,за исключением младшей, соединен с пятым входом предыдущей ячейки, пятыйвыход младшей ячейки соединен с выходомблока, а пятый вход старшей ячейки соединен со входом начала сложения блокаперезаписи информации, причем каждаяячейка блока перезаписи информации состоит из элементов И и элемента эадержки, вход которого соединен с пятым входом ячейки, а выход - с пятым выходомячейки - и с первыми входами первого,второго, третьего и четвертого элементовИ, вторые входы которых соединены соо 732864 6ветственно с первым, вторым, третьим и четвертым входами ячейки, а выходы со. .ответственно с первым, вторым, третьим и четвертым выходами ячейки.Кроме того, нормализатор состоит из однотипных ячеек по числу разрядов, каждая из которых содержит вход промежуточной сверхсуммы, вход запомненного сигнала, первый, второй, третий и четвертый входы связи, информационный вы ход, контрольный выход, первый и второй выходы связи, кроме того нормализатор содержит первый и второй элементы ИЛИ, фильтр, постоянная времени которого превышает время переходного процесса в нормализаторе, триггер, элемент НЕ и элемент И, выход которого соединен с выходом конца сложения нормализатора, первый вход - с единичным выходом триггера, второй вход - с выходом элемента НЕ, вход которого соединен с выходом первого элемента ИЛИ и входом фильтра, выход которого соединен с первым входом второго элемента ИЛИ, другие входы которого соединены соответственно с контрольными выходами ячеек нормелизатора, единичный вход триггера соединен с входом нормализатора, входы первого элемента ИЛИ соединены с соответствующими вторыми выходами связи всех ячеек нормализатора, информационные выходы всех ячеек нормализатора соединены с выходом результата сложения сумматора, второй выход связи ячейки-го разряда соединен с четвертым входом связи ячейки35 (0-1)-го разряда и третьим входом связи ячейки (0+1)-го разряда, первый вход связи ячейки 6 -го разряда соединен с информационным выходом ячейки ( (; -1)-го40 разряде, второй вход ячейки-го разряда сОединен с первым выходом связи ячейки ( 6+1)-го разряда, причем каждая ячейка нормализетора содержит элемент ИЛИ, первый, второй и третий элементы 45 И, первый триггер и второй триггер, счетный вход которого соединен с третьим входом связи, единичный вход - со входом промежуточной сверхсуммы, нулевой вход - с выходом первого элемента И ячейки нормелизатора, единичный выход - с информационным выходом ячейки нормализатора и первым входом второго элемента И ячейки нормализетора, нулевой выход - с первым выходом связи ячейки нормализетора и первым входом третьего элемента И ячейки нормализетора, второй вход второго элементе И ячейки нормали- затора соединен с первым входом связи ячейки нормализетора, третий вход - свторым входом связи ячейки нормализатора, а выход - со вторым выходом связи и первым входом элемента ИЛИ ячейки нормализеторе, втсрой вход которогосоединен с четвертым входом связи ячеЙи нормализатора, а выход - с первымвходом первого элемента И и третьим входом первого триггера ячейки нормализатора, единичный вход которого соединен со входом запомненного сигнала, нулевой выход - со вторым входом первого элемента И ячейки нормализатора, а единичный выход - со вторым входом третьего элемента И ячейки нормализатора, выход которого соединен с контрольным выходомячейки нормализатора.На фиг, 1 приведена структурная схема сумматора кодов Фибоначчи; на фиг, 2 - схема многоразрядного полусумматоре; на фиг. 3 - схема одноразрядного полусумматора; на фиг, 4-схемабдока перезаписи информации; на фиг. 5- схеме ячейки блоке перезаписи информации; на фиг. 6 - схема нормализатора;на фиг, 7 - схема ячейки нормализатора,Сумматор кодов Фибоначчи содержит вход 1 первого слагаемого, вход 2 второго слагаемого, многорезрядный полусумматор 3, выход 4 промежуточной сверхсуммы, выход 5 запомненных сигналов, контгрольный выход 6 полусумматора 3, вход 7 начала сложения, блок 8 перезаписи ю- формации, выход 9 промежуточной суммы блока 8 перезаписи информации выход 10 запомненных сигналов блока 8 перезаписи инФормации, выход 11 сигнала окончания процесса перезаписи информации, нормализатор 12, выход 13 результата сложения, выход 14 окончания сложения,контрольный выход 15 нормализатора 12,элемент ИЛИ 16, контрольный выход 17сумматора. Входы многоразрядного подусумматора 3 соединены со входами 1 и2 слагаемых, а выходы 4 промежуточнойсверхсуммы и запомненных сигналов 5 подключены к входам 11 блока перезаписи информации, к которым также подключенвход 7 начала сложения. Выходы 9 промежуточной суммы и запомненных сигналов 10 и выход 11 сигнала окончанияпроцесса перезаписи информации блока 8перезаписи информации подключены ко входам нормалиэаторе 12, имеющем выходы 13 результата сложечия, окончания сложения 14 и контрольный выход 15. Контрольный выход 15 нормализатора 12 и контрольный выход 6 полусумматора 3 подклю7 7328чены ко входам элемента ИЛИ 16, выходкоторого подключен к контрольному выходу сумматора 17.Многорвзр 51 дный полусумматор 3 содержит И ( И - количество разрядов) одноразрядных сумматоров 18; . - ый изкоторых имеет ( 3=1, , й ) выход 19+ 1-го разряда, вход 25 сверхпереносаиэ ( 3+2)-г разряда, входы 26 и 27слагаемых, вход 28 переноса из (6+2)-горазряда, вход 29 переноса из ( 1+1)-го 15разряда, вход 30 промежуточной суммы,выход 31 промежуточной суммы, вход 32запомненного сигнала. Многоразрядный полусумматор 3 содержит кроме того элемент ИЛИ 33. 20При этом выходы 19 всех одноразрядных полусумматоров 18 соединены с соответствующими выходами 4 многоразрядного полусумматора 3; выходы 20 всеходноразрядных полусумматоров 18 соединены с соответствуюшими выходами 5 многоразрядного полусумматорв 3; входы26 и 27 всех одноразрядных полусумматоров 18 соединены с соответствуюшимивходами 1 и 2 многоразрядного полусум- З 0матора 3; контрольные выходы 21 всеходноразрядных полусумматоров 18, а также выходы 20, 22, 23 и 31 одноразрядного полусумматора 18 младшего разрядасоединены со входами элемента ИЛИ 33, 35выход которого соединен с контрольнымвыходом 6 многоразрядного полусумматорв 3; выход 22 Одноразрядного полусумматора 18 3-го разряда соединен со входом 24 одноразрядного полусумматора 18 40( 3-1)-го разряда и входом 28 одноразрядного полусуммвторв 18 ( ь)-го разряда; вход 30 одноразрядного полусумма-тора 18 3-го разряда соединен с выходом 31 одноразрядного полусумматорв 4518 ( 6-1)-го разряда; выход 20 одноразрядного полусумматорв 18 6-го разряда соединен со входом 32 одноразрядного ( В)-го разряда,Одноразрядный полусумматор 18. со- Ыдержит алементы ИЛИ 34, 35 и 36, элемент И 37, элемент НЕ 38, элемент И39, элементы ИЛИ 40 и 41, алементыИ 42 и 43, элемент ИЛИ 44, элементИ 45, элемент ИЛИ 46, элементы И 47и 48,При этом вход элемента НЕ 38 соединен со входом 30 промежуточной суммы 64 8и первыми входами элементов ИЛИ 41 и42, в выход - с первым входом элемента И 43, второй вход которого соединенсо вторым входом элемента И 42 и выходом элемента И 39, а выход - с выходом 22 сверхпереноса и входом элементаИ 47, другой вход которого подключен квыходу элемента ИЛИ 41. Выход элемента И 47 подключен ко входу алементаИЛИ 46, выход которого соединен с контрольным выходом 21, второй вход - свыходом элемента И 48, а третий вход -с выходом элемента И 45, первый входкоторого соединен с выходом элементаИЛИ 40, а второй вход - со входом переноса из ( ь+1)-го разряда 29 и первымвходом элемента ИЛИ 34, выход которого соединен с выходом 31 промежуточнойсуммы и первым входом элемента ИЛИ44, в второй вход - с первым входомэлемента И 39, элемента ИЛИ 40 и выходом элемента ИЛИ 35. Входы элемента ИЛИ 35 соединены со входами 26 и27 слагаемых, которые подключены также ко входам элемента И 37, выход которого соединен с выходом 23 переносе ивторым входом элемента.ИЛИ 41, третийвход которого соединен с выходом элемента И 42, выходом 20 запомненного сигнала и первым входом элемента И 48,второй вход которого соединен со входомзапомненного сигнала 32. Вход сверхпереноса из ( +1)-го разряда 24 соединен со вторыми входами элементов ИЛИ40 и 44,Выход элемента ИЛИ 44 подключен квыходу 19 промежуточной сверхсуммы,а третий вход соединен со вторым входомэлемента И 39, третьим входом элемента ИЛИ 40 и выходом элемента ИЛИ 36,первый вход которого соединен со входом28 переноса из ( 6+2)-го разряда, в второй вход - со входом 25 сверхпереносаиз ( б +2)-го оазряда 25,Блок 8 перезаписи информации состоит из однотипных ячеек 49 каждая иэ которых связана с двумя разрядами многоразрядного полусуммвтора 3 и содержитвходы 50, 51, 52, 53 и 54, выходы55, 56, 57 58 и 59, алемент 60 задержки, алементы И 61, 62, 63 и 64.При этом входы 50, 51, 52 и 53 соедииены с соответствуюшими выходами 4промежуточной сверхсуммы и запомненных сигналов 5 двух соседних разрядовмногоразрядного лолусумматора 3; выходы 55, 56, 57 и 58 соединены с вы,ходами 9 промежуточной суммы и эапом732864 10 ненных сигналов соответствующих разрядов блока перезаписи информации 8; выход 54 И-ой ячейки 49 блока 8 перезаписи информации соединен со входом59 п-ой ячейки 49; выход 54 младшей,ячейки 49 соединен с выходом 11сигнала окончания процесса перезаписиинформации, вход 59 старшей ячейки подключен ко входу 7 начала сложения.Вход элемента 60 задержки подключен 10ко входу 59 ячейки 49 а выход - к выФходу 54 ячейки 49 и ко входам элементов И 61, 62, 63 и 64, вторые входыкоторых подключены соответственно ковходам 51, 53, 50 и 52 ячейки 49, а 15выходы - к выходам 57, 55, 58 и 56ячейки 49,Нормализатор 12 содержит И однотипных ячеек 65, каждая из которых включает первый триггер 66, с единичным и нулевым входами 67 и 68 и нулевым и единичным выходами 69 и 70, второй трагер 71, с единичным входом 72, счетнымвходом 73 с запуском по заднему фронтунулевым входом 74, нулевым входом 75,единичным выходом 76, элемент И 77,элемент ИЛИ 78, элементы И 79 и 80;первый вход 81 связи, второй вход 82 связи, первый выход 83 связи, третий вход84 связч, вход 85 промежуточной сверх- ЗОсуммы, вход 86 запомненного сигнала,четвертый вход 87 связи, второй выход88 связи, контрольный выход 89, информационный выход 90.Кроме того, нормализатор 12 содержит элемент ИЛИ 91, фильтр 92, постоянная времени которого превышает время переходного процесса в нормализаторе 12, элемент ИЛИ 93, триггер 94, сединичным входом 95 и единичным выхсдом 96, элемент И 97 и элемент НЕ 98,При этом в нормализаторе 12 второй выход 88 связиячейки 65 6 -го разряда соединен с четвертым входом 87 связи ячейки 65 ( (-1) -го разряда, третьим входом связи 84 ячейки 65 ( 1+1)-го разряда и одним из входов элемента ИЛИ 91; первый вход 81 связи ячейки 65-го разряда соединен с информационным выходом 90 ячейки 65 ( Г)-го разряда; второй вход 82 связи ячейки 65 го разряда соединен с первым выходом 83 связи ячейки 65 ( 1+1)-го разряда; вход 11 сигнала окончания процесса перезаписи информации соединен с единичным входом 95 триггера 94, единичный выход 96 которого соединен с одним из входов элемента И 97; выход элемента ИЛИ 91 соединен со вхсдом элемента НЕ 98, выход которого через элемент И 97 соединен с выходом 14 окончания сложения;Выходы 88 всех ячеек нормализаторасоединены через элемент ИЛИ 91 с фильтром 92 и далее через элемент ИЛИ 93с контрольным выходом 15, Эта цепьсоединений выполняет контрольные функции в нормализаторе, После нормализациина всех выходах 88 должны быть нулевыесигналы. Единичные сигналы на этих выходах появляются кратковременно, покаидет переходной процесс в нормализаторе,фильтр 92 не пропускает кратковременныесигналы на выходах 88 на контрольныйвыход 15. Если же на одном из выходов88 появляется устойчивый единичный сигнал, то это приводит к появлению сигналана контрольном выходе 15.Выход элемента ИЛИ 91 соединен совходом элемента НЕ 98, а через элементИ 97 с выходом 14 окончания сложения.Эта цепь соединений вмете с триггером94 и входом 11 играет следующую роль,Йо тех пор, пока длится переходной,процесс в нормализаторе, на выходе элемента ИЛИ 91 будет единичный сигнал, который через элемент НЕ 96 запрещаетпоявление единичного сигнала на выходе14. Как только на входе 11 появляетсяединичный сигнал (что свидетельствуетоб окончании первого этапа и перезаписиинформации в нормализатор 12) он приводит к переходу триггера 94 в единичноесостояние и появлению разрешающего сигнала на соответствующем входе элементаИ 97. После окончания переходного процесса в нормализаторе на выходе 14 появляется единичный сигнал. При устойчивом отказе нормализатора 12 на выходе15 единичный (разрешающий) сигнал появиться не может,В каждой ячейке нормализатора 65 триггер 71 своим счетным входом 73 подключен к третьему входу 84 связи, единичным входом 72 - ко входу 85 промежуточной сверхсуммы, нулевым входом 74 - к выходу элемента И 77. Единичный выход 76 триггера 71 подключен к информационному выходу 90 и к входу элемента И 79, а нулевой выход 75 - к первому выходу 83 связи и входу элемента И 80, другой вход которого подключен к единичному выходу 70 триггера 66, а выход - к контрольному выходу 89. Второй и третий входы элемента И 79 подключены соответственно к первому и второму входам 81 и 82 связи, а выход -64 12налом переноса из ( , +2)-го разряда, Операция образования запомненных сигналов по существу совпадает с операцией образования переносов;г) операция контроля сложения, Сигнал контроля сложения в 8 -м разряде равен 1, если одновременно равны 1 сигналы переносов .из ( 6+1)-го и ( О +2 )-го разрядов.2. Промежуточная сумма приводится к нормальной форме и над нормальным кодом фибоначчи промежуточной суммы и комбинацией запомненных сигналов выполняют п. 1, 2 алгоритма до образования нулевой комбинации запомненных сигналов,П р и м е р 1. Сложить два числа 46 и 41 в 1 - коде фибоначчи.1. Представление чисел 46 и 41 в нормальных 1 - кодах фибоначчи: 1) 34 21 13 8 5 3 2 1 1 46=1 0 0 1 0 1 0 1 0 41=1 0 . 0 0 1 0 1 0 02,Выполнение п, 1 алгоритма: 2) 100101010+100010100 Так как двух единичных переносов одновременно в один разряд не произошло, то . по и. 1 алгоритма выполнен правильно,3. Выполнение п, 2 алгоритма (нормализация промежуточной суммы):- Д1010010011101001010010 4) ОО 01000010 6) 1010010010 0000010000 1010100110 11 7328ко второму выходу 88 связи и входу элемента ИЛИ 78, другой вход которогосоединен с четвертым входом 87, связи,а выход - со входом элемента И 77 инулевым входом 68 триггера 66, единичный вход 67 которого соединен со входом 86 запомненного сигнала, а нулевойвыход 69 - с другим входом элементаИ 77.Существо алгоритма сложения кодов 10фибоначчи состоит в следующем.Слагаемые числа представляются в виде нормальных кодов фибоначчи (в нормальном коде фибоначчи две единицы подряд в коде не встречаются) и затем над 15нормальными кодами фибоначчи осуществляются следующие операции.1. Образование промежуточной суммы,переносов, запомненных сигналов и сигналов контроля сложения в каждом разряде, 20Сигнал 6-го разряда промежуточной суммы и сигналы переносов из-го разря-да в ( К)ый и ( Я)-й разряды образуются на основе следующей таблицы сложения одноразрядных чисел в коде фибо 25наччи.О+ 0 = 0 110111110О+ О = 1 110= 11 + 1 = 111ЗОВ указанном алгоритме сложения сигналпереноса из-го разряда в ( 6 -1)-йразряд сразу же помещается в ( 8-1-)йразряд промежуточной суммы, а сигнал переноса в (8 -2)-й разряд является запомненным сигналом в (0-2)-м разряде.Таким образом, в процессе сложенияв каждом разряде ( 5-м) анализируютсячетыре сигнала; сигналы в о -м Разряде слагаемых и сигналы переноса из( 5+1)-го и ( 1+2)-го разрядов в 6 -йразряд, При этом одновременно выполняется четыре операции;5) 10 111( 01а) операция образования сигнала про111001010 10 10010межуточной суммы, Сигнал промежуточной суммы в 6 -м разряде принимаетсяравном 1, если равен 1 хотя бы один изсигналов в К-м разряде слагаемых илисигнал переноса иэ ( 8 +1)-го разряда, 1010011013и нулю в противном случае; 1б) операция образования сигнала переноса из 3-го разряда. Сигнал переноса 7) 1 0 1 0 1 0 1 Оиэ -го разряда принимается равным 1, 101010 010если равны 1 одновременно оба сигналав 3 -м разряде слагаемых, 8) 1010100010. в) операция образования запомненного 0000000100сигнала в 6-м разряде. Запомненныйсигнал в 6 -м разряде совпадает с сиг13 732864 тат сложения5 Сложное законченоСокрашение времени сложения и повышение быстродействия сумматора, а также повышение контролирующей способности сумматора могут быть достигнуты, если дополнительно к известным операци ям образования промежуточной суммы в -м разряде и образования переноса из В-го в ( С -1)-й и ( 0 -2)- разряды ввести операцию образования сигнала промежуточной сверхсуммы в о -м разряде, 15 операцию образования сверхпереноса из 6-го в ( 1 -1)-й и ( б)-й разряды, операцию образования запомненного сигнала и операцию образования сигнала контроля сложения. 20В предлагаемом сумматоре кодов фибоначчи в каждом разряде ( 1-м) анализируются семь сигналов: сигналы в о-м разряде слагаемых, сигналы переносов иэ (+1 )д д и(8+2)-горазрядов в 6 й разряд, сигьЗ налы сверхпереносов иэ ( 6+1)-го и ( В+ +2)-го разрядов в 6-й разряд и сигнал промежуточной сверхсуммы из ( Ю)-го разряда; при этом в каждом разряде вы 30 полняются одновременно шесть операций:а) операция образования сигнала промежуточной суммы в 6 -м разряде, которая совпадает с аналогичной операцией в известном способе и состоит в следую 35 шем; сигнал промежуточной суммы принимают равным 1, если равен 1 хотя бы один из сигналов в-м разряде слагаемых, или сигнал переноса иэ-го разряда, и нулю в противном случае;б) операция образования перекоса иэ ( 6+1)-го в ( 6-1)-й и ( К -2)-й разряды, которая совпадает с аналогичной операцией в известном способе и состоит в следующем: сигнал переноса из 6 -го разряда принимают равным 1, если равны 1 одновременно оба сигнала в о-м разряде слагаемых, и нулю в противном случае;в) операция образования сигнала промежуточной сверхсуммы в 1-м разряде; сигнал промежуточной сверхсуммы принимают равным 1, если равен 1 хотя бы один из следующих сигналов; сигнал промежуточной суммы В 6 м раэрядеэ сиг 55 нал переноса из ( 6+2)-го разряда, сигнал сверхпереноса из ( 6+1)-го либо из ( +2)-го разряда, и нулю в противном случае; сигналы переносов иэ соответствующихразрядов 1 1 1 1 1 1 1 О 1 О 1 О О - промежуточная сумма1 1сигналы переносов из (6+2)-го разряда,101010 1101 О 1 О 1 0 О 0 - резуль 14г) операция образования сигнала сверхпереноса иэ 8 -го разряда в ( 6-1)-Йи ( 6-2)-й разряды: сигнал сверхперенсса из , -го разряда принима.от равным 1,если равен нулю сигнал промежуточной суммы в ( 8-1)-м разряде и одновременноравен единице хотя бы один иэ сигналовпереноса или сверхпереноса из ( 6 +2)-горазряда в-й разряд, и нулю в противном случае;д) операция образования запомненногосигнала в 6-м разряде: запомненныйсигнал в 6-м разряде принимают равным1; если одновременно равны 1 следующиесигналы: сигнал промежуточной суммы в( -1)-м разряде, хотя бы один из сигналов в 6 -м разряде слагаемых и хотябы один иэ сигналов переноса и сверхпереноса из 6 +2-го разряда и нулю в противном случае;е) операция образования сигнала контроля; сигнал контроля принимают равным1 (сигнал ошибки), если равен 1 сигналпереноса из ( 1+1)-го разряда и одновременно равен 1 хотя бы один из следующих сигналов: сигнал в 0 -м разрядепервого слагаемого, сигнал в 0 -м разряде второго слагаемого, сигнал переносаиз ( 8+2 )-го разряда, сигнал сверхпереноса из ( 6+1)-го разряда, сигнал сверхпереноса из ( 6+2)-го разряда, либо равен 1 сигнал сверхпереноса из б -горазряда и одновременно равен 1 хотя быодин из следующих сигналов: сигнал переноса иэ 6-го разряда, сигнал промежуточной суммы в ( С)-м разряде, запомненный сигнал в 6 -м разряде,С учетом введенных операций образование промежуточной сверхсуммы и задомненных сигналов приведены в примере 2,П р и м е р 2, Образовать промежуточную сверхсумму и запомненные сигна лы при сложении следуюших 1-кодов фибоначчи: 1211 1098765432 10-номера разрядов 1 0 10100010100 1 0 10101010000Так как сигналы промежуточной суммы в 0-м и 7-м разрядах равны 1 и одновременно равны 1 сигналы в 10-м и 8-м разрядах промежуточной суммы, то в 10-м и 8-м разрядах образуют запомненные сигналы,Так как сигнал промежуточной суммы ,в 5-м разряде равен нулю, то это приводит к образованию сигнала сверхпереноса из 6-го разряда, а затем из 4-го и 2-го 1 О разрядов:1111111010100сигналы сверхперено ов В результате образуется следующая промежуточная сверхсумма и запомненные сигналы:1 1 1 1 1 1 1 1 1 1 1 1 1 - промежуточная сверхсуммазапомненныесигналыЕсли равен 1 сигнал переноса из ( В+ +1)-го разряда, то это означает, что в ( 8 +1)-м разряде слагаемых имеются единичные сигналы, отсюда вытекает, что в ( 6+2)-м и 6-м разрядах слагаемых заведомо должны быть нули (свойство нормальной формы кодов фибоначчи), т,е, ЗО имеет место следующая ситуация:Е+2 8+1еЕФФвеЕе0 1 00 1 0перенос из (6 +1)-го разряда. Следовательно, при единичном сигнале переноса из ( 6+1)-го разряда сигналы в 3-м разряде слагаемых должны быть нулевыми (первое контрольное соотношение), 4 О Должен быть нулевым также сигнал переноса из (6+2)-го разряда (второе контрольное соотношение), Далее, сигнал переноса из ( 6+1)-го разряда приводит к появлению единичного сигнала в 6-м раз 45 ряде промежуточной суммы, что автоматически исключает появление сигнала сверх- переноса из ( 6+1)-го разряда (третье контрольное соотношение). Единичный сигнал сверхпереноса из ( 6+2)-го разряда также не может появиться, так как равен 1 сигнал в ( 6+1)-м разряде дромежуточной суммы (четвертое контрольное соот ношение),Если равен 1 сигнал сверхпереноса из 6-го разряда, то исключает появление единичного сигнала промежуточной суммы в ( 6-1)-м разряде (пятое контрольное соотношение), а также запомненного сиг 1 1 0 1 1 1 0 1 1 0 1 1 1 0 ФзФ з Ф 1 а 3 10 0100110010010 10010 10000 100 10 В сумматоре крдов фибоначчи операция нормализации ведется с учетом значений запомненных сигналов в соответствующих разрядах и состоит в следующем: если в процессе нормализации возникает необходимость замены нуля в 6-м разряде и единиц в ( (;-1)-м и ( 1 -2)-м разряде своими отрицаниями, а запомненный сигнал либо в ( б)-м, либо в ( б)-м разряде равен 1, то в процессе нормализации единицу сохраняют в разряде с единичным запомненным сигналом, а запомненный единичный сигнал заменяют на нулевой.Проведем нормализацию промежуточной сверхсуммы и запомненных сигналов в рассмотренном выше примере; 1 11) 1111111111111 Л 2) 10011111111111 3) 10010111111111Ф 1 1001 1 1011 11 111 1 О 1 О О 1 1 О О 1 1 1 1 1 1 0 1 0 1 0 0 0 0 1 0 1 1 1 4) 6) нала в ь-м разряде, который может появиться только при единичном сигнале промежуточной суммы в ( 1-1)-м разряде(шестое контрольное соотношение) и, нар Уконец, появление единичного сигнала переноса из 0-го разряда, который сразу жевызывает появление единичного сигналапромежуточной суммы в ( 0-1)-м разряде и запрет сигнала сверхпереноса из Я-горазряда (седьмое контрольное соотношение),Таким образом, вместо одного контрольного соотношения в известном сумматоре кодов фибоначчи в данном сумматоре введено 7 контрольных соотношений,которые и приводят к достижению второйцели изобретения - повышению контролирующей способности сумматора,Известная операция нормализации кодафибоначчи не учитывает запомненныесигналы и состоит, например в следующем:17 7328647) 10101000101001ди О О 1 0 О 1 1 0 Е+2 Е+1 Е 0 0 8) 10101000101010 -резульат сложения Работа сумматора кодов фибоначчи5протекает следующим образом.Сигналы на входах слагаемых 1 и 2появляются одновременно с сигналом навходе 7 начала сложения, При этом начи 1 Онается процесс формирования сигнала вмногоразрядном попусумматоре 3 (какбудет показано ниже, сигнал переноса вполусумматоре распространяется от старших разрядов к младшим). Блок 8 перезаписи информации представляет собой линию задержки с отводами в каждом разряде. Сигнал в блоке 8 перезаписи информации также распространяется от старшихразрядов к.младшим и, начиная со старших разрядов, последовательно переписывает информацию с полусумматора 3 внормалиэатор 12. Сигнал в нормалиэаторе 12 распространяется в направлении отмладших разрядов к старшим, Поэтомунормализация старших разрядов начинается раньше, чем закончился переходнойпроцесс в полусумматоре 3. За счет параллельной организации работы полусумматора 3 и нормализатора 12 удается всреднем повысить быстродействие сумматора, Появление сигнала на выходе 11свидетельствует об окончании процессаперезаписи информации, Если хотя бы наодном из выходов 6 или 15 появляетсясигнал ошибки, то через элемент ИЛИ 16он поступает на контрольный выход 17сумматора, После появления сигнала навыходе 11 и, после окончания переходногопроцесса в нормализаторе 12 на выходе 4 О14 появляется сигнал окончания сложения,разрешающий считывание информации ссумматора. Наличие сигнала окончаниясложения также приводит к повышению всреднем быстродействия сумматора,45Работу многоразрядного полусумматора3 удобнее объяснить, если ввести как быдва этапа обработки информации в одноразрядном полусумматоре; этап образования промежуточной суммы (выход 31) ипереноса (выход 23) и этап образованияпромежуточной сверхсуммы (выход 19),сверхпереноса (выход 22) и запомненного сигнала в Е -м разряде (выход 20).На первом этапе сигналы могут появляться только на входах 26, 27, 28 и29, Если хотя бы на одном из входов 26,27 и 29 появляется единичный сигнал,то через элементы ИЛИ 36 34 это привот к появлению сигнала на выходе 31,а через элемент ИЛИ 44 - на выходе 19,Если единичный сигпал появляется на входе 28, то через элементы ИЛИ 36 и 44это приводит к появлению сигнала на выходе 19. Если на входах 27 и 26 одновременно появляются единичные сигналы,то через элемент И 37 это приводит кпоявлению сигнала на выходе 23,Первый этап обработки информации вполусумматоре хорошо, контролируется,При сложении нормальных 1-кодов фибоначчи из 16 кодовых комбинаций на входах 26, 27, 28 и 29 семь кодовых комбинаций являются эапрешенными, а именно: 28 26 27 29 - входы О 0 0 О, О 0 0 1 О 0 1 1 - запрет О1 О 1 - запрет 0 1 1,1 - запрет1 0 0 01 0 0 1 - запрет1 0 1 01 0 1 1 - запрет1 1 0 О1 1 0 1 - запрет1 1 1 01 1 1 1 - запрет Появление единичного сигнала переноса иэ ( И +1)-го разряда (вход 29) означает, что в ( 8+1)-м разряде слагаемых находятся единицы и, следовательно, в (4+2)-м и Е-м разрядах слагаемых заведомо должны быть нули: 11ЬпереносСледовательно наличие переноса из (8+1)-го разряда и наличие хотя бы одной единицы на входах 26, 27 и 28 является признаком ошибки.В схеме одноразрядного полусумматора 18 эта идея контроля полусумматора на первом этапе обработки информации

СмотретьЗаявка

2432391, 22.12.1976

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

СТАХОВ АЛЕКСЕЙ ПЕТРОВИЧ

МПК / Метки

МПК: G06F 7/385

Метки: кодов, сумматор, фибоначчи

Опубликовано: 05.05.1980

Код ссылки

<a href="https://patents.su/18-732864-summator-kodov-fibonachchi.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор кодов фибоначчи</a>

Предыдущий патент: Устройство для извлечения квадратного корня

Следующий патент: Устройство для деления

Случайный патент: Режущая пластина